Digital Equipment Corporation Maynard, Massachusetts

Maintenance Manual Volume 1

# **RK8 DISK SYSTEM**

DEC-00-HRKB-D

# RK8 DISK SYSTEM MAINTENANCE MANUAL

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

1st Edition December 1970 2nd Edition October 1971

Copyright © 1970, 1971 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

#### CONTENTS

#### Page

.

#### CHAPTER 1 GENERAL INFORMATION

| 1.1 | Performance Specifications | 1-2 |

|-----|----------------------------|-----|

|-----|----------------------------|-----|

#### CHAPTER 2 DESCRIPTION

| 2.1    | Physical                                  | 2-1  |

|--------|-------------------------------------------|------|

| 2.2    | Disk Cabinet                              | 2-2  |

| 2.3    | Recording Disk Cartridge                  | 2-3  |

| 2.4    | Disk Read/Write Heads                     | 2-4  |

| 2.5    | Disk Drive Assembly                       | 2-5  |

| 2.6    | RK08 Disk Control Logic                   | 2-6  |

| 2.7    | Double-Frequency Recording                | 2-7  |

| 2.7.1  | Clock Frequency                           | 2-7  |

| 2.7.2  | Double-Frequency Recording                | 2-8  |

| 2.7.3  | Write Operation                           | 2-8  |

| 2.7.4  | Read Operation                            | 2-8  |

| 2.8    | Operator Control and Indicator Lights     | 2-8  |

| 2.9    | Disk Drive Power Supply                   | 2-10 |

| 2.10   | Disk Drive Power Interlock and Sequencing | 2-11 |

| 2.10.1 | ON Sequence                               | 2-11 |

| 2.10.2 | General Reset                             | 2-11 |

| 2.10.3 | Low Voltage                               | 2-11 |

| 2.10.4 | Interlock                                 | 2-11 |

| 2.10.5 | +24 Vdc Control Voltage                   | 2-11 |

| 2.10.6 | Indicator Lamp Outputs                    | 2-11 |

|        |                                           |      |

#### CHAPTER 3 INSTALLATION AND OPERATION

| 3.1 | Installation                  | 3-1 |

|-----|-------------------------------|-----|

| 3.2 | Inspection                    | 3-1 |

| 3.3 | Cabinet Installation          | 3-1 |

| 3.4 | Protective Coverings          | 3-2 |

| 3.5 | Primary AC Power Cables       | 3-2 |

| 3.6 | AC Power Check-Out Procedures | 3-3 |

| 3.7 | Operation                     | 3-5 |

|       |                                         | Page         |

|-------|-----------------------------------------|--------------|

| 3.7.1 | Sequencing                              | 3 <b>-</b> 5 |

| 3.7.2 | Disk Cartridge Insertion                | 3-9          |

| 3.7.3 | Disk Cartridge Removal                  | 3-9          |

| 3.7.4 | Disk Cartridge Handling                 | 3-10         |

| 3.7.5 | Storage and Shipping of Disk Cartridges | 3-11         |

#### CHAPTER 4 PROGRAMMING

| 4.1     | Disk Operation                    | 4-1  |

|---------|-----------------------------------|------|

| 4.2     | Programming                       | 4-2  |

| 4.3     | Format Description                | 4-2  |

| 4.3.1   | Sector Detail                     | 4-2  |

| 4.3.2   | Formatting a New Disk             | 4-7  |

| 4.3.3   | Effects of Errors on Data         | 4-7  |

| 4.3.3.1 | Control Busy Error                | 4-7  |

| 4.3.3.2 | Time Out Error Flag               | 4-7  |

| 4.3.3.3 | Parity or Timing Bit Error        | 4-7  |

| 4.3.3.4 | Data Rate Error                   | 4-8  |

| 4.3.3.5 | Track Add <b>ress</b> Error       | 4-8  |

| 4.3.3.6 | Sector No Good Error              | 4-8  |

| 4.3.3.7 | Track Capacity Exceeded Error     | 4-8  |

| 4.3.3.8 | Select Error                      | 4-8  |

| 4.3.4   | First Header Word                 | 4-9  |

| 4.3.5   | Second Header Word                | 4-9  |

| 4.3.6   | Accessing of Disk Sectors         | 4-10 |

| 4.3.7   | Control Description               | 4-10 |

| 4.3.8   | Multidisk Operations              | 4-11 |

| 4.4     | IOT Programming Instructions      | 4-11 |

| 4.5     | Detailed Programming Instructions | 4-15 |

#### CHAPTER 5 THEORY OF OPERATION

| 5.1   | RK01-X Disk Drive Interface | 5-1 |

|-------|-----------------------------|-----|

| 5.1.1 | Format Delays               | 5-1 |

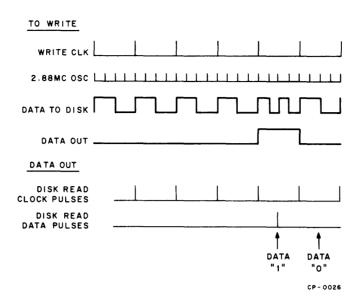

| 5.1.2 | Data to Disk                | 5-2 |

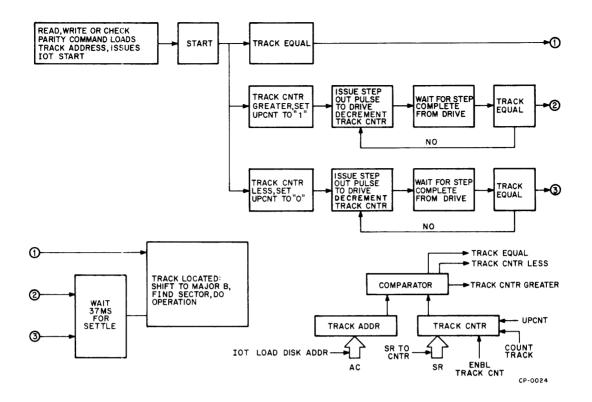

| 5.1.3 | Track Seek Mode             | 5-3 |

|          |                                            | Page        |

|----------|--------------------------------------------|-------------|

| 5.1.3.1  | Seek Track                                 | 5-3         |

| 5.1.3.2  | Find Track Zero                            | 5-5         |

| 5.1.3.3  | New Select                                 | 5-5         |

| 5.1.4    | Track Address, Counter, and Comparator     | 5-6         |

| 5.1.4.1  | Track Seek Mode                            | 5-6         |

| 5.1.4.2  | Formatted Disk                             | 5-7         |

| 5.1.4.3  | Enable Track Count                         | 5-7         |

| 5.1.4.4  | Reset Track/Sector Counter                 | 5-7         |

| 5.1.5    | Disk Selection                             | 5-7         |

| 5.1.6    | Cable Terminators                          | 5-8         |

| 5.2      | RK08 Disk Control                          | 5 <b>-9</b> |

| 5.2.1    | IOT Decoding                               | 5 <b>-9</b> |

| 5.2.2    | Skip and Break                             | 5-10        |

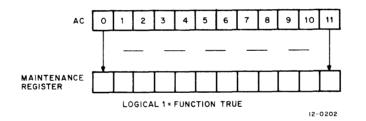

| 5.2.3    | Maintenance Register                       | 5-12        |

| 5.2.4    | Major Sequencer Register                   | 5-12        |

| 5.2.5    | R/W Command, Find Sector, and End Transfer | 5-13        |

| 5.2.6    | Read                                       | 5-15        |

| 5.2.6.1  | Parity Checking                            | 5-17        |

| 5.2.6.2  | Block End, Read Set Major J and K          | 5-18        |

| 5.2.7    | Write                                      | 5-18        |

| 5.2.8    | Data Buffers                               | 5-20        |

| 5.2.9    | Data Shift Register                        | 5-21        |

| 5.2.10   | Longitudinal Parity                        | 5-21        |

| 5.2.11   | Status Registers                           | 5-22        |

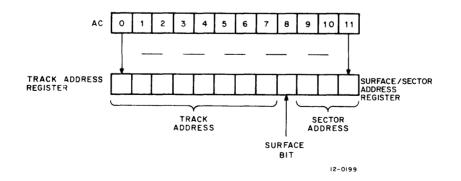

| 5.2.12   | Sector Addressing                          | 5-23        |

| 5.2.13   | Bit and Block Counter                      | 5-25        |

| 5.2.14   | Word Count and Current Address Registers   | 5-25        |

| 5.2.15   | AC Input Gating 00–11                      | 5-26        |

| 5.2.16   | AC and MB Inverters                        | 5-26        |

| 5.2.17   | Cable Terminators                          | 5-26        |

| 5.2.18   | Interconnecting Cables                     | 5-26        |

| 5.2.19   | 716 Power Supply                           | 5-26        |

| 5.2.20   | 854 Power Control Panel                    | 5-26        |

| 5.2.21   | Disk Drive Power Supply                    | 5-27        |

| 5.2.21.1 | Operation                                  | 5-27        |

|        |            | Page |

|--------|------------|------|

| 5.2.22 | New Select | 5-29 |

#### CHAPTER 6 MAINTENANCE

| 6.1    | General                               | 6-1  |

|--------|---------------------------------------|------|

| 6.2    | Maintenance Kit                       | 6-1  |

| 6.3    | Preventive Maintenance                | 6-2  |

| 6.3.1  | Functional Check for Head Alignment   | 6-2  |

| 6.3.2  | Visual Inspection                     | 6-2  |

| 6.3.3  | Head Damage                           | 6-2  |

| 6.3.4  | Audible "Tinging" or Scratching       | 6-3  |

| 6.3.5  | Scratches or Grooves Across the Head  | 6-3  |

| 6.3.6  | Oxide Deposits on Heads               | 6-3  |

| 6.3.7  | Disk Surface Scratches                | 6-4  |

| 6.3.8  | Cleaning Read/Write Heads             | 6-4  |

| 6.3.9  | Particle Damage to Disk Surface       | 6-4  |

| 6.3.10 | Particle Damage to Read/Write Head    | 6-5  |

| 6.3.11 | Nonparticle Damage                    | 6-5  |

| 6.3.12 | Electronic Circuitry                  | 6-5  |

| 6.3.13 | Cleanliness                           | 6-6  |

| 6.4    | RK01-X Modules                        | 6-6  |

| 6.5    | RK08 Logic Modules                    | 6-7  |

| 6.6    | Control Commands                      | 6-8  |

| 6.7    | CE PWB Switch Operation               | 6-10 |

| 6.8    | I/O Interface Cables and Terminations | 6-11 |

| 6.9    | Preventive Maintenance Schedule       | 6-12 |

| 6.10   | Read/Write Head Alignment             | 6-14 |

| 6.10.1 | Alignment Procedures                  | 6-14 |

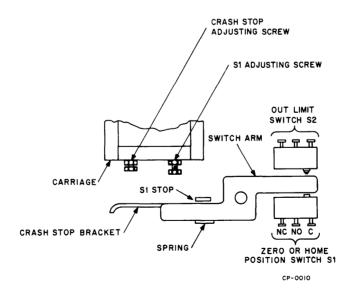

| 6.11   | Home Position Switch S1 Alignment     | 6-19 |

| 6.12   | Outer/Inner Limit Switches            | 6-21 |

| 6.12.1 | Outer Track Stop Switch               | 6-21 |

| 6.12.2 | Inner Track Stop Switch               | 6-22 |

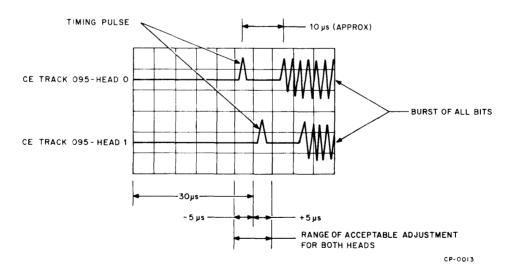

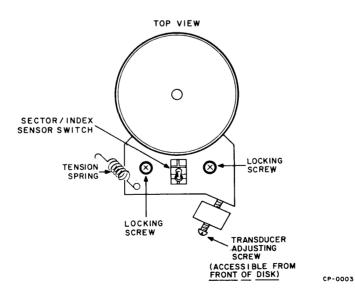

| 6.13   | Sector Transducer Alignment           | 6-23 |

| 6.13.1 | General                               | 6-23 |

| 6.13.2 | Procedures                            | 6-23 |

|        |                                       |      |

|        |                                     | Page |

|--------|-------------------------------------|------|

| 6.14   | Light Replacement                   | 6-26 |

| 6.14.1 | Replacing Register Indicator Lights | 6-26 |

| 6.14.2 | Replacement of Pushbutton Lights    | 6-26 |

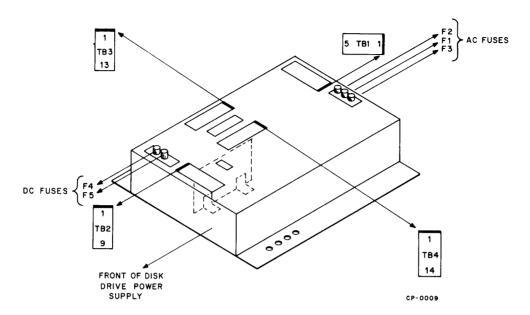

| 6.15   | Disk Drive Power Supply             | 6-26 |

| 6.16   | Signal Index                        | 6-27 |

| 6.17   | ad/dc Wiring                        | 6-28 |

|        | RK08 Signal Index                   | 6-29 |

|        | RK01 Signal Index                   | 6-38 |

#### ILLUSTRATIONS

| Figure No. | Title                                                             | Art No.  | Page          |

|------------|-------------------------------------------------------------------|----------|---------------|

| 1-1        | RK8 Disk System                                                   | 5103-2   | 1-1           |

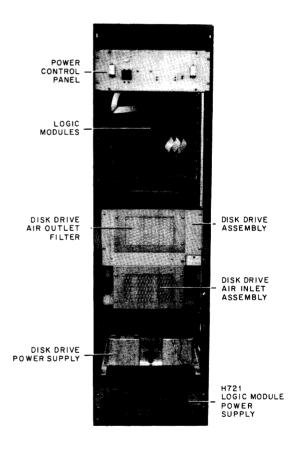

| 2-1        | Rear View of Cabinet Interior                                     | 5103-5   | 2-1           |

| 2-2        | Logic Mounting Panels with Logic Modules                          | 5103-4   | 2-2           |

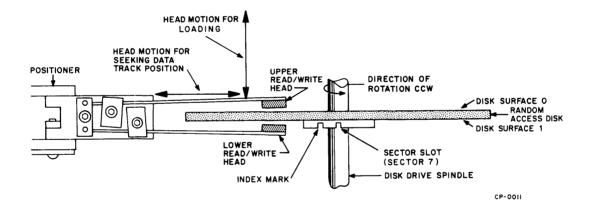

| 2-3        | Disk Assembly Diagram                                             | CP-0011  | 2-3           |

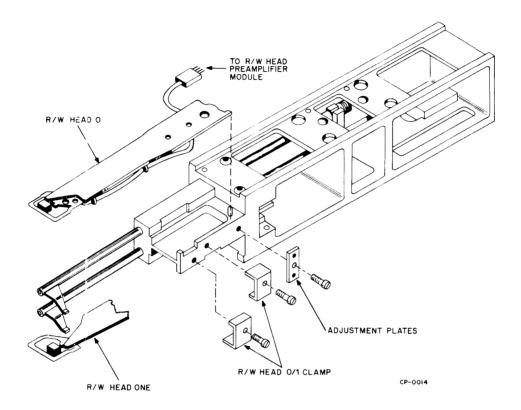

| 2-4        | Read/Write Carriage Assembly Diagram                              | CP-0014  | 2-4           |

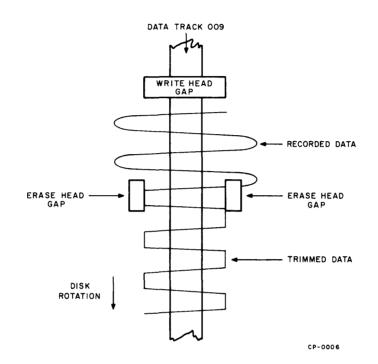

| 2-5        | Data Trimming Diagram                                             | CP-0006  | 2-5           |

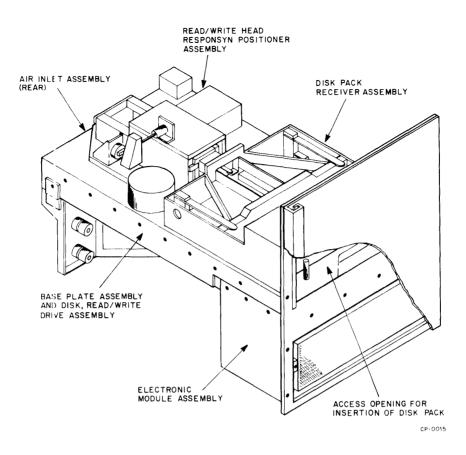

| 2-6        | Main Disk Drive Assembly Diagram                                  | CP-0015  | 2-6           |

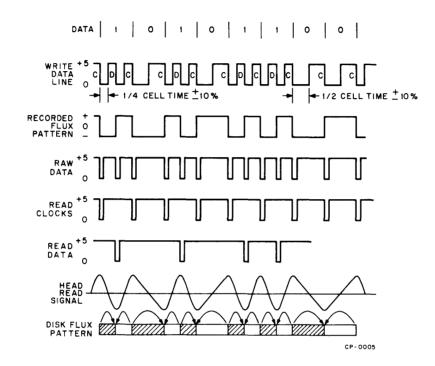

| 2-7        | Double—Frequency Recording Data In/Out<br>Relationship Diagram    | CP-0005  | 2-7           |

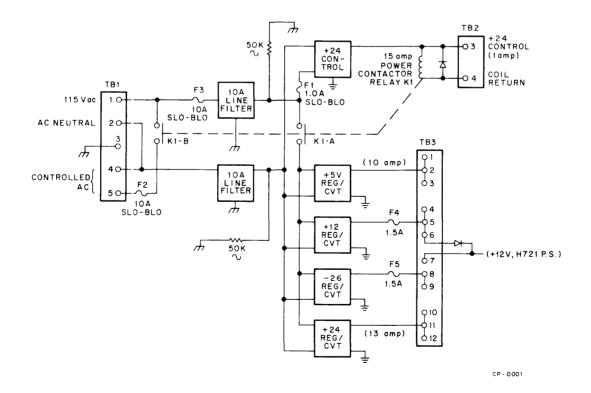

| 2-8        | Disk Drive Power Supply Block Diagram                             | CP-000 ] | 2-10          |

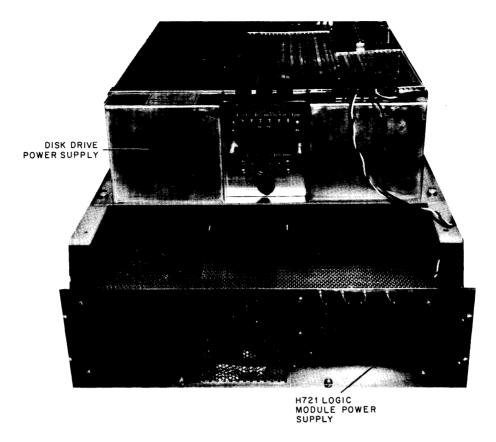

| 3-1        | Disk and Type H721 Power Supplies                                 | 5103-1   | 3-3           |

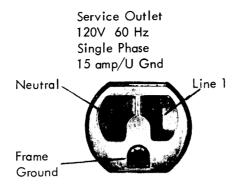

| 3-2        | Hubbell Wall Receptacle Connector Diagram                         |          | 3-4           |

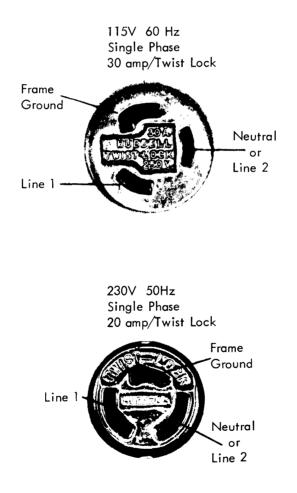

| 3-3        | Type H721 Power Supply Block Schematic Diagram<br>(D-BS-H721-0-1) |          | 3-7           |

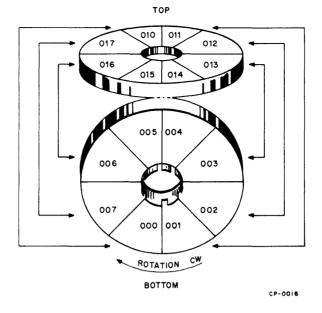

| 4-1        | Disk Surfaces 0 and 1 Diagram                                     | CP-0016  | 4–3           |

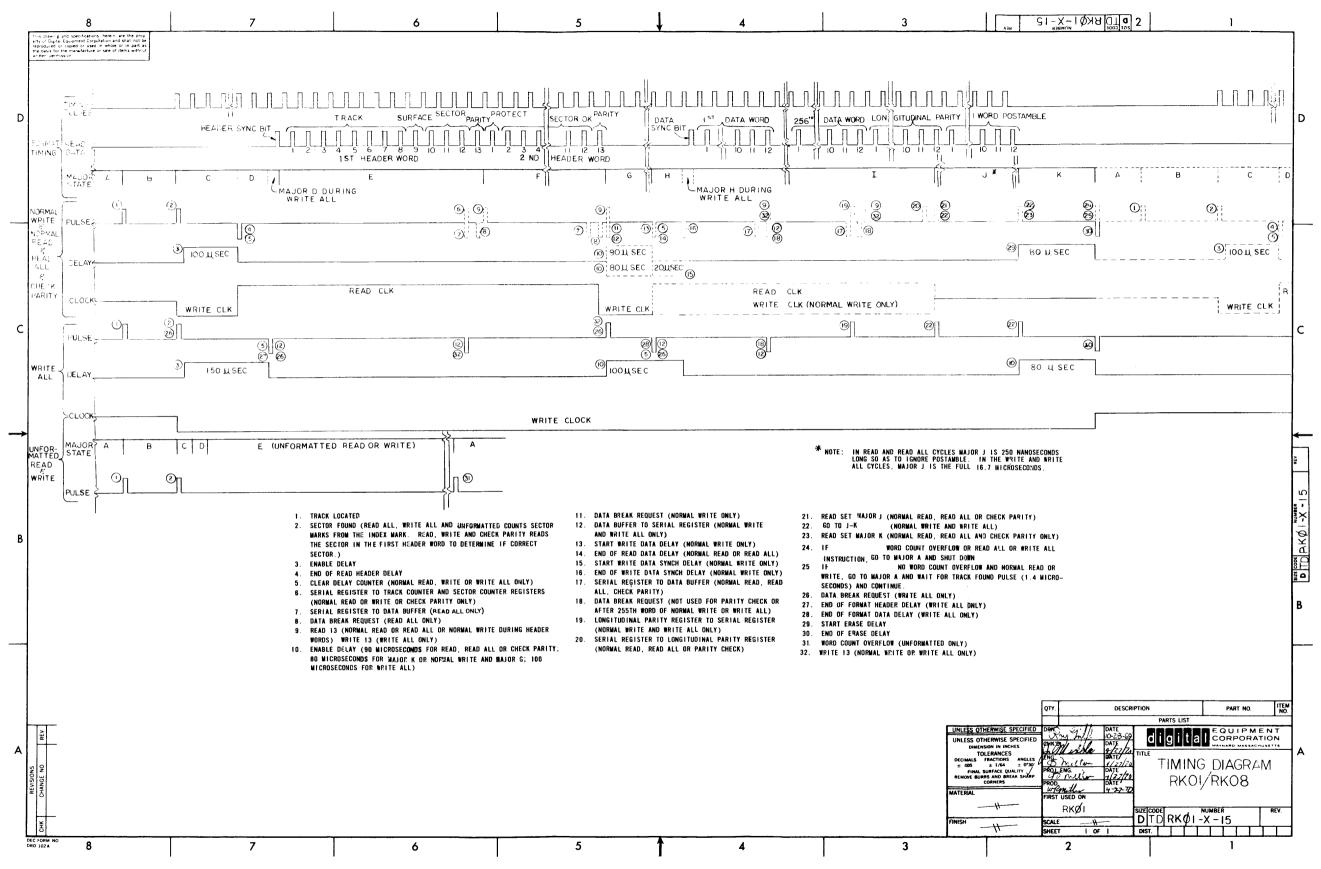

| 4-2        | Sector Timing Diagram (D-TD-RK01-X-15)                            |          | 4-5           |

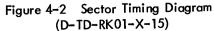

| 4-3        | DLDC Command Register Diagram                                     | 12-0203  | 4-13          |

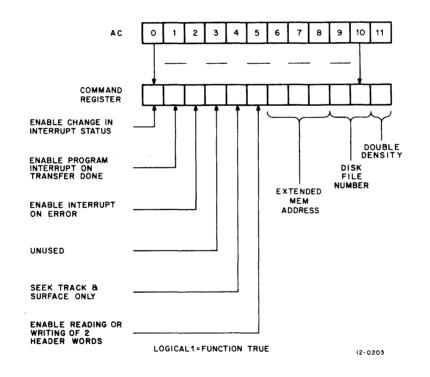

| 4-4        | DRDS Instruction Register Diagram                                 | 12-0201  | 4-14          |

| 4-5        | DMNT Instruction Register Diagram                                 | 12-0202  | 4-14          |

| 4-6        | Disk Address Register Diagram                                     | 12-0199  | 4-14          |

| 5-1        | Data to Disk Timing Diagram                                       | CP-0026  | 5-3           |

| 5-2        | Track Seek Mode                                                   | CP-0024  | 5-4           |

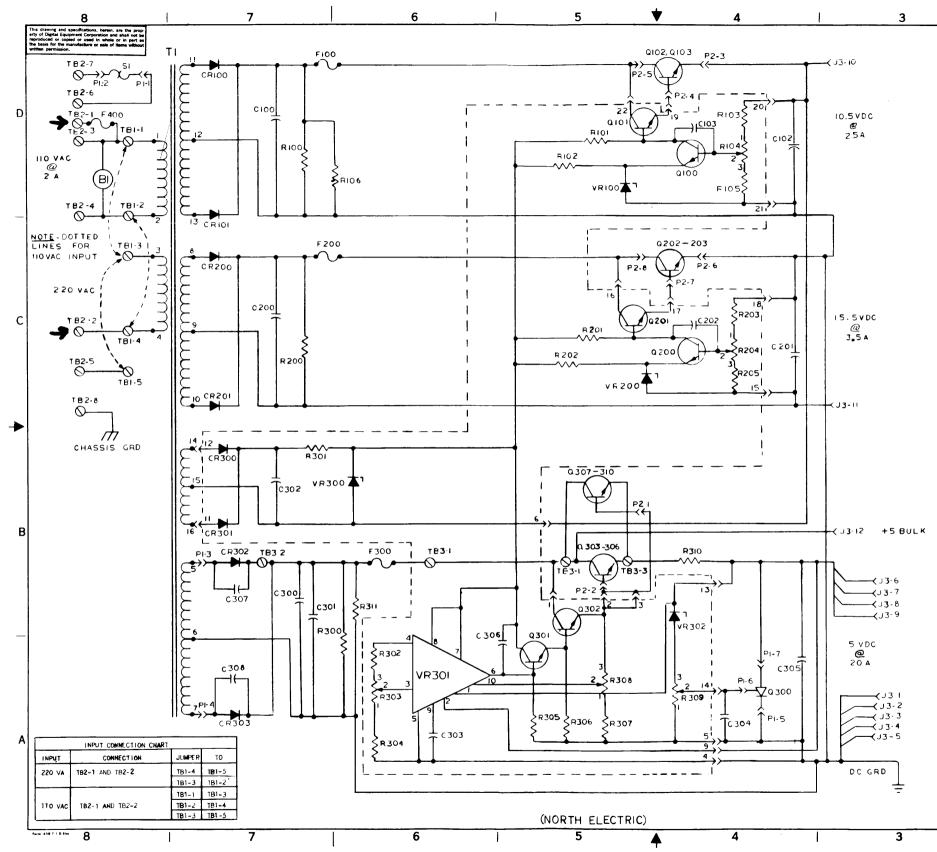

| 5-3        | Power Supply Schematic                                            | CP-0023  | 5 <b>-</b> 28 |

#### ILLUSTRATIONS (Cont)

| Figure No.   | Title                                                         | Art No. | Page          |

|--------------|---------------------------------------------------------------|---------|---------------|

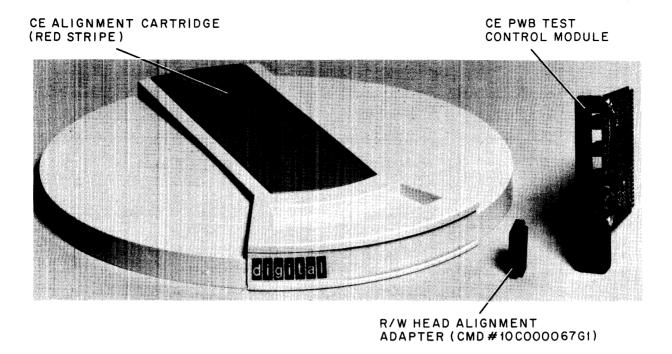

| 6-1          | Alignment Cartridge , Control Module and Alignment<br>Adapter | 5103-6  | 6-11          |

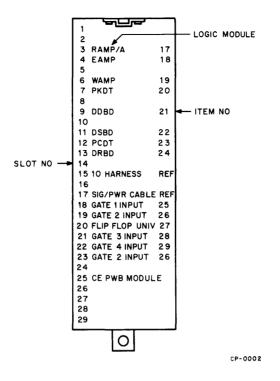

| 6-2          | Electronic Module Assembly Diagram                            | CP-0002 | 6-15          |

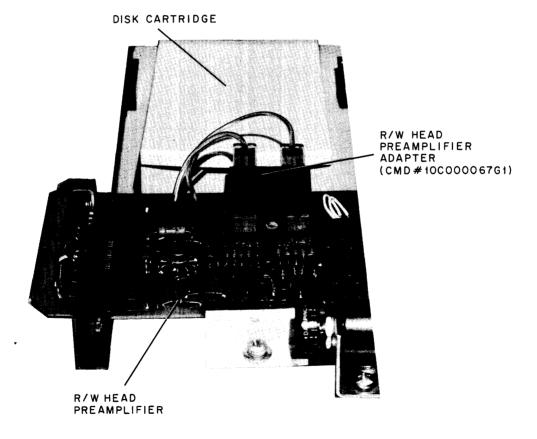

| 6-3          | Read,/Write Head Alignment Adapter                            | 5103-3  | 6-15          |

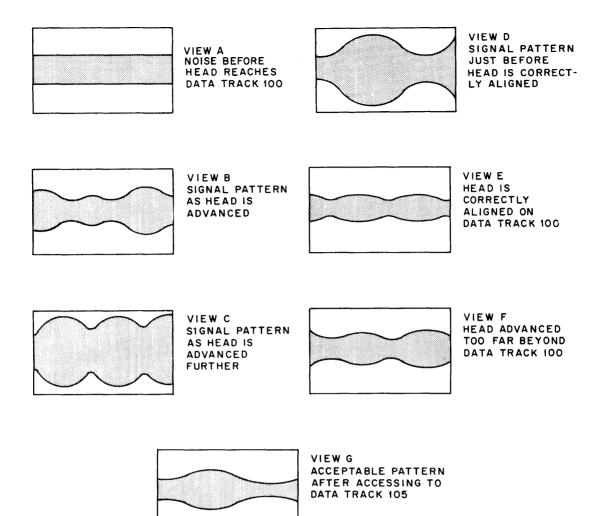

| 6-4          | Signal Patterns for Data Track 100 Alignment                  | CP-0027 | 6-17          |

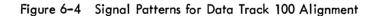

| 6 <b>-</b> 5 | Head Adjustment Diagram                                       | CP-0008 | 6-18          |

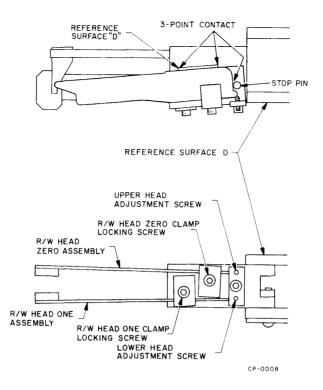

| 6-6          | R/W Head Stepping Motor Baseplate<br>Adjustment Diagram       | CP-0025 | 6-19          |

| 6-7          | Home Position and Inner/Outer Limit Switch Diagram            | CP-0010 | 6-19          |

| 6-8          | Sector Transducer Timing Diagram                              | CP-0013 | 6-24          |

| 6-9          | Sector Transducer Adjustment Diagram                          | CP-0003 | 6 <b>-2</b> 5 |

| 6-10         | Disk Drive Power Supply Fuse and TB location<br>Diagram       | CP-0009 | 6-27          |

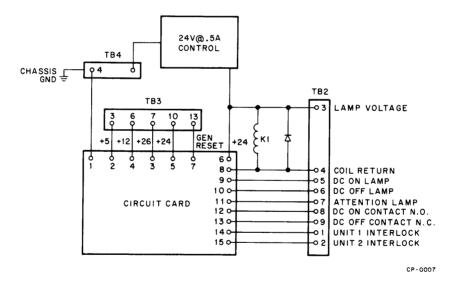

| 6-11         | Disk Drive Power Supply Circuit Card<br>Connection Diagram    | CP-0007 | 6 <b>-27</b>  |

#### TABLES

Page

#### 1-1 Specifications 1-2 2-1 2-9 Control Switch 2-2 Indicator Lights 2-9 2-3 2-9 **Control Panel Switches** 3-1 Power Cable Line Identification 3-2 3-2 Disk Cartridge Specifications 3-11 4-1 Sector Format Program 4-10 4-2 4-11 Sector Format Program 4-3 IOT Instructions 4-12 4-4 Detailed Programming Instructions 4-15 5-1 5-8 Control Signals to a Selected Disk Drive 5-2 Output Signals from a Selected Disk Drive 5-9 5-3 Error Flags 5-22 6-1 Maintenance Equipment 6-2 6-2 RK01-X Logic Modules 6-6 6-3 **RK08 Logic Modules** 6-7 6-4 Disk Input/Output Command Signals 6-8

Table

#### TABLES (Cont)

| Table |                                           | Page |

|-------|-------------------------------------------|------|

| 6-5   | CE PWB Switches                           | 6-10 |

| 6-6   | Termination Modules                       | 6-11 |

| 6-7   | Data Break I/O Cables to Computer         | 6-12 |

| 6-8   | I/O Bus Interface                         | 6-12 |

| 6-9   | Maintenance Schedule                      | 6-13 |

| 6-10  | Test Equipment                            | 6-14 |

| 6-11  | ac-dc Voltages Terminal Board Connections | 6-28 |

| 6-12  | CMD Module Replacement                    | 6-42 |

## Preface

The RK8 Disk operational and functional charactersitics are fully described in Volumes I and II of the associated Maintenance Manual. In Volume I all written data pertinent to the Disk is presented, and Volume II contains the RK8 Disk Engineering Drawing set showing the logic circuitry described in Chapter 5 of Volume I.

The drawings referenced in Chapter 5 of Volume I and the drawing identification in Volume II are prefixed by the Roman numeral II.

# Chapter 1 General Information

The RK8 Disk System is a movable read/write head, random-access, removable bulk storage, digital memory device designed for use with DEC PDP-8 family-of-computer systems (see Figure 1-1). The RK8 accepts up to four RK01 Disk Drives that can be added to the system in

831,488 word increments providing a total of 3,325,952 words of storage. One RK08/RK01 provides up to 831,488 words of storage (12 bits). The single-cycle data break facility allows transfers at a rate of 16.7 µs per word. The average access time is 240 ms with the disk read/write head (one per surface) at extreme disk track positions, or 134 ms when the disk head is at random disk track positions. Worst-case access timing is 443 ms. (The accessing times include settling time.)

The RK8 System has the following three features:

1.

- a. The RK08 Disk Control possesses many maintenance features useful in diagnostic program checking of registers, flags, and logic functions.

- b. The system uses the single-cycle data break facility and is designed to minimize programming effort.

- c. Delay networks, associated with data transfers, are derived from a crystal-controlled clock and give format stability over a wide range of environmental conditions.

Three basic functions of the disk are: normal read or normal write for accessing data, a read-all or write-all for formatting and accessing the header word, and a parity check that reads data without transferring it to the computer.

#### NOTE

All drawings referenced in Chapter 5 are contained in Volume II of this Maintenance Manual.

Figure 1-1 RK8 Disk System

#### 1.1 PERFORMANCE SPECIFICATIONS

Table 1-1 provides electrical, environmental, physical, and mechanical specifications for the RK8 Disk Drive System.

| Charac teristic      | Specification                                                                                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Power     | 115/230 ±10 Vac, 50/60 ±1/2 Hz at 1.5A 150W<br>(510 Btu) for the RK08 Control and 6.1A, 700W<br>(2380 Btu) or 8.7A (surge current), 1000W (3450<br>Btu) for each RK01 Disk Drive. |

| Disk Logic Voltage   | +24 ±2 Vdc, -5A minimum, 6.0A maximum aver-<br>age with a 15A peak.<br>+12 Vdc ±5% at 200 mA<br>-26 Vdc ±5% at 200 mA<br>+5 Vdc ±5% at 1.0A.                                      |

| Disk Capacity        |                                                                                                                                                                                   |

| Storage Capacity     | Each RK01 Disk Cartridge stores 831,488 (in-<br>cludes 3 spare tracks) 12-bit words.                                                                                              |

| Expansion            | Four RK01 Disk Drives can be controlled by one<br>RK08 Control for a total of 3,325,952 words.                                                                                    |

| Data Tracks          | 200 (plus 3 spare tracks)                                                                                                                                                         |

| Words per Track      | 4096 (2048 words on 0 and 1 surfaces)                                                                                                                                             |

| Sectors              | 16 (eight sectors per side)                                                                                                                                                       |

| Words per Sector     | 256                                                                                                                                                                               |

| Minimum Block Size   | 256                                                                                                                                                                               |

| Maximum Block Size   | 4096 _                                                                                                                                                                            |

| Read/Write Heads     |                                                                                                                                                                                   |

| Туре                 | Tunnel erase                                                                                                                                                                      |

| Number               | 2 (one per disk surface)                                                                                                                                                          |

| Recording Parameters |                                                                                                                                                                                   |

| Recording Method     | Double Frequency – Time plus data                                                                                                                                                 |

| Densi ty             | 704 bits/inch (outer track 000)<br>1026 bits/inch (inner track 203)                                                                                                               |

| Speed                | 1500 ±30 rpm                                                                                                                                                                      |

| Transfer Path        | Single-cycle Data Break                                                                                                                                                           |

| Transfer Rate        | 16.7 μs per word                                                                                                                                                                  |

| Tabl | e | 1. | -1  |

|------|---|----|-----|

| Tabi | e | 1. | - 1 |

#### Specifications

#### Table 1–1 (Cont) Specifications

| Characteristic              | Specification                                                                                                                                                                         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Recording Parameters (Cont) |                                                                                                                                                                                       |

| Minimum Access Time         | 2.0 ms step , plus 37 ms settle time (Adjacent<br>Tracks)                                                                                                                             |

| Average Access              | 134 ms (includes settle time)                                                                                                                                                         |

| Maximum Access              | 441 ms (includes settle time)                                                                                                                                                         |

| Latency Maximum             | 40 ms (1 revolution)                                                                                                                                                                  |

| Latency Average             | 20 ms $(1/2 revolution)$                                                                                                                                                              |

| Program Interrupts          | Transfer Done Flag (Enabled Separately)<br>Error Flag (Enabled Separately)                                                                                                            |

| Write Lock                  | A programmable header word allows sector write lock . A pushbutton allows total disk write lock .                                                                                     |

| Environmental Conditions    |                                                                                                                                                                                       |

| Operating Temperature       | +65°F (+15°C) to +90°F (+32°C)<br>20°F per hour cycle rate.                                                                                                                           |

| Storage Temperature         | +20°F (-7°C) to +165°F (74°C) for a period of six months when packaged for storage and shipment.                                                                                      |

| Operating Humidity          | 20% to 80%, excluding all conditions that would cause moisture to condense in or on the equipment.                                                                                    |

| Storage and Shipping        |                                                                                                                                                                                       |

| Humidity                    | Range: minimum 5%, maximum 95% up to 100°F.<br>No condensation, resulting in moisture in or on<br>the equipment, is tolerable.                                                        |

| Mechanical                  |                                                                                                                                                                                       |

| Cabinets                    | One cabinet can accommodate one RK08 Control<br>and one RK01 Disk Drive (an RK8 System), a<br>second cabinet houses two RK01 units, and a third<br>cabinet houses a fourth RK01 unit. |

| Physical                    |                                                                                                                                                                                       |

| Mechanical Package          | One standard DEC cabinet accommodates the RK8<br>System, a second cabinet houses two RK01 units<br>and a third cabinet houses a fourth RK01 unit.                                     |

| Weight                      | 500 lb uncrated (RK8)<br>590 lb crated<br>Additional RK01 130 lb                                                                                                                      |

# Chapter 2 Description

#### 2.1 PHYSICAL

The disk, its associated logic circuitry, the two power supplies, and the control and registry indicator panel are mounted in a free-standing, 19-in. wide H950 Cabinet (see Figures 1-1 and 2-1).

The STATUS, COMMAND, DATA, DISK ADDR (Disk Address), MAJOR STATES, BRK RQ (Break Request), BREAK, WRITE, and WCOV (word count overflow) indicator lamps are located on the upper front section of the cabinet. When lit, these lamps reflect the status of the registers.

Three RK08/RK01 logic mounting panels are located (behind two dress panels) directly below the indicator panel (see Figure 2-2). Removal of these panels exposes the logic mounting panel module connector pins.

A control panel consisting of the DISK LOCKOUT 0, 1, 2, and 3, the SECT PROT (Sector Protect), and the ATTN-OFF-ON (Attention-Off-On) pushbutton switches is located below the three dress panels; the Disk START/STOP switch and SAFE lamp are located on the disk control panel below the access door. The function of each switch is outlined in Table 4-7.

Figure 2-1 Rear View of Cabinet Interior

The front door of the disk drive unit is a removable

panel allowing access to the disk logic mounting panel module pins. The power supply voltage terminations are accessible by removing the dress panel (second from the bottom of the cabinet). All

Figure 2-2 Logic Mounting Panels with Logic Modules

voltages are separately fused. The +5 and -15 Vac and ground connections for the three module mounting panels are on the left interior of the cabinet and each connection is identified.

#### 2.2 DISK CABINET

The H950 Disk Cabinet is equipped with roll-around casters and permanent leveling feet. Although either can be used for installation purposes, it is recommended that the disk cabinet be mounted on the leveling feet.

#### NOTE

The disk air intake opening, located in the rear of the cabinet, must not be obstructed during installation; this is the air intake facility for the disk cartridge.

#### 2.3 RECORDING DISK CARTRIDGE

The recording medium for the RK08 Disk is a removable disk cartridge which houses an aluminum, oxide-coated platter that rotates counterclockwise, when viewed from the top, when inserted into the disk drive assembly.

The unformatted storage capacity of a single disk is 1,929,000 6-bit characters. There are two recording surfaces per disk, the top designated side 0 and the other side 1. There are 203 data tracks per surface which are numbered, starting from the outer edge of the disk, from data track 000 to the center of the disk and track 202 (see Figure 4-1). The disk drive mechanism permits the interchanging of disk cartridges, the procedures for this operation are outlined in Chapter 3.

The disk cartridge is a semipermanently encased unit with an access door for entry of the read/write heads; the disk cartridge also contains an air valve on the bottom of the disk pack which allows filtered air to enter the cartridge. The pressurized air performs a two-fold function: 1) it keeps the disk aluminum platter operating at the required ambient conditions, and 2) it keeps foreign particles from entering the disk cartridge read/write head access door. When the disk cartridge is inserted into the disk, the read/write head access door is automatically opened by an interior spring arm that allows the aluminum platter to be positioned between the read/write heads (see Figure 2-3).

Figure 2-3 Disk Assembly Diagram

The disk cartridge is accurately positioned on the disk's internal mechanical drive spindle and is held in position until the disk cartridge activates an internal switch that issues a status level permitting the drive motor to turn on and bring the disk up to speed.

#### 2.4 DISK READ/WRITE HEADS

Data is recorded on and retrieved from the disk by upper and lower read/write heads (see Figure 2-4) which "fly" between 125 and 160 microinches from the disk recording surfaces on a self-generated film of air. The heads shown in Figure 2-5 consist of: a split erase element located behind the read/write gap, and the erase coil connected in series with the center tap of the read/write coil.

Figure 2-4 Read/Write Carriage Assembly Diagram

The disk surface velocity generates the film of air which supports the heads. The heads are not lowered onto the disk surface until the disk is close to or at its normal operating speed of 1500 rpm.

A CS circuit monitors all dc voltages, disk speed, and other disk parameters; if unsafe conditions exist, the heads are automatically retracted.

The read/write heads are mounted on two movable assemblies, one gliding over disk 0 surface and the other over disk 1 surface (see Figures 2-3 and 2-4).

#### NOTE

Heads must not be loaded manually when the disk cartridge has been removed from the disk receiver, when the disk has stopped rotating, or when the disk logic air blower is not operational. Heads can be loaded under static conditions only if a folded piece of Hollerith card is inserted between the upper and lower heads giving protection to the gliding surfaces. When reading/writing information from or onto the disk, the information is trimmed in width by the split erase head (see Figure 2-5). The difference in the recorded and the erased trimmed track compensates for mechanical tolerances in the head positioning mechanism and provides protection for data recorded on adjacent data tracks. For example, if the data on track 009 was not trimmed, the read head would read the data on track 009 in addition to partial data on track 010. The erase function occurs approximately 40 µs after the recording of data.

Figure 2-5 Data Trimming Diagram

#### 2.5 DISK DRIVE ASSEMBLY

The main disk drive assembly (see Figure 2-6) is a 19-in. wide, 19-3/8-in. high, and 30-in. deep unit consisting of the following separate components:

- a. The read/write head responsyn positioner assembly that accommodates the read/write magnetic head assemblies and their associated electronic control circuitry,

- b. The disk cartridge drive and associated spindle mechanism,

- c. The operator control panel with functional control indicators and the START/STOP switch,

- d. The logic and control circuitry for operation of the disk,

- e. A 10-ft I/O cable, and

- f. An air blower and associated filter.

Figure 2-6 Main Disk Drive Assembly Diagram

The air blower assembly of the disk is mounted in the lower rear portion of the disk assembly, the logic and control circuitry in the lower front portion of the disk assembly, the read/write head responsyn positioner assembly on the interior base-plate assembly, and the functional control panel in the upper front portion of the disk.

#### 2.6 RK08 DISK CONTROL LOGIC

The disk control circuitry is divided into a series of functions, each of which is controlled by the major state shift register. The functions, which are divided into MAJOR states A through K by the shift register, are described as follows:

- a. Locate the data track,

- b. Sync off the sector pulse,

- c. Wait for the header words,

- d. Read the header words (2) of the sector addressed,

- e. Wait for the data words, and

- f. Transfer the data to or from the computer memory.

#### 2.7 DOUBLE-FREQUENCY RECORDING

Double-frequency recording, which is used in the RK08/RK01 Disk for recording and writing of data, provides an overall frequency of 1,440,000 bits/sec which includes the clock and data bits.

The reading and writing of data is performed by the read/write head which senses pattern changes in the head gap flux (see Figure 2-7).

Figure 2-7 Double-Frequency Recording Data In/Out Relationship Diagram

#### 2.7.1 Clock Frequency

The clock frequency signal is encoded in data pulses to produce a single composite signal at the read/ write head. This signal presents a 0- or 1-bit condition for each bit-cell time generated by the clock.

Single disk storage uses the double-frequency method of magnetic recording; a clock frequency is used in establishing the basic bit-cell timing cycle. The insertion of a data pulse between clock pulses in a bit-cell time period produces a composite read/write signal that uses only clock pulses for a 0-bit indication and data pulses plus clock pulses for a 1-bit indication.

A 0 bit-cell time (clock pulses only) produces a single change in direction of the flux pattern, and a 1 bit-cell time (a data pulse located between two clock pulses) produces a double change in the disk flux pattern direction. In either case, the clock signal generates a change in the direction of magnetic polarity from plus-to-minus or minus-to-plus, causing a bit to be stored. Because the clock and data information are synchronized on a composite signal, double-frequency recording is sometimes referred to as "self-clocking".

#### 2.7.2 Double-Frequency Recording

With double-frequency recording, a clock bit is always inserted at the beginning of each bit-cell time to establish the basic recording frequency. A data bit is inserted between clock bits at twice the frequency; consequently, the bit generates two disk flux reversals within a single bit-cell time. If the data bit is not present, a single disk flux reversal occurs in a bit-cell time.

The magnetic recording head, which contains a split-ring core with a coil winding, causes a magnetic field in a given flux direction to prevail at the ring gap while the coil is energized. When current flows through the coil, the flux induced in the ring establishes a fringe flux at the gap, and as the magnetic recording surfaces passes by the gap, the fringe flux magnetizes the disk surface.

#### 2.7.3 Write Operation

When writing data on the disk, a bit is recorded when the flux direction in the ring is reversed by switching between coils in the read/write head. The fringe flux is reversed in the gap and, therefore, the portion of the flux flowing through the recording medium is reversed.

If the flux reversal is instantaneous in relation to the motion of the recording surface and the gap is observed at the moment of reversal, the portion of the surface that has passed the gap is magnetized in one horizontal direction, while the portion directly under the gap is magnetized in the opposite direction. Between these two conditions the flux must reverse 180° which represents a bit.

#### 2.7.4 Read Operation

During the read operation, the gap passes over an area that is magnetized in one horizontal direction, and a constant flux flows through the ring and coil. There is no output voltage for this condition, however, when the recorded bit and the 180° horizontal flux reversal passes the gap, the flux flowing through the ring and coil reverses 180°. The coil senses the flux change and produces a voltage output pulse.

#### 2.8 OPERATOR CONTROL AND INDICATOR LIGHTS

The operational control and indicator lamps are readily accessible to the operator from the front of the disk. The function and purpose of each is described in Tables 2-1, 2-2 and 2-3.

#### Table 2–1 Control Switch

| Control    | Function                                                                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START/STOP | When placed in the START or up position, the disk start-<br>ing cycle is initiated only if the disk cartridge is in place<br>and the disk cartridge receiver handle is in the raised<br>position. When placed in the STOP or down position,<br>the disk STOP sequence is initiated. |

#### Table 2–2 Indicator Lights

| Light | Function                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAFE  | When illuminated, the disk cartridge access door inter-<br>lock is off, and it is safe for the operator to lower the<br>disk cartridge receiver handle for removal or insertion of<br>the disk cartridge. |

|       | The indicator lamp illuminates approximately 35 seconds after a STOP sequence has been initiated.                                                                                                         |

| READY | When illuminated, it is ready to begin communicating<br>with the central processor of the computer. The lamp il-<br>luminates approximately 90 seconds after the START se-<br>quence has been initiated.  |

#### Table 2–3 Control Panel Switches/Lights

| Switch           | Function                                                                                                                                                                                                                                                                                                       |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DISK LOCKOUT 1-4 | When depressed, the lamp illuminates indicating that the<br>disk associated with the pushbutton is locked out and data<br>cannot be written onto the disk platter. The panel con-<br>trols up to four disks.                                                                                                   |  |

| ATTN             | When illuminated (red), the lamp indicates that the disk<br>power supply has a malfunction. Pushing the STOP<br>switch resets the power supply.                                                                                                                                                                |  |

|                  | NOTE<br>This lamp is also illuminated after turning system<br>power off with the computer on-off switch. Push-<br>ing this lamp switch resets the power supply. This<br>interlocking action protects the data on the disk<br>from spurious write signals while computer and<br>disk controls are powered down. |  |

#### Table 2-3 (Cont) Control Panel Switches

| Switch                 | Function                                                                                                                                                                          |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ON<br>Off<br>Sect prot | When ON, power is applied to the disk.<br>When OFF, power is removed from the disk.<br>Prevents writing on protected sectors, as specified by bit<br>0 of the second header word. |  |

#### 2.9 DISK DRIVE POWER SUPPLY

The disk drive power supply operates from a 115 Vac, 60 Hz primary power source which is controlled by a 15A power contactor relay K1. The 115 Vac input line and the ac neutral line are filtered by two 10A line filters (see Figure 2-8). The dc output voltages are terminated on connectors TB1, -2, -3, and -4, with the dc voltage common lines connected to chassis ground TB4 (see Figure 6-13). The dc outputs are capable of driving up to two disk drives, and both ac and dc lines are fuse-protected.

All terminal boards are mounted on the exterior of the power supply and are protected with an insulated cover to prevent accidental contact with live voltages or damage to the power supply.

Figure 2-8 Disk Drive Power Supply Block Diagram

#### 2.10 DISK DRIVE POWER INTERLOCK AND SEQUENCING

The interlock and sequencing of events which take place in the disk drive power supply are presented in the following sections.

#### 2.10.1 ON Sequence

The ON sequence starts when the disk drive power supply interlock and sequencing logic accepts a momentary relay (K1) contact closure to ground of 20 mA maximum. With the relay contacts closed, the following sequence of events takes place: 1) a general reset is generated, 2) the dc <u>ON LIGHT is illuminated</u>, 3) all dc voltages are turned on in sequence except for the +24 Vdc control voltage, and 4) the power OFF LIGHT is deactivated.

#### 2.10.2 General Reset

During this condition, the ground level from +5V is activated for a minimum of one millisecond after stabilization of all dc voltages during the START sequence.

#### 2.10.3 Low Voltage

If the dc voltage, with the exception of the +24 Vdc control voltage, falls below the specified dc levels, the low voltage detector initiates an unconditional OFF sequence and illuminates the ATTEN LIGHT output voltage.

#### 2.10.4 Interlock

The power supply sequencing logic has two individual interlock inputs which inhibit operation of the OFF SWITCH-initiated sequence with a ground input from +5 Vdc.

#### 2.10.5 +24 Vdc Control Voltage

This voltage is activated directly from the primary ac power source and is not switched with the power supply sequencing logic or the ON or OFF relay contacts.

#### 2.10.6 Indicator Lamp Outputs

The indicator lamp output control voltage is +24V when OFF.

# Chapter 3 Installation and Operation

#### 3.1 INSTALLATION

The RK8 Disk System is installed at the customer's site by DEC Field Service personnel; therefore, no attempt should be made by customer personnel to install the equipment.

#### 3.2 INSPECTION

After removing the equipment packing material, inspect the equipment and report any damage to the local DEC sales office. Inspection procedures are as follows:

| Step | Procedure                                                                                                                                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Inspect external surfaces of the cabinets and related equipments for surface, bezel, switch, and light damage, etc.                                                                                                                                                      |

| 2    | Remove the shipping bolts from the rear door, and internally inspect<br>the cabinet for console, processor, and interconnecting cable damage;<br>inspect for loose mounting rails, loose or broken modules, blower or<br>fan damage, any loose nuts, bolts, screws, etc. |

| 3    | Inspect the wiring side of the logic panels for bent pins, cut wires,<br>loose external components and foreign material. Remedy any de-<br>fects found.                                                                                                                  |

| 4    | Inspect the power supply for proper seating of fuses and power con-<br>necting plugs .                                                                                                                                                                                   |

#### 3.3 CABINET INSTALLATION

The RK8 Disk cabinet is equipped with roll-around casters and adjustable leveling feet. It is not necessary to bolt the cabinet to the mounting floor unless conditions indicate otherwise (e.g., shipboard installation). Cabinet installation procedures are as follows:

### Step 1

Procedure

With the cabinet in the desired position, lower the leveling feet so that the cabinet is supported on the leveling feet, not the roll–around casters.

| Step | Procedure                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | Use a spirit level to level all cabinets and be certain that all leveling feet are firmly against the floor.                                                                          |

| 3    | If necessary, tighten the bolts that secure the cabinet groups together,<br>then recheck cabinet level. Again, make certain that all leveling<br>feet are seated firmly on the floor. |

#### 3.4 PROTECTIVE COVERINGS

When the RK8 Disk System has been correctly positioned at the installation site, the protective packing of the read/write head and the associated head carriage assembly tie-down binding must be removed. Access to these components is gained through the rear door of the cabinet and through removing the top cover panel from the disk assembly.

#### 3.5 PRIMARY AC POWER CABLES

The primary ac power cable is a three-wire cable which connects the installation site power source to the power supplies. The cable is connected at the factory to the disk power transformer for either 50 Hz or 60 Hz operation. The disk has a self-contained Type 721 Power Supply and an ac power cable (each wire in the cable is color coded, refer to Table 3-1 and Figure 3-1).

| Pigto<br>Line | uil Information<br>Wire Color | Terminal Strip Nomenclature | Plug |

|---------------|-------------------------------|-----------------------------|------|

| Green         | Frame Ground                  | Frame Ground                | W    |

| White         | Neutral/Line 2                | Neutral or Line 2           | X    |

| Black         | Line 1                        | Line 1                      | Y    |

Table 3–1 Power Cable Line Identification

#### WARNING

- a. The green wire is the cabinet frame ground and does not carry load current; however, it must be connected for safety reasons. This wire must be securely connected from the disk cabinet to the grounding point on the primary power source.

- b. The white or light gray wire is the neutral, common, ac return, or cold lead and must never be used for purposes of grounding the disk cabinet.

Figure 3-1 Disk and Type H721 Power Supplies

#### 3.6 AC POWER CHECK-OUT PROCEDURES

Before connecting the power cords to the disk, perform the following check-out procedures (see Figure 3-2).

#### CAUTION

Under no circumstances should the customer apply power to the RK8 Disk System unless a DEC Field Service Engineer is in attendance during installation.

| Step | Procedure                                                                                                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Measure the power source ac voltage and ensure that the proper voltage is present .                                                                                                                |

| 2    | Measure the voltage potential between the ac return and the frame ground<br>lines to ensure that no potential exists between earth ground (cold water<br>pipe) and the disk ground.                |

| 3    | Refer to Figure 3–3 and check the power supply transformer T1 primary windings terminated on the Jones–type terminal strip to be certain they are connected for proper voltage and line frequency. |

When neutral is not available for  $115 \vee 60 \text{ Hz} 15 \text{ A}$ service, a receptacle of this design shall be used except that both parallel slots shall be short so that polarized parallel blade plugs (caps) will not fit.

Figure 3-2 Hubbell Wall Receptacle Connector Diagram

| Step | Procedure                                                                                                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | Set the installation site primary power circuit breaker to the OFF position,<br>then plug the disk primary power line cord into the wall outlet. The red<br>lamp on the power supply control panel (see Figure 2–1) should illuminate<br>indicating primary ac power is applied to the transformer. |

| 5    | Set the source power circuit breaker to ON.                                                                                                                                                                                                                                                         |

#### 3.7 OPERATION

The procedures presented in this section outline the sequential steps which initiate operation of the disk.

The dc power must always be ON before inserting a disk cartridge into the disk. If the disk cartridge is inserted without first turning the dc power on, the read/write head carriage assembly may be in a position other than the home or data track 000 position and the cartridge would strike the read/write heads. The disk is interlock protected; consequently, when dc power is on and ac drive motor power is turned off, the read/write head carriage returns to the home position.

#### NOTE

Do not write on CE disk cartridge data tracks 090 through 110 because this area contains prerecorded test tracks, 095, 100, and 105 which would be destroyed. Any other data tracks can be used for test purposes.

#### 3.7.1 Sequencing

The correct sequencing procedure is as follows:

| Step | Procedure                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Depress the disk power supply dc ON/OFF switch to ON and observe that<br>the associated dc ON lamp illuminates. The read/write heads now seek<br>data track minus 003 at a relatively slow rate of speed (heads fully re-<br>tracted). |

| 2    | When the SAFE lamp, on the front control panel of the disk, comes on and the handle lock unlatches, the disk is ready to be loaded with a disk cartridge.                                                                              |

| 3    | Depress the disk power supply dc ON/OFF switch to OFF and observe that the disk sequences down.                                                                                                                                        |

|      | NOTE                                                                                                                                                                                                                                   |

|      | If there is the slightest indication of resistance to the in-<br>sertion of the disk cartridge into the disk receiver the                                                                                                              |

If there is the slightest indication of resistance to the insertion of the disk cartridge into the disk receiver, the cartridge should be removed and the interior of the disk receiver examined to determine the cause of resistance.

|                         | COMPONENT CHAI                             |            | VENDOR               | 1  |

|-------------------------|--------------------------------------------|------------|----------------------|----|

| CHT DEC                 |                                            | <u>, i</u> |                      | ł  |

| CKT. REF                | DESCRIPTION<br>P. C. CARD ASS'Y.           |            | PART NO<br>618 1979  | 4  |

| A1                      | FAN                                        |            | 312 0020             | ┨  |

| B1<br>C100              | CAPACITOR 12,000 MFD @ 30 VDC              |            | 304 2159             | ł  |

| C102,201                | CAPACITOR 12,000 MFD @ 25 VDC              |            | 304 1282             | 1  |

| C102.201                | CAPACITOR 0.0068 MFD @ 100 VI              |            | 304 0992             | 1  |

| C200                    | C/PACITOR 19,000 MFD @ 40 VD               |            | 304 2170             | 1  |

| C307,308                | CAPACITOR 1.0 MFD @ 50 VD                  | ;          | 304 1106             | 1  |

| C306                    | CAPACITOR 0.001 MFD @ 100 VDC              |            | 304 0714             | ]  |

| C300,301                | CAPACITOR 50,000 MFD @ 25 VDC              |            | 304 2153             |    |

| C302                    | CAPACITOR 500 MFD @ 25 VDC                 | _          | 304 1383             | ł  |

| C303                    | CAPACITOR 0.0022 MFD @ 100 VI              |            | <b>304</b> 1048      | 1  |

| C304                    | CAPACITOR 0.68 MFD @ 35 VDC                | 2          | 304 1332             | ł  |

| C305                    | CAPACITOR                                  | -          | 304 1397             | ł  |

| 11                      | TRANSFORMER                                |            | 602 2264             |    |

| CR100,101               | DIODE BRIDGE                               |            | 337 1558             | ł  |

| CR200.201               | DIODE BRIDGE                               | -          | <u> هر ار ر</u>      | ŀ  |

| CR300, 301              | DIODE 1N645                                | _          | 337 1363             | 1  |

| CR302,303               | DIODE IN1185A                              |            | 337 1329             | 1  |

|                         |                                            | _          |                      | I  |

|                         |                                            |            |                      | l  |

|                         |                                            |            |                      | I  |

| F100                    | FUSE 3A AGC                                |            | 315 0049             | ł  |

| F200                    | FUSE 5A AGC                                |            | 315 0242             | Į  |

| F 300                   | FUSE 25A AGC                               | _          | 315 0093             | ł  |

| F400                    | FUSE 12A ABC                               | _          | 315 0218             | ł  |

| Q302                    | TRANSISTOR 2N3055                          |            | 370 0202             | ł  |

| Q100,200                | TRANSISTOR 2N1613                          | _          | 370 0072             | ł  |

| Q301                    | н н<br>                                    |            | н                    | ł  |

| 0101.201                | IRANSI STOR 2N3054                         | _          | 370 0223             | ł  |

| Q303-310                | TRANSISTOR 2N3055                          | _          | 370_0219             | ł  |

| Q102,103                |                                            | _          | <u> </u>             | ł  |

| Q202,203<br>Q300        | S. C. R. C30U                              |            | 337 1560             | ł  |

| <b>4</b>                | 0. 0. IN 0.00                              |            | 551 1500             | 1  |

| R100_106                | RESISTOR 2600 5 W.                         | 12         | 340 1732             | 1. |

| R101                    |                                            | 5%         | 340 0619             | 1  |

| R102,201                |                                            | 5%         | 340 0629             | 1  |

| R103                    |                                            | 1%         | 240 6111             | 1  |

| R104,204                | POT. 5000 3/4 W. ±1                        | 0%         | 341 0656             | I  |

| R303,308                | <u>в в</u>                                 |            | 0                    |    |

| R105.205                | RESISTOR 9099 1/2 N.                       | 12         | 340 6279             | 1  |

| R200                    | RESISTOR 3000 10 W.                        | 5¥         | 340 1902             |    |

| R202                    | RESISTOR 2.7K 1 W.                         | <u>5%</u>  | 340 0635             | ł  |

| R203                    | RESISTOR 16900 1/2 #.                      | 1%         | 340 6278             | ١. |

| <u>R300,311</u><br>R301 | RESISTOR 100Ω 10 ₩.   RESISTOR 62Ω 2 ₩.    | 5%<br>5%   | 340 1900<br>340 0819 | μ  |

| R301                    | RESISTOR 620 2 W.<br>RESISTOR 75002 1/2 W. | 5%<br>1%   | 340 6113             | ł  |

| R302                    | RESISTOR 22100 1/2 W.                      | 1%         | 340 6238             | ł  |

|                         | RESISTOR 2K 1/2 W.                         | 5%         | 340 0160             | ł  |

| R305<br>R306            | RESISTOR 1K 1/2 W.                         | 5%<br>5%   | 340 0160             | ł  |

| R306                    | RESISTOR 6800 1/2 W.                       | 5%<br>5%   | 340 0133             | 1  |

| R307                    |                                            | 20%        | 341 0657             | 1  |

| R310                    |                                            | 3%         | 340 2966             | 1  |

| S1                      | THERMOSTAL                                 | •          | 366 0430             | I  |

| VR100,200               | ZENER IN751A                               |            | 337 1072             | 1- |

| VR300                   | 11 16                                      |            | н                    | I  |

| VR301                   | 1.C. REG. UA723C                           |            | 371 3001             | 1  |

| VR302                   | ZENER 1N749A                               |            | 337 1241             | 1  |

| FIRST USED ON OPTION/MOD                                                        | QTY.       | DESCR                              | IPTION     | PART NO.  | NO. |

|---------------------------------------------------------------------------------|------------|------------------------------------|------------|-----------|-----|

| PDP-15                                                                          |            | 2.0                                | PARTS LIST |           |     |

| UNLESS OTHERWISE SPECIFIED<br>UNLESS OTHERWISE SPECIFIED<br>DIMENSION IN INCHES | <u>3</u>   | DATE<br>-30-10<br>DATE<br>DATE     | digita     |           | J   |

| TOLERANCES<br>DECIMALS FRACTIONS ANGLES<br>± .405 ± 1/64 ± 0'34                 | PRO I      | Ela-Shand 2/9/70<br>ENG. () ADATE, | H72        | 21        |     |

| CORNERS                                                                         | -7<br>1999 |                                    | CIRCUIT S  | SCHEMATIC |     |

| MATERIAL.                                                                       | NEXT       |                                    |            |           | v   |

| FINISH                                                                          | SCAL       |                                    | DCS H721 - |           |     |

|                                                                                 | SHEE       | <u>1 / 0+ /</u>                    |            |           |     |

Figure 3-3 Type H721 Power Supply Block Schematic Diagram (D-BS-H721-0-1) The proper procedure for inserting the disk cartridge is as follows:

| Step | Procedure                                                                                                                                                                                                                                                                                                                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Make certain the dc power is ON.                                                                                                                                                                                                                                                                                                                                                                  |

| 2    | Pull the disk cartridge access door panel, then lower the disk cartridge<br>receiver handle to the down or unloaded position. The cartridge receiver<br>is now raised into position for insertion of the disk cartridge. The handle<br>interlock will keep the cartridge receiver handle locked in its closed<br>position whenever the SAFE lamp is turned OFF.                                   |

| 3    | Slowly slide the disk cartridge into the receiver assembly and make certain there is no internal resistance to its insertion.                                                                                                                                                                                                                                                                     |

| 4    | Raise the disk cartridge receiver handle to the up or loaded position to seat the disk armature plate securely on the spindle assembly. Do not force the handle.                                                                                                                                                                                                                                  |

|      | When the disk cartridge is properly loaded, a disk carriage microswitch places the disk in the ON position.                                                                                                                                                                                                                                                                                       |

| 5    | Close the disk cartridge access door.                                                                                                                                                                                                                                                                                                                                                             |

|      | NOTE                                                                                                                                                                                                                                                                                                                                                                                              |

|      | An interlock switch is activated when the disk cartridge<br>is properly inserted. However, if the switch is not acti-<br>vated, the drive is not put in the ready condition. If the<br>switch should transfer to its unoperative position during an<br>otherwise normal operation, the disk will immediately se-<br>quence down to a stopped condition and the SAFE light<br>will be illuminated. |

| 6    | Set the START/STOP switch to the START or up position to put the disk drive<br>system into operation. A disk handle interlock will be activated to ensure<br>that the handle cannot be raised during normal operation. The drive motor<br>is then energized to bring the disk up to its proper operating speed.                                                                                   |

| 7    | A 90 second delay occurs after the disk has reached its operational speed of 1500 rpm allowing it to reach a stabilized condition. During this delay, the read/write heads are loaded on data track 000.                                                                                                                                                                                          |

| 8    | After the disk has stabilized, the READY lamp will illuminate, indicating that it is ready for actual operation.                                                                                                                                                                                                                                                                                  |

#### 3.7.3 Disk Cartridge Removal

The following procedure should be followed for disk cartridge removal:

#### Step

#### Procedure

- 1 Make certain the dc power is ON.

- 2 Set the START/STOP switch to the STOP or down position. In this position, the read/write heads are unloaded and the read/write head responsyn positioner assembly moves the heads to seek data track -003. The disk now begins its deceleration cycle which, when completed, will be in a SAFE condition.

| Step | Procedure                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------|

| 3    | After disk drive rotation has stopped, the disk cartridge receiver interlock is released and the SAFE lamp illuminates. |

| 4    | Open the disk cartridge access door and pull the cartridge receiver handle down.                                        |

| 5    | Remove the disk cartridge from the cartridge receiver assembly.                                                         |

## 3.7.4 Disk Cartridge Handling

The 0 and 1 surfaces of the aluminum, oxide-coated disk platter are sensitive to foreign particles introduced into the interior of the disk cartridge. For this reason, the disk cartridge read/write head access door and the air intake valve must not be opened after the disk cartridge is removed from the disk system. The only exception is when the disk must be cleaned and this must be done in a "white room" atmosphere.

The disk cartridge must not be subjected to top loading or protruding objects when removed from the machine because deformity of the cartridge-centering diaphragm can result. Damage to this diaphragm renders the cartridge useless and damage to the read/write heads is possible.

The aluminum disk contains valuable data pertinent to a user's program and therefore must be protected. To maintain extended life of the disk cartridge, the following steps should be followed:

| Step | Procedure                                                                                                                                                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Keep the external surface of the disk cartridge free of dust and dirt con-<br>taminants by wiping it with a lint-free cloth .                                                                                                                                        |

| 2    | Replace a disk cartridge with broken or damaged access doors.                                                                                                                                                                                                        |

| 3    | A preventive maintenance routine should be established to ensure that<br>foreign particles have not entered the disk cartridge. If the disk cartridge<br>becomes damaged or its interior becomes dirty, it should be replaced.                                       |

| 4    | The disk cartridge cover must not be depressed while the disk is in operation because it will cause the cartridge cover to strike the surface of the disk rendering it useless.                                                                                      |

| 5    | Beverages should not be placed in close proximity to the disk. If a beverage is spilled onto the disk, it should be examined by DEC Field Service personnel to determine the extent of damage and whether the disk can be operated.                                  |

| 6    | Do not smoke near the disk since ashes can damage the disk surface.                                                                                                                                                                                                  |

| 7    | When the disk cartridge is removed from the disk cartridge receiver<br>assembly, the disk cartridge access door and air valve should be checked<br>to be certain they are securely closed. If open, a slight pressure on<br>their external surfaces will close them. |

## Procedure

8 When the disk cartridge is introduced into the installation room environment where the temperature change may be extreme, approximately two hours should be allowed for conditioning of the aluminum disk platter. A conditioning period of approximately 15 minutes is normally all that is necessary. If disk conditioning is not allowed, track registration and data recording retrieval errors can occur.

## 3.7.5 Storage and Shipping of Disk Cartridges

Disk cartridges that receive the most use should be stored in the room where the Disk is installed or in a similar environment. The suggested environmental conditions are 65°F to 90°F (32°C) and 20% to 80% relative humidity. A disk cartridge must be conditioned to the environmental conditions of the room it is to be operated in. Disk cartridges are best stored in their original shipping containers on flat surfaces, free of other objects.

## NOTE

Only when the disk cartridges are in their original shipping containers can they be stacked or stored on edge.

When shipping disk cartridges, the original shipping containers must be used.

Disk cartridge specifications are described in Table 3-2.

| Description                 | Sį                                            | pecification                                                             |

|-----------------------------|-----------------------------------------------|--------------------------------------------------------------------------|

| Disk Cartridge (with cover) | Diameter:<br>Height:                          | 15.0 in.<br>1.5 in.                                                      |

| Shipping Container          | Length:<br>Height:                            | 19.9 in.<br>6.5 in.                                                      |

| Temperature Range           | Shipping:<br>Operating:<br>Relative Humidity: | 40°F (-10°C) to 150°F (65°C)<br>65°F (18°C) to 90°F (32°C)<br>20% to 80% |

## Table 3-2 Disk Cartridge Specifications

Step

# Chapter 4 Programming

The software written for the RK8 Disk has increased its capabilities and expandability; it has also provided device-independent access to as many as fifteen I/O devices. It is possible to write a device handler in one, or in some cases, two core pages and interface it to the system software.

The user's program can call various monitor services, including file manipulation and program chaining with access to standard DEC programs.

To build the RK8 Disk System and to load programs, the user requires a minimum of 8K of core memory, at least one RK8 Disk and either a high-speed paper tape reader or DECtape.

## 4.1 DISK OPERATION

Before the disk becomes fully operational, a 90 second time delay occurs allowing the disk to reach a speed of 1500 rpm. During this time delay the magnetic read/write heads are loaded and flying above the surface of the disk and are in the data track 000 or home position.

Access to any of the 200 data tracks (203 with three spare data tracks) is achieved in an average positioning time of 134 ms. The read/write head responsyn positioner assembly operates in a sequential stepping mode with a minimum positioning time of 2 ms.

Frequency of data transmission is 720K data bits per second. Double-frequency recording is used with an overall frequency of 1,440,000 bits per second, including clock and data bits.

When the disk is operating, internal circuits are continuously monitoring the disk cartridge platter speed so that if the disk falls below speed, the RK01 automatically cycles down providing appropriate indications through the Disk Control. A hysteresis main drive motor maintains disk speed at a uniform rate.

## 4.2 PROGRAMMING

A normal programming sequence is as follows: