Digital Equipment Corporation Maynard, Massachusetts

# MAINTENANCE MANUAL

DEC-16-HMMMA-A-D

# PDP16-M MAINTENANCE MANUAL

digital equipment corporation · maynard, massachusetts

1st Edition February 1973

## Copyright © 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

## CONTENTS

### Page

| CHAPTERT                                                                                                         | GENERAL INFORMATION                       |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1.1                                                                                                              | Introduction                              |

| 1.2                                                                                                              | Functional Description                    |

| 1.2.1                                                                                                            | Control                                   |

| 1.2.1.1                                                                                                          | Program Control Sequencer                 |

| 1.2.1.2                                                                                                          | Control PROM                              |

| 1.2.1.3                                                                                                          | Evoke Decoders                            |

| 1.2.1.4                                                                                                          | Flag (MUX and PAGE) Module                |

| 1.2.1.5                                                                                                          | Page Evoke Module                         |

| 1.2.1.6                                                                                                          | Boolean Input Multiplexer                 |

| 1.2.2                                                                                                            | Data Processor                            |

| 1.2.2.1                                                                                                          | General Purpose Arithmetic (GPA) Register |

| 1.2.2.2                                                                                                          | General Purpose Arithmetic (GPA) Control  |

| 1.2.2.3                                                                                                          | Link (L) Flip-Flop                        |

| 1.2.2.4                                                                                                          | Constant (C) Generator                    |

| 1.2.2.5                                                                                                          | Transfer Register (TR) 1-4                |

| 1.2.2.6                                                                                                          | Boolean Output/Flags (FF1 – FF3) Module   |

| 1.2.2.7                                                                                                          | General Purpose Interface No. 1 (GPI 1)   |

| 1.2.2.8                                                                                                          | Bus Sense and Termination Module          |

| 1.2.3                                                                                                            | Memory Options                            |

| 1.2.3.1                                                                                                          | Constant Generator MR16-D                 |

| 1.2.3.2                                                                                                          | Data PROM MR 16-E                         |

| 1.2.3.3                                                                                                          | Scratch Pad (SP) Register MS16-C          |

| 1.2.3.4                                                                                                          | Data R/W MOS Memory MS16-D                |

| 1.2.3.5                                                                                                          | Data R/W MOS Memory MS16-E                |

| 1.2.4                                                                                                            | I/O Options                               |

| 1.2,4.1                                                                                                          | General Purpose Interface DB16-A          |

| 1.2.4.2                                                                                                          | Serial Interface DC16-A                   |

| 1.2.4.3                                                                                                          | Boolean Input Multiplexer PCS16-D         |

| 1.2.4.4                                                                                                          | Boolean Output/Flag Module KFL16          |

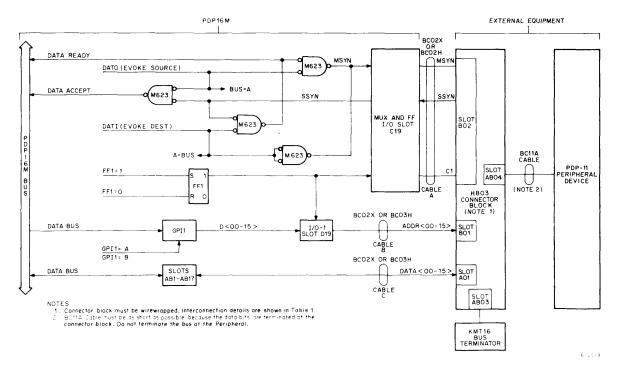

| 1.2.4.5                                                                                                          | PDP-11 Peripheral Interface DA16-F        |

| 1.2.5                                                                                                            | Interfacing Details                       |

| 1.2.5.1                                                                                                          | Peripheral Interface 1.7                  |

| 1.2.5.2                                                                                                          | Interface Sockets                         |

| 1.2.5.3                                                                                                          | DC16-B Serial Interface Adapter           |

| 1.3                                                                                                              | Physical Description                      |

| 1.4                                                                                                              | Specifications                            |

| 1.4.1                                                                                                            | Processor                                 |

| 1.4.2                                                                                                            | Mechanical                                |

| 1.4.3                                                                                                            | Electrical                                |

| 1.4.4                                                                                                            | Environmental                             |

| 1.5                                                                                                              | Configuration Data                        |

| CHAPTER 2                                                                                                        | INSTALLATION                              |

| 2.1                                                                                                              | General                                   |

| 2.2                                                                                                              | Unpacking                                 |

| 2.3                                                                                                              | Inspection                                |

| and the second |                                           |

####

### **CONTENTS** (Cont)

•

| 2.5       Checkout Procedure       2-3         2.5.1       Equipment Required       2-3         2.5.2       Procedures       2-3         CHAPTER 3       OPERATION AND PROGRAMMING       3-1         3.1       Controls and Indicators       3-1         3.2       Instruction Format       3-1         3.2.1       LET Instruction       3-2         3.2.2       GOTO Instruction       3-2         3.2.3       IF Instruction       3-2         3.2.4       CALL Instruction       3-2         3.2.5       EXIT Instruction       3-2         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-4         3.3.4       Constant Generator Group       3-5         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-5         3.3.7       Test Group       3-5                                                                                                                                                                                                                                                                                                                                   |           |                                                          | Page   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------|--------|

| 25.1       Equipment Required       23         25.2       Procedures       23         25.2       Procedures       23         CHAPTER 3       OPERATION AND PROGRAMMING       31         3.1       Controls and Indicators       31         3.2       Instruction Format       31         3.2.1       LET Instruction       32         3.2.2       GOTO Instruction       32         3.2.3       IF Instruction       32         3.2.4       CALL Instruction       32         3.2.5       EXIT Instruction       33         3.3       Basic Instruction Rest       33         3.3.1       Arithmetic Group       34         3.3.2       Logical Group       34         3.3.4       Constant Generator Group       34         3.3.5       I/O Group       35         3.3.6       Command Group       36         3.3.7       Test Group       36         3.3.8       Conditional Jump Group       36         3.3.9       Subroutine Group       37         3.4       A and B Registers       37         3.5       Link (Overflow)       38         3.6       Boolean I/O                                                                                                                                     | 2.4       | Installation Procedure                                   | . 2-1  |

| 2.5.2       Procedures       2.3         CHAPTER 3       OPERATION AND PROGRAMMING       3.1         3.1       Controls and Indicators       3.1         3.2       Instruction Format       3.1         3.2.1       LET Instruction       3.2         3.2.2       GOTO Instruction       3.2         3.2.3       IF Instruction       3.2         3.2.4       CALL Instruction       3.2         3.2.5       EXIT Instruction       3.2         3.2.6       EXIT Instruction Set       3.3         3.3       Baic Instruction Set       3.3         3.3.2       Logical Group       3.3         3.3.3       Register Group       3.4         3.3.4       Constant Generator Group       3.5         3.3.5       I/O Group       3.5         3.3.6       Command Group       3.6         3.3.8       Conditional Jump Group       3.6         3.3.9       Subroutine Group       3.7         3.4       A and B Registers       3.7         3.5       Link (Overflow)       3.8         3.6       Boolean I/O       3.8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3.8                                                                                                          | 2.5       | Checkout Procedure                                       | . 2-3  |

| CHAPTER 3         OPERATION AND PROGRAMMING           3.1         Controls and Indicators         3.1           3.2         Instruction Format         3.1           3.2.1         LET Instruction         3.2           3.2.2         GOTO Instruction         3.2           3.2.3         IF Instruction         3.2           3.2.4         CALL Instruction         3.2           3.2.5         EXIT Instruction         3.3           3.3         Basic Instruction Set         3.3           3.3.1         Arithmetic Group         3.4           3.3.2         Logical Group         3.4           3.3.3         Register Group         3.4           3.3.4         Constant Generator Group         3.4           3.3.5         I/O Group         3.5           3.3.6         Command Group         3.6           3.3.7         Test Group         3.6           3.3.8         Conditional Jump Group         3.6           3.3.9         Subroutine Group         3.6           3.4         A and B Registers         3.7           3.5         Link (Overflow)         3.8           3.6         Boolean I/O         3.8           3.7 <td>2.5.1</td> <td>Equipment Required</td> <td>. 2-3</td> | 2.5.1     | Equipment Required                                       | . 2-3  |

| 3.1       Controls and Indicators       3-1         3.2       Instruction Format       3-1         3.2.1       LET Instruction       3-2         3.2.2       GOTO Instruction       3-2         3.2.3       IF Instruction       3-2         3.2.4       CALL Instruction       3-2         3.2.5       EXIT Instruction       3-3         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-4         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-4         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-6         3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9                                                                                                                      | 2.5.2     | Procedures                                               | . 2-3  |

| 3.2       Instruction Format       3-1         3.2.1       LET Instruction       3-2         3.2.2       GOTO Instruction       3-2         3.2.3       IF Instruction       3-2         3.2.4       CALL Instruction       3-2         3.2.5       EXIT Instruction       3-3         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logial Group       3-4         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-5         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-5         3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.6       Constant Generator (C)       3-9         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-9                                                                                               | CHAPTER 3 | OPERATION AND PROGRAMMING                                |        |

| 32.1       LET Instruction       3-2         32.2       GOTO Instruction       3-2         32.3       IF Instruction       3-2         32.4       CALL Instruction       3-2         32.5       EXIT Instruction       3-3         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-4         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-5         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-6         3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       Tarsfer Register (TR)       3-9         3.11       MUX Selection       3-9         3.12       Page Linkages       3-10         3.13       Page Linkages       3-10         3.14       Program Countrol Sequen                                                                                                                             | 3.1       | Controls and Indicators                                  | . 3-1  |

| 3.2.2       GOTO Instruction       3.2         3.2.3       IF Instruction       3.2         3.2.4       CALL Instruction       3.2         3.2.5       EXIT Instruction Set       3.3         3.3       Basic Instruction Set       3.3         3.3.1       Arithmetic Group       3.3         3.3.2       Logical Group       3.4         3.3.3       Register Group       3.4         3.3.4       Constant Generator Group       3.4         3.3.5       I/O Group       3.5         3.3.6       Command Group       3.5         3.3.7       Test Group       3.6         3.3.8       Conditional Jump Group       3.6         3.3.9       Subroutine Group       3.6         3.3.9       Subroutine Group       3.7         3.4       A and B Registers       3.7         3.5       Link (Overflow)       3.8         3.6       Constant Generator (C)       3.9         3.10       Bus Sense and Terminator       3.9         3.11       MUX Selection       3.9         3.12       Page Selection       3.40         3.13       Page Linkages       3.10         3.14       <                                                                                                                         | 3.2       |                                                          | . 3-1  |

| 32.3       IF Instruction       3-2         32.4       CALL Instruction       3-2         32.5       EXIT Instruction       3-3         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-4         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-5         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-5         3.3.7       Test Group       3-6         3.8       Conditional Jump Group       3-6         3.3.8       Conditional Jump Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.7       GP11 (General C(C)       3-9         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9                                                                                                                  | 3.2.1     | LET Instruction                                          | • • -  |

| 3.2.4       CALL Instruction       3-2         3.2.5       EXIT Instruction       3-3         3.3       Basic Instruction Set       3-3         3.3.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-3         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-5         3.5.5       I/O Group       3-5         3.6       Command Group       3-6         3.7       Test Group       3-6         3.8       Conditional Jump Group       3-6         3.7       Test Group       3-6         3.8       Conditional Jump Group       3-6         3.8       Conditional Jump Group       3-6         3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-9         3.8       Constant Generator (C)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9                                                                                                                             | 3.2.2     | GOTO Instruction                                         | . 3-2  |

| 3.2.5       EXIT Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.2.3     | IF Instruction                                           | . 3-2  |

| 3.3       Basic Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.2.4     | CALL Instruction                                         | . 3-2  |

| 33.1       Arithmetic Group       3-3         3.3.2       Logical Group       3-4         3.3.3       Register Group       3-4         3.3.4       Constant Generator Group       3-5         3.5       I/O Group       3-5         3.6       Command Group       3-5         3.7       Test Group       3-6         3.8       Conditional Jump Group       3-6         3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.6       Boolean I/O       3-9         3.1       MUX Selection       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Program Control Sequencer       44         4.2.1.1       State Generator       44 <td>3.2.5</td> <td>EXIT Instruction</td> <td>. 3-3</td>                                      | 3.2.5     | EXIT Instruction                                         | . 3-3  |

| 3.3.2       Logical Group       34         3.3.3       Register Group       34         3.3.4       Constant Generator Group       34         3.3.5       I/O Group       35         3.3.6       Command Group       35         3.3.7       Test Group       36         3.8       Conditional Jump Group       36         3.9       Subroutine Group       37         3.4       A and B Registers       37         3.5       Link (Overflow)       38         3.6       Boolean I/O       38         3.7       GPI1 (General Purpose Interface) – Parallel I/O       38         3.8       Constant Generator (C)       39         3.9       Transfer Register (TR)       39         3.10       Bus Sense and Terminator       39         3.11       MUX Selection       310         3.12       Page Selection       310         3.13       Page Linkages       310         3.14       Start, Clock, and Evoke Enable Logic       44         4.2.1.1       Program Control Sequencer       44         4.2.1.2       Instruction Decoder       44         4.2.1.3       State Generator       44                                                                                                              | 3.3       | Basic Instruction Set                                    | . 3-3  |

| 3.3.3       Register Group       34         3.3.4       Constant Generator Group       35         3.3.5       I/O Group       35         3.3.6       Command Group       35         3.3.7       Test Group       36         3.3.8       Conditional Jump Group       36         3.3.8       Conditional Jump Group       36         3.3.9       Subroutine Group       37         3.4       A and B Registers       37         3.5       Link (Overflow)       38         3.6       Boolean I/O       38         3.6       Boolean I/O       38         3.6       Boolean I/O       38         3.6       Boolean I/O       38         3.7       GPI1 (General Purpose Interface) – Parallel I/O       38         3.8       Constant Generator (C)       39         3.9       Transfer Register (TR)       39         3.10       Bus Sense and Terminator       39         3.11       MUX Selection       39         3.12       Page Selection       310         3.13       Page Linkages       310         3.14       Program Control Sequencer       44         4.2.1.1 <td< td=""><td>3.3.1</td><td>Arithmetic Group</td><td>. 3-3</td></td<>                                                            | 3.3.1     | Arithmetic Group                                         | . 3-3  |

| 3.3.4       Constant Generator Group       3-5         3.3.5       I/O Group       3-5         3.3.6       Command Group       3-5         3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-9         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION         4.1       Introduction       4-4         4.2.1       Program Control Sequencer       4-4                                                                                                      | 3.3.2     | Logical Group                                            | . 3-4  |

| 3.3.5       I/O Group       3-5         3.3.6       Command Group       3-5         3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GP11 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5 </td <td>3.3.3</td> <td>Register Group</td> <td>. 3-4</td>                                           | 3.3.3     | Register Group                                           | . 3-4  |

| 3.3.6       Command Group       3-5         3.7       Test Group       3-6         3.8       Conditional Jump Group       3-6         3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.6       Boolean I/O       3-8         3.6       Boolean I/O       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         ChAPTER 4       THEORY OF OPERATION       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       State Generator       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4                                                                                                                         | 3.3.4     | Constant Generator Group                                 | . 3-5  |

| 3.3.7       Test Group       3-6         3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Introduction       4-1         4.2       Control Section       3-10         3.13       Page Linkages       3-10         4.2       Control Section       4-4         4.2.1.1       Program Control Sequencer       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4                                                                                          | 3.3.5     | I/O Group                                                | . 3-5  |

| 3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Introduction       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean                                                                                  | 3.3.6     |                                                          | . 3-5  |

| 3.3.8       Conditional Jump Group       3-6         3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Introduction       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean                                                                                  | 3.3.7     |                                                          | . 3-6  |

| 3.3.9       Subroutine Group       3-7         3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         3.14       Introduction       4-1         4.1       Introduction       4-1         4.2       Control Section       4-1         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evok                                                                                 | 3.3.8     | Conditional Jump Group                                   | . 3-6  |

| 3.4       A and B Registers       3-7         3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       4-1         4.1       Introduction       4-1         4.2       Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-4         4.2.1       Boolean Input Multiplexers       4-7         4.2.4                                                                               | 3.3.9     |                                                          | . 3-7  |

| 3.5       Link (Overflow)       3-8         3.6       Boolean I/O       3-8         3.7       GPI 1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       3-10         CHAPTER 4       Theory of operation       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Countrel (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-7         4.2.                                                                        | 3.4       | •                                                        | . 3-7  |

| 3.6       Boolean I/O       3-8         3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-7         4.3       Data Section       4-7                                                                                                                                                 |           | 5                                                        | . 3-8  |

| 3.7       GPI1 (General Purpose Interface) – Parallel I/O       3-8         3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-7         4.3       Data Section       4-7                                                                                                                                                                                         |           |                                                          | . 3-8  |

| 3.8       Constant Generator (C)       3-9         3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-7         4.3       Data Section       4-9                                                                                                                                                                                                                                                                     |           |                                                          | 3-8    |

| 3.9       Transfer Register (TR)       3-9         3.10       Bus Sense and Terminator       3-9         3.11       MUX Selection       3-9         3.12       Page Selection       3-10         3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-8         4.3       Data Section       4-9                                                                                                                                                                                                                                                                                                                                  |           |                                                          |        |

| 3.10Bus Sense and Terminator3-93.11MUX Selection3-93.12Page Selection3-103.13Page Linkages3-10CHAPTER 4THEORY OF OPERATION4.1Introduction4-14.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                                          |        |

| 3.11MUX Selection3-93.12Page Selection3-103.13Page Linkages3-10CHAPTER 4THEORY OF OPERATION4.1Introduction4-14.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | •                                                        |        |

| 3.12Page Selection3-103.13Page Linkages3-10CHAPTER 4THEORY OF OPERATION4.1Introduction4-14.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.3Boolean Input Multiplexers4-74.2.4Evoke Decoders4-74.2.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                          | •      |

| 3.13       Page Linkages       3-10         CHAPTER 4       THEORY OF OPERATION       4-1         4.1       Introduction       4-1         4.2       Control Section       4-4         4.2.1       Program Control Sequencer       4-4         4.2.1.1       Start, Clock, and Evoke Enable Logic       4-4         4.2.1.2       Instruction Decoder       4-4         4.2.1.3       State Generator       4-4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.3       Data Section       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                                                          |        |

| CHAPTER 4THEORY OF OPERATION4.1Introduction4-14.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-44.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | •                                                        |        |

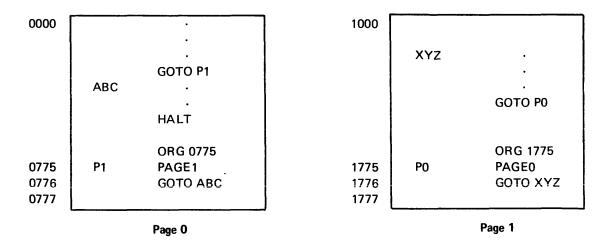

| 4.1Introduction4-14.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.13      |                                                          | . 5-10 |

| 4.2Control Section4-44.2.1Program Control Sequencer4-44.2.1.1Start, Clock, and Evoke Enable Logic4-44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-44.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.2.4Evoke Decoders4-84.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CHAPTER 4 | THEORY OF OPERATION                                      |        |

| 4.2.1Program Control Sequencer4.44.2.1.1Start, Clock, and Evoke Enable Logic4.44.2.1.2Instruction Decoder4.44.2.1.3State Generator4.44.2.1.4Program Counter (PC) and Stack4.44.2.2Memory and Page Select4.74.2.3Boolean Input Multiplexers4.74.2.4Evoke Decoders4.84.3Data Section4.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.1       | Introduction                                             | . 4-1  |

| 4.2.1.1Start, Clock, and Evoke Enable Logic4.44.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.2.4Evoke Decoders4-84.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.2       | Control Section                                          | . 4-4  |

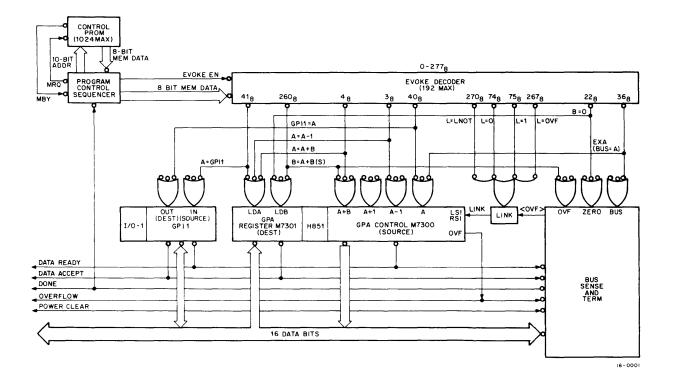

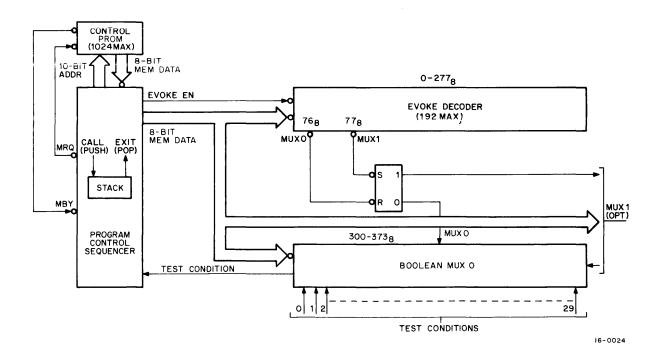

| 4.2.1.2Instruction Decoder4-44.2.1.3State Generator4-44.2.1.4Program Counter (PC) and Stack4-54.2.2Memory and Page Select4-74.2.3Boolean Input Multiplexers4-74.2.4Evoke Decoders4-84.3Data Section4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.1     | Program Control Sequencer                                | . 4-4  |

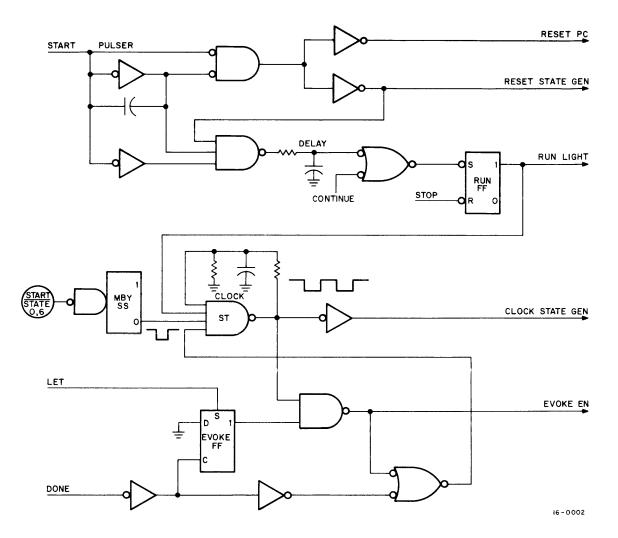

| 4.2.1.3       State Generator       4.4         4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-8         4.3       Data Section       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.1.1   | Start, Clock, and Evoke Enable Logic                     | . 4-4  |

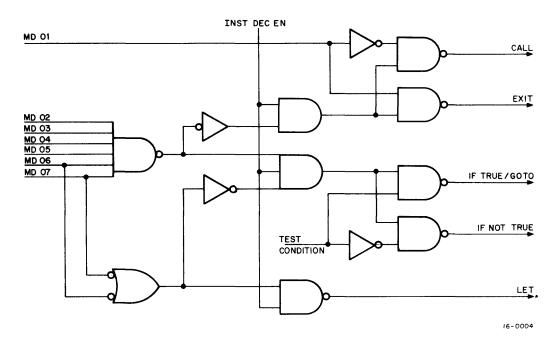

| 4.2.1.4       Program Counter (PC) and Stack       4-5         4.2.2       Memory and Page Select       4-7         4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-8         4.3       Data Section       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.1.2   | Instruction Decoder                                      | . 4-4  |

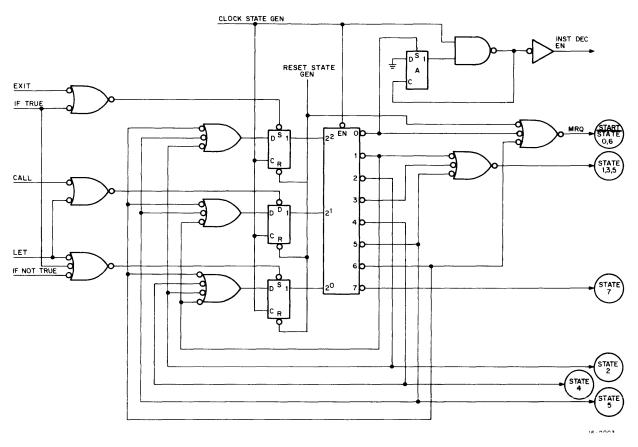

| 4.2.2       Memory and Page Select       4.7         4.2.3       Boolean Input Multiplexers       4.7         4.2.4       Evoke Decoders       4.8         4.3       Data Section       4.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.1.3   | State Generator                                          | . 4-4  |

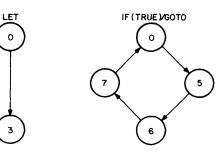

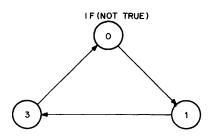

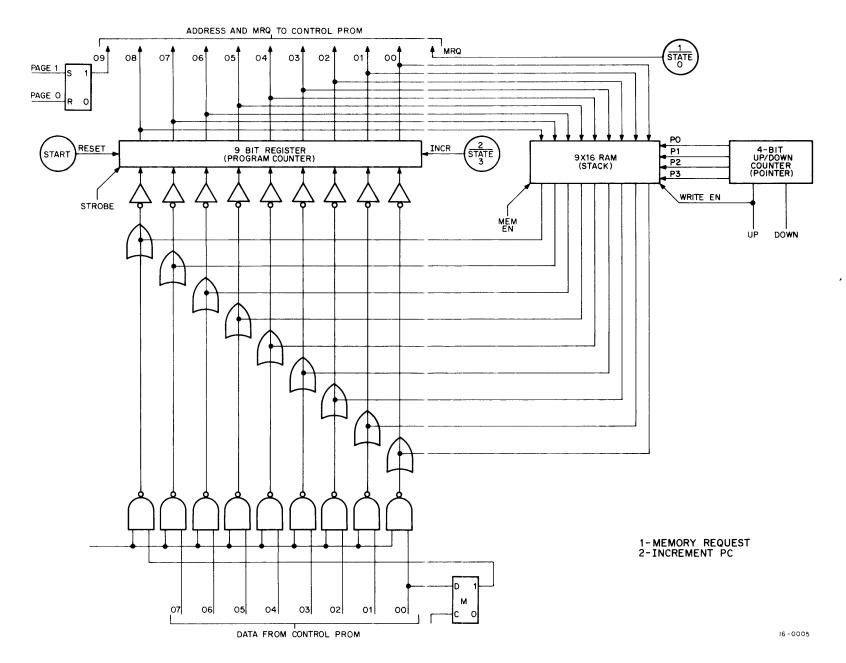

| 4.2.3       Boolean Input Multiplexers       4-7         4.2.4       Evoke Decoders       4-8         4.3       Data Section       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.1.4   | Program Counter (PC) and Stack                           | . 4-5  |

| 4.2.3         Boolean Input Multiplexers         4-7           4.2.4         Evoke Decoders         4-8           4.3         Data Section         4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.2.2     | Memory and Page Select                                   | . 4-7  |

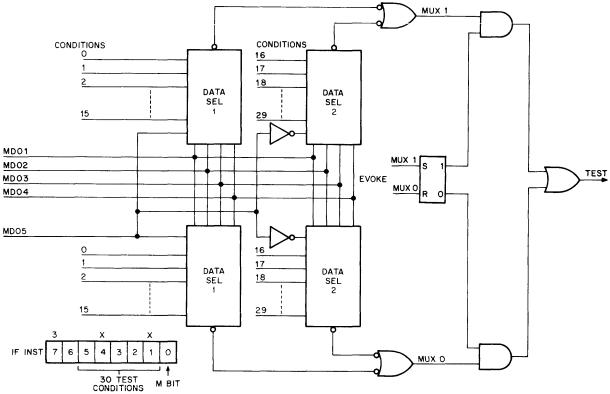

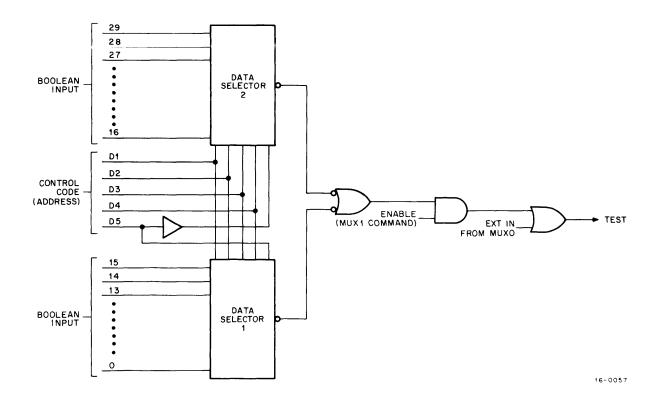

| 4.3 Data Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.2.3     | Boolean Input Multiplexers                               | . 4-7  |

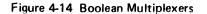

| 4.3 Data Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.2.4     | Evoke Decoders                                           | . 4-8  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.3       |                                                          |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.3.1     | General Purpose Arithmetic (GPA) Unit, LINK and OVERFLOW | . 4-9  |

#### **CONTENTS** (Cont)

Page

| 4.3.2     | Transfer Register (TR)                 |

|-----------|----------------------------------------|

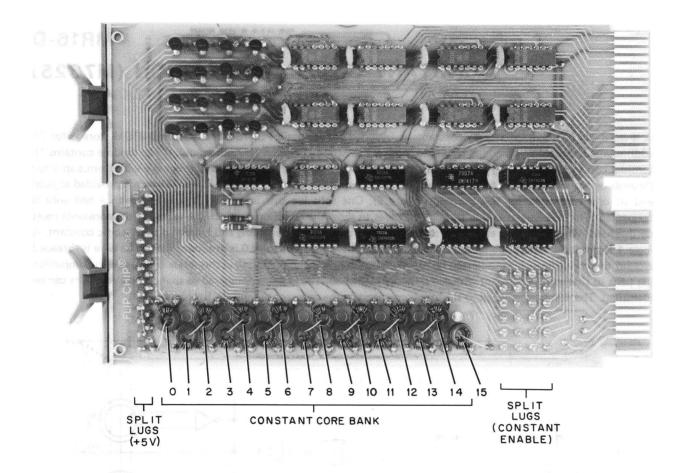

| 4.3.3     | Constant Generator (C)                 |

| 4.3.4     | General Purpose Interface No. 1 (GPI1) |

| 4.3.5     | Bus Sense and Termination Module (BS)  |

| 4.3.6     | Data Transfer Timing                   |

| CHAPTER 5 | MAINTENANCE                            |

| 5.1       | Preparation and Maintenance            |

| 5.1.1     | Equipment Required                     |

| 5.1.2     | Maintenance Modules                    |

| 5.1.2.1   | Bus Monitor Module M7332               |

| 5.1.2.2   | Service Module M7335                   |

| 5.1.2.3   | Option Switch Module M7334             |

| 5.1.3     | Maintenance Programs                   |

| 5.1.4     | Maintenance Setup                      |

| 5.2       | Preventive Maintenance                 |

| 5.3       | Corrective Maintenance                 |

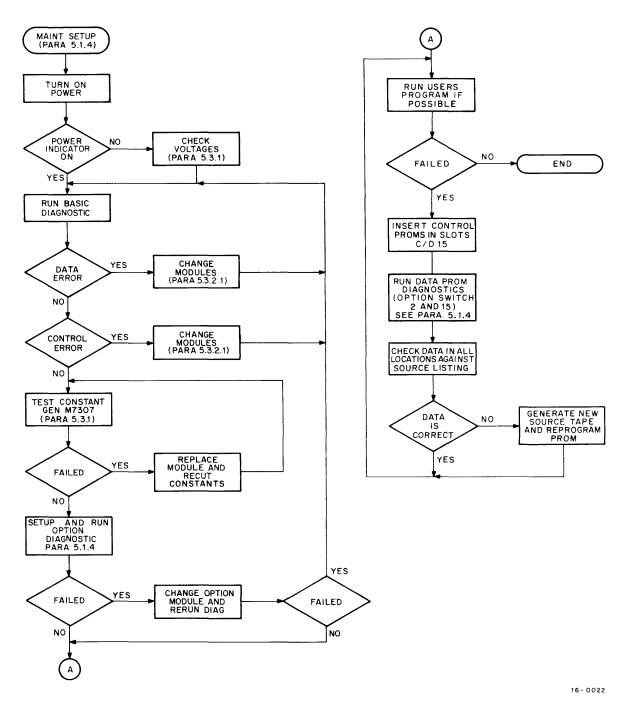

| 5.3.1     | Repair Procedure                       |

| 5.3.2     | Module Swapping Priorities             |

| 5.3.2.1   | Data Error                             |

| 5.3.2.2   | Control Error                          |

#### APPENDIX A HARDWARE OPTION DESCRIPTIONS

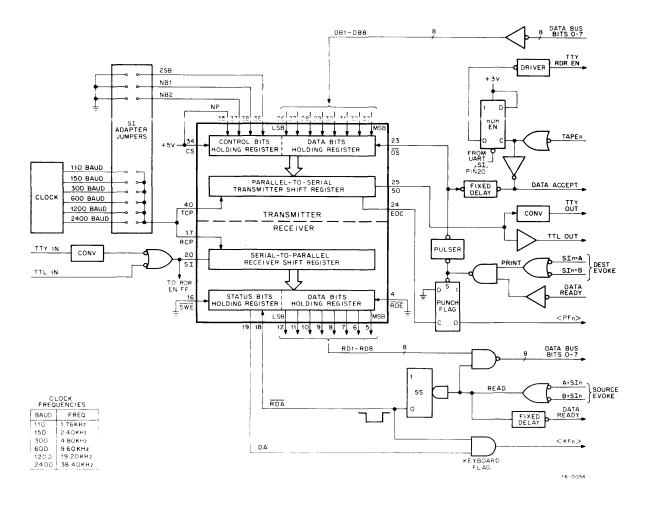

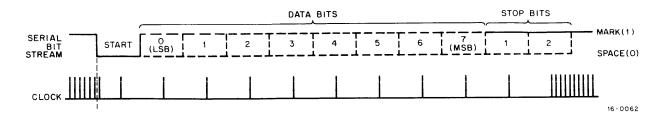

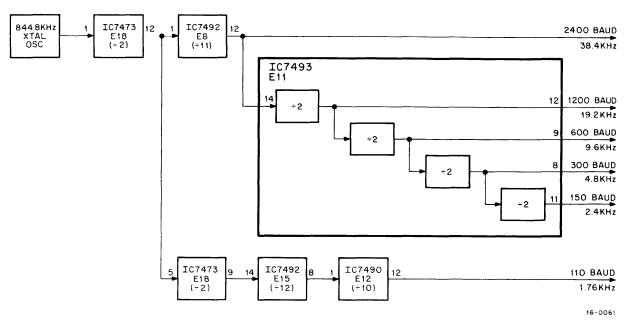

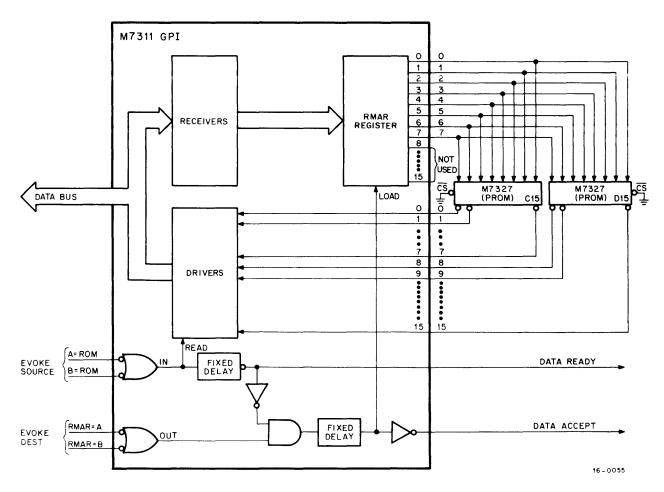

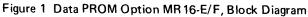

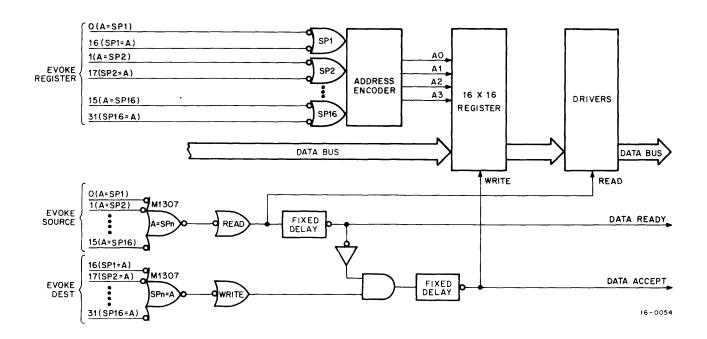

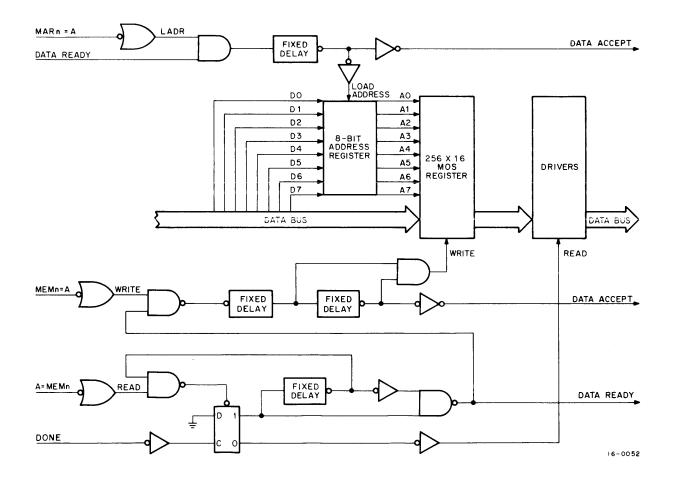

DA 16-F Peripheral Interface Option (M623) DB 16-A Parallel I/O Option (M7311) DC 16-A Serial I/O Option (M7313) KFL 16 Boolean Output/Flag Option (M7306) MR 16-D Constant Generator Option (M7325) MR 16-E/F Data PROM Option (M7327) MS 16-C Scratch Pad Register Option (M7318) MS 16-D Data R/W MOS Memory Option (M7319) MS 16-E Data R/W MOS Memory Option (M7324) PCS 16-B Control PROM Option (M7327) PCS 16-D Boolean Input Multiplexer Option (M7329)

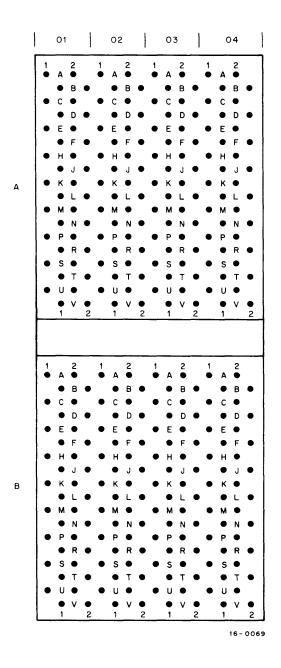

## APPENDIX B MAINTENANCE HARDWARE CONSTRUCTION PROCEDURE

- APPENDIX C SIGNAL LISTING

- APPENDIX D PDP16-M MACHINE CODES

#### **ILLUSTRATIONS**

| Figure No. | Title                               |       |

|------------|-------------------------------------|-------|

| 1-1        | PDP16-M Minicomputer, Block Diagram | . 1-2 |

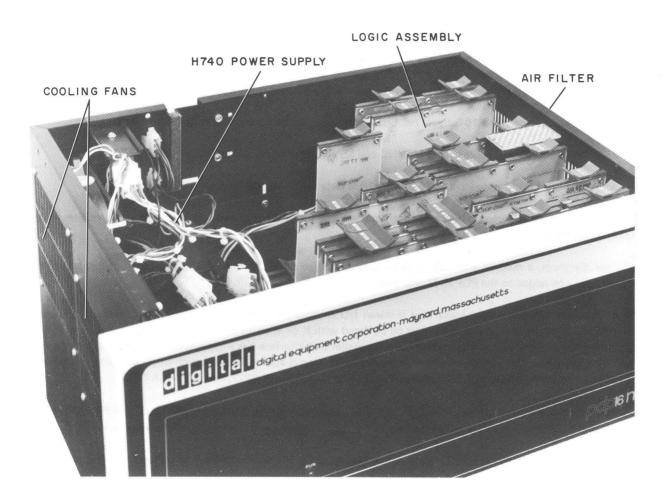

| 1-2        | PDP16-M Oblique View                | . 1-8 |

## ILLUSTRATIONS (Cont)

|      |                                                        | Page   |

|------|--------------------------------------------------------|--------|

| 1-3  | Logic Assembly Configuration Diagram                   | 1-9    |

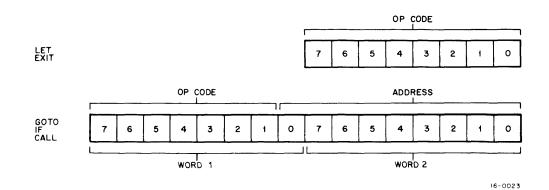

| 3-1  | Instruction Format                                     | 3-1    |

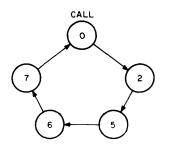

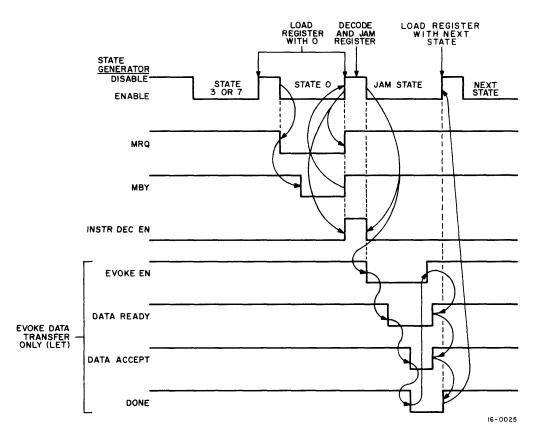

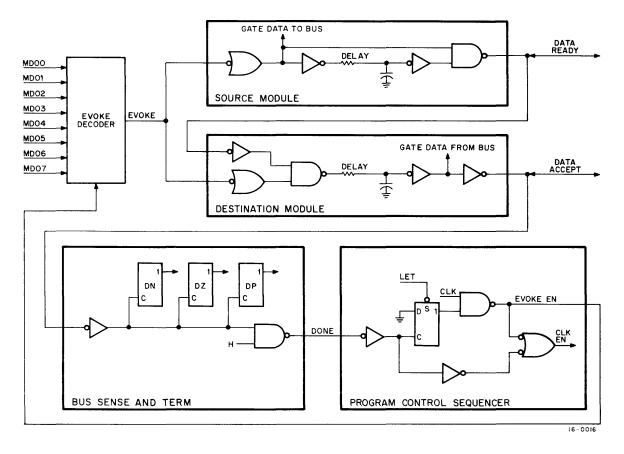

| 4-1  | Evoke Data Transfer Scheme                             | 4-2    |

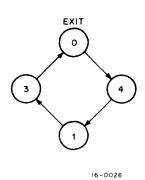

| 4-2  | Control Scheme                                         | 4-3    |

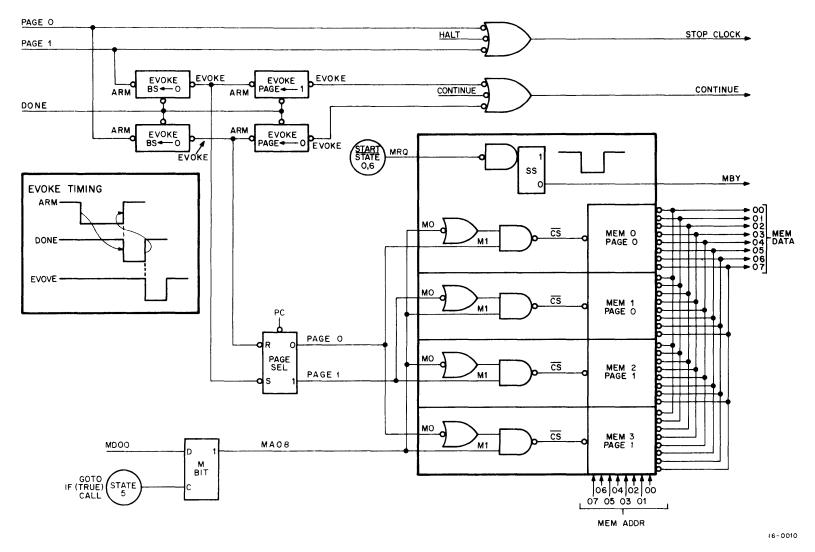

| 4-3  | Start, Clock, and Evoke Enable Logic                   | 4-15   |

| 4-4  | Instruction Decoder                                    | 4-16   |

| 4-5  | State Generator                                        | 4-17   |

| 4-6  | State Generator State Diagram                          | 4-17   |

| 4-7  | State Generator Timing Diagram                         | 4-18   |

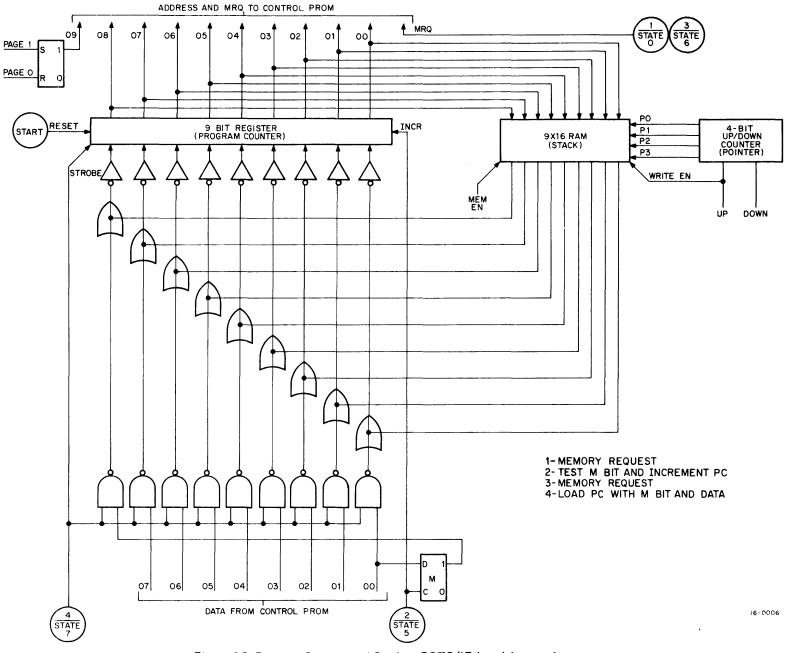

| 4-8  | Program Counter and Stack – LET Instruction            | 4-19   |

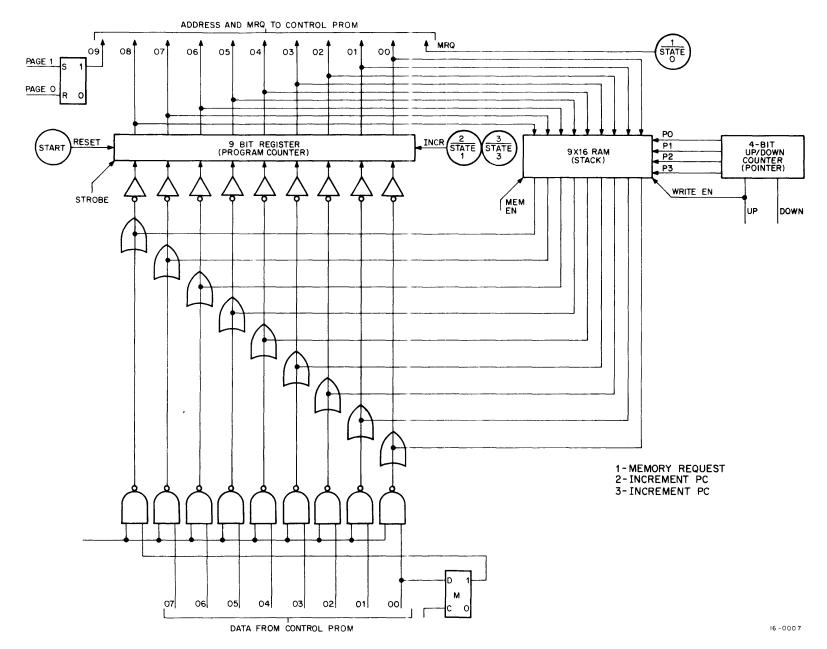

| 4-9  | Program Counter and Stack - GOTO/IF (true) Instruction | 4-20   |

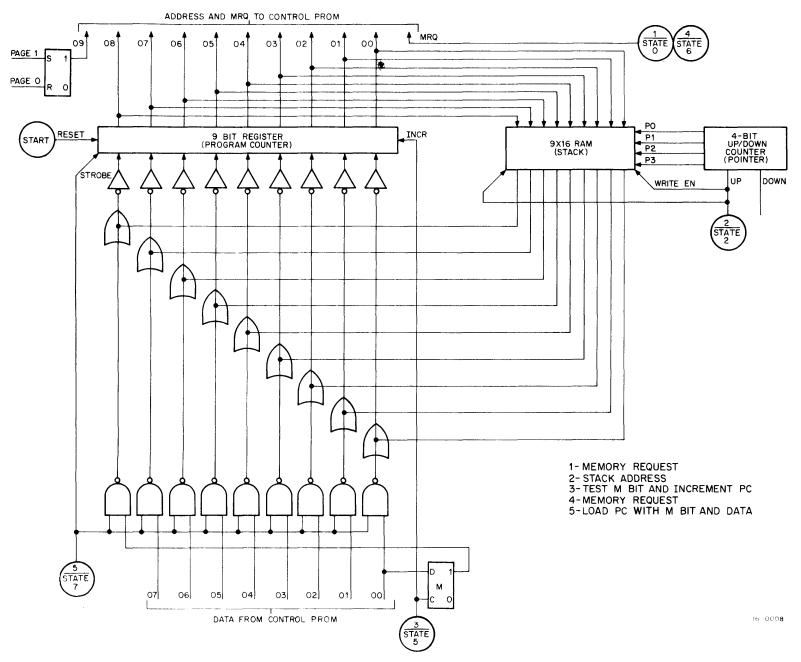

| 4-10 | Program Counter and Stack IF (not true) Instruction    | 4-21   |

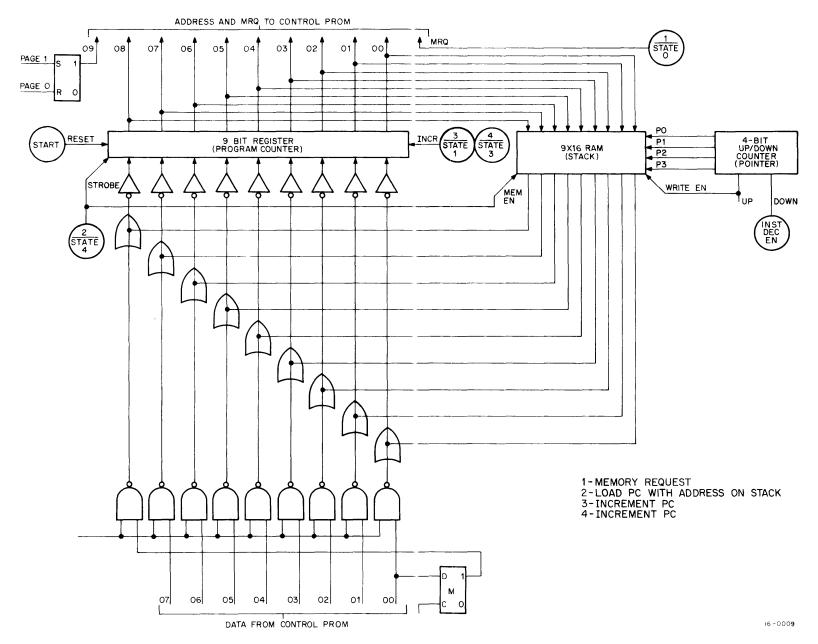

| 4-11 | Program Counter and Stack – CALL Instruction           | 4-22   |

| 4-12 | Program Counter and Stack – EXIT Instruction           | . 4-23 |

| 4-13 | Memory and Page Select Logic                           | . 4-24 |

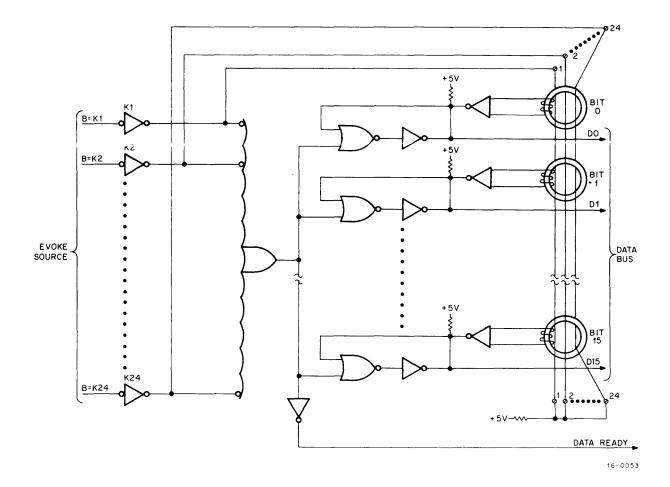

| 4-14 | Boolean Multiplexers                                   | . 4-25 |

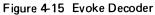

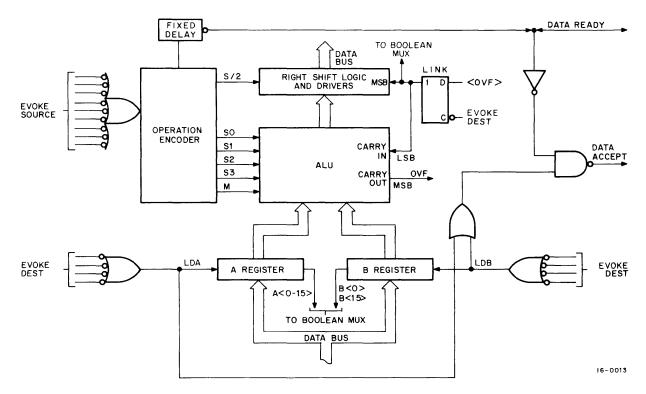

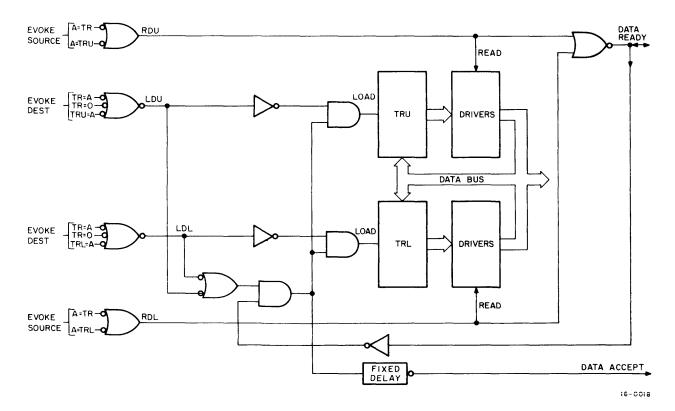

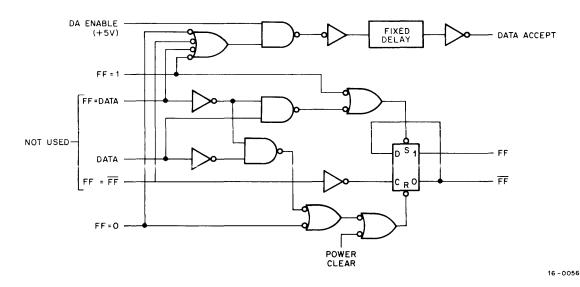

| 4-15 | Evoke Decoder                                          | . 4-25 |

| 4-16 | GPA Registers and Control                              | . 4-26 |

| 4-17 | Transfer Register                                      | . 4-26 |

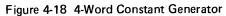

| 4-18 | 4-Word Constant Generator                              | . 4-27 |

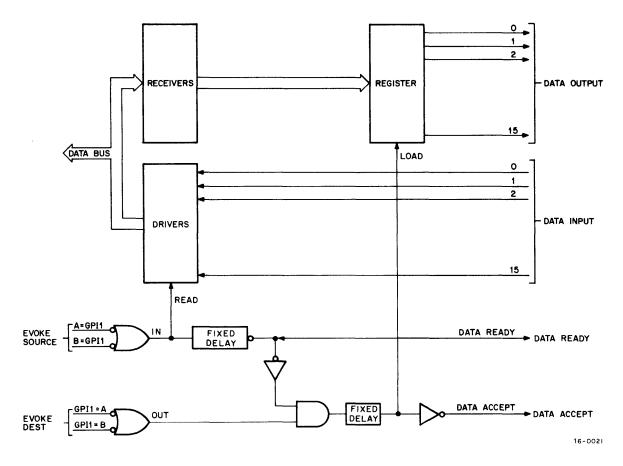

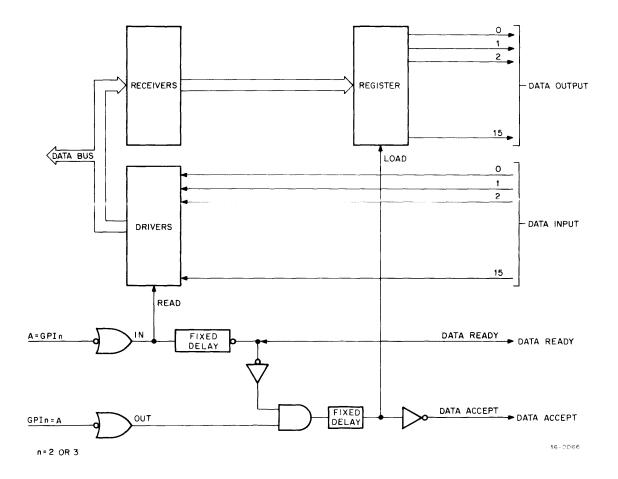

| 4-19 | General Purpose Interface                              | . 4-28 |

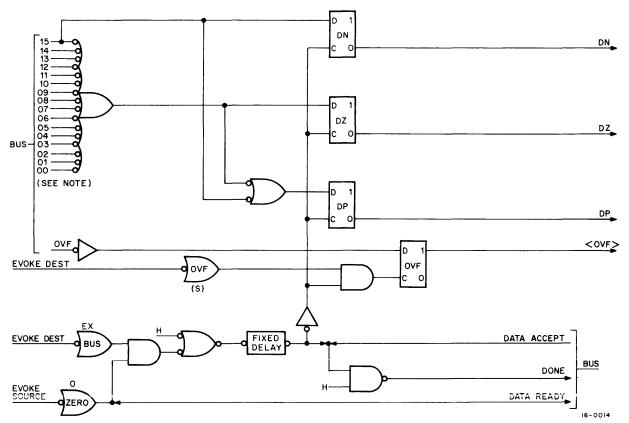

| 4-20 | Bus Sense and Termination Module                       | . 4-29 |

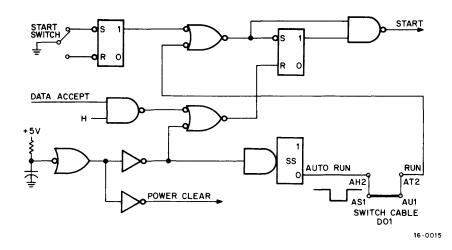

| 4-21 | Data Transfer Timing Logic                             | . 4-30 |

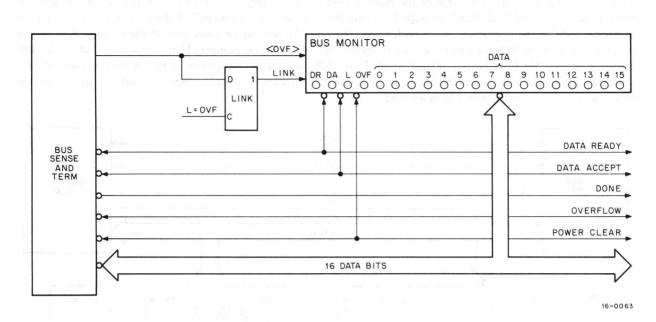

| 5-1  | Bus Monitor Module M7322, Application Diagram          | . 5-3  |

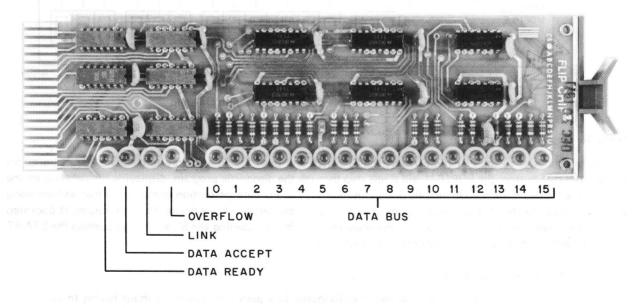

| 5-2  | Bus Monitor Module M7322                               | . 5-3  |

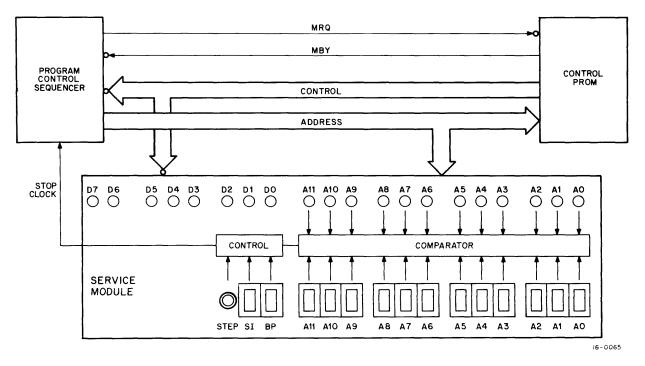

| 5-3  | Service Module M7335, Application Diagram              | . 5-4  |

| 5-4  | Service Module M7335                                   | . 5-5  |

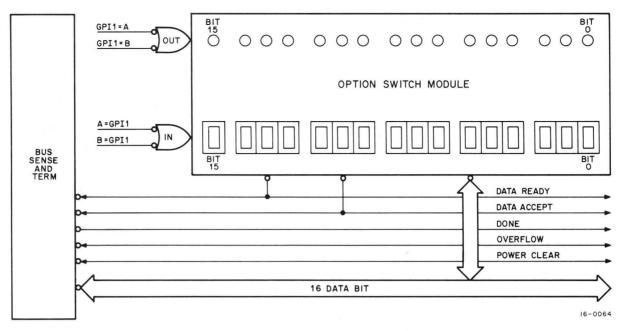

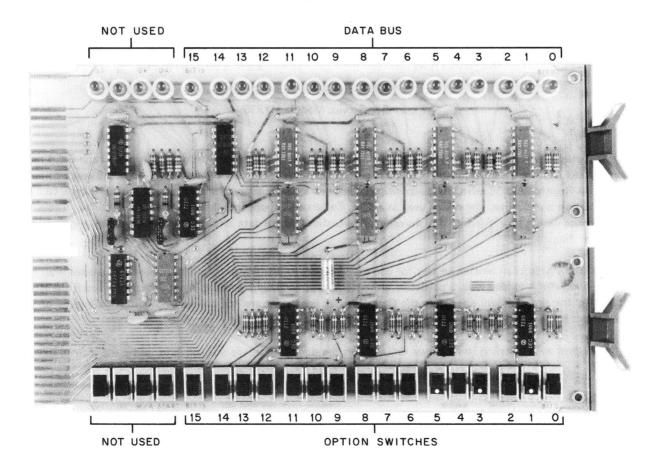

| 5-5  | Option Switch Module M7334, Application Diagram        | . 5-6  |

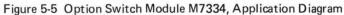

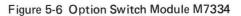

| 5-6  | Option Switch Module M7334                             | . 5-6  |

| 5-7  | Logic Assembly Maintenance Configuration Diagram       | . 5-9  |

| 5-8  | Repair Procedure Flow Diagram                          | . 5-12 |

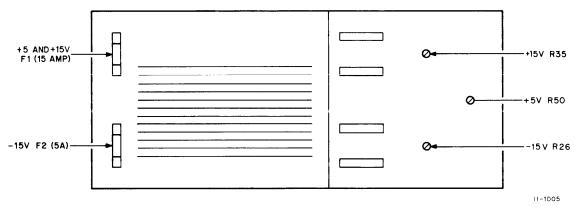

| 5-9  | H740 Power Supply Fuses and Adjustment Controls        |        |

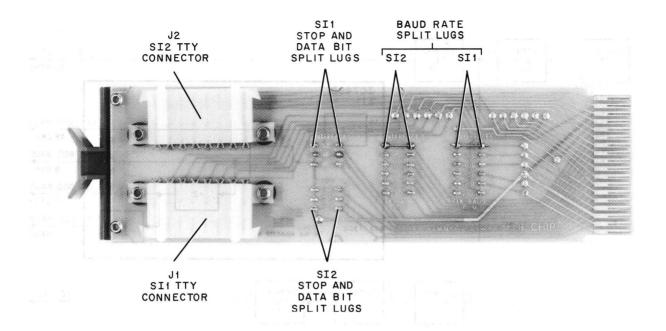

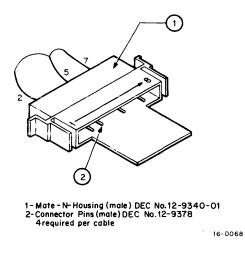

| B-1  | Serial I/O Jumper Plug                                 | . В-З  |

## TABLES

#### Table No.

#### Title

Page

| 1-1 | Module Slot Assignment and Description |

|-----|----------------------------------------|

| 1-2 | Configuration Data                     |

| 2-1 | DC Voltages                            |

| 2-2 | Diagnostic Option Select Switches      |

| 4-1 | State Table                            |

| 4-2 | Boolean Multiplexers Input 4-8         |

| 4-3 | GPA Units Operations Summary 4-9       |

| 4-4 | Basic PDP16-M Registers and Functions  |

| 5-1 | PDP16-M Field Service Repair Kit       |

| 5-2 | Option Diagnostic Key                  |

## **TABLES** (Cont)

Page

| 5-3 | Preventive Maintenance Schedule (3 months or 500 hours) |

|-----|---------------------------------------------------------|

| 5-4 | DC Voltages                                             |

| C-1 | PDP16-M I/O Slot Pin Assignments (By Signal Name)       |

| C-2 | PDP16-M Data Bus Pin Assignments (By Signal Name)       |

| C-3 | PDP-11 Unibus Pin Assignments (By Signal Name) C-5      |

.

## FOREWORD

All information necessary to service and maintain the PDP16-M minicomputer is contained in this manual. The manual contains five chapters and four appendices:

Chapter 1 provides a general functional and physical description of the PDP16-M and its options. Specifications and configuration data are also detailed in this chapter.

Chapter 2 contains installation and checkout procedures. The basic diagnostic and all relevent option diagnostic programs are performed after installation to verify that the PDP16-M is operating properly.

Chapter 3 covers operating and programming details. In addition to the operating information, a complete description of the basic instruction set for the PDP16-M is included. Instructions that are implemented through options are detailed in the appropriate option descriptions (Appendix A).

Chapter 4 contains the theory of operation of the basic PDP16-M. Theory of operation for the options is included in the appropriate option description (Appendix A).

Chapter 5 provides maintenance information. All optional maintenance modules and programs are described in this chapter. Procedures for performing corrective maintenance are also included in this chapter.

Appendix A contains the option descriptions. Each option description provides a general description of the option, installation details, programming information, and theory of operation.

Appendix B presents details on building jumper modules and plugs that will facilitate maintenance and testing.

Appendix C is an alphabetic listing of PDP16-M and PDP-11 bus and I/O signals.

Appendix D lists all PDP16-M instruction machine codes, execution times, and mnemonics.

## CHAPTER 1 GENERAL INFORMATION

#### **1.1 INTRODUCTION**

The PDP16-M is a programmable minicomputer with built-in flexibility for memory and I/O expansion. It can be used as a stand-alone controller or as a subprocessor in a larger system.

A prewired mainframe facilitates expansion of control memory, data memory, and I/O options simply by inserting the appropriate option module in its assigned slot. Insertion slots are also reserved on the mainframe for standard I/O interfacing cables and PDP16-M maintenance options. The application program is stored in a control PROM which can be reprogrammed at least 100 times. Once a PROM is loaded and installed in a PDP16-M, the machine exhibits the characteristics of a dedicated controller. However, the PROM can be reloaded with a different application program and/or a different application PROM can be installed in the PDP16-M. This feature permits the PDP16-M to be used not only as a dedicated controller, but as a general purpose controller, monitor, or preprocessor.

Application programs can be written for virtually any kind of application within the range of the arithmetic, logic, memory, and I/O capabilities of the PDP16-M. Data logging, waveform analysis, data format and media conversion, preprocessing, and postprocessing are some applications for which a PDP16-M can be implemented.

#### **1.2 FUNCTIONAL DESCRIPTION**

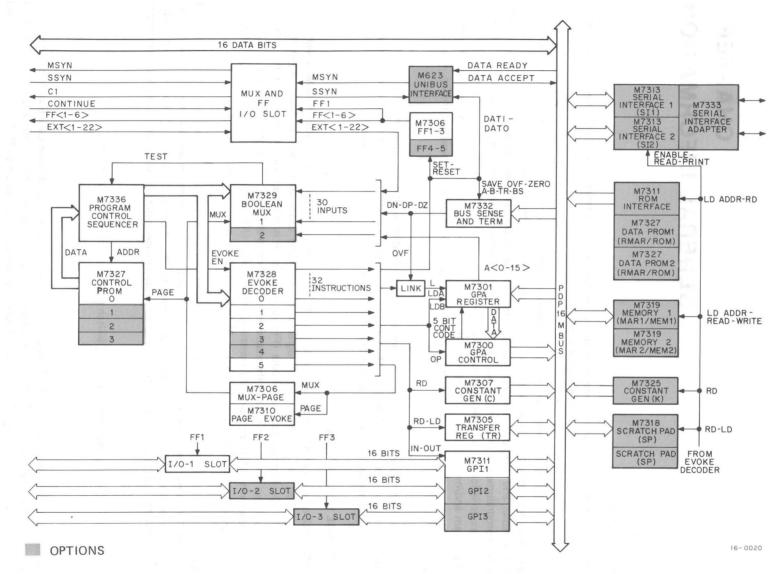

The basic PDP16-M consists of a general purpose arithmetic unit (GPA), 256-location control PROM, a high speed transfer register, a 16-bit I/O interface, three programmable flip-flops (Boolean outputs or flags), a 4-word data constant ROM, and six external Boolean inputs (Figure 1-1). Space is reserved within the chassis for prewired memory and I/O options which can expand the machine to 1K of control PROM, 33 registers, 256, 512, 1K, 1.25K or 2K of 16-bit read-write MOS memory, 28 constants, three 16-bit I/O interfaces, two serial I/O interfaces, six programmable flip-flops, a 256-word 8- or 16-bit data PROM, and 22 external Boolean inputs.

The control program is stored in a semiconductor PROM which may be erased and reloaded using ultraviolet light and a special PROM loader interface. Data constants used by the control program are not stored in the control memories. They are stored in either a high speed 4-word ROM, 24-word ROM or a 256-word 8- or 16-bit semiconductor PROM. This feature allows the data to be easily changed without having to reprogram the control memories.

The program may be started by the front panel start switch or by auto start after power on.

#### 1.2.1 Control

The programmable control section of the PDP16-M generates all control signals that cause data transfers and execute the instructions stored in the control PROMs. It includes a control module, a control memory (expandable to 4), 4 evoke decoders (expandable to 6), and a 30-channel Boolean multiplexer (expandable to 2). The control section also contains a 16-level automatic hardwired subroutine push down stack. The CALL and EXIT instructions control the stack operations.

Figure 1-1 PDP16-M Minicomputer, Block Diagram

3

€,

1-2

The control section of the PDP16-M consists of the following modules: