Digital Equipment Corporation Maynard, Massachusetts

digital

PDP-8 Maintenance Manual

# KV GRAPHIC DISPLAY SYSTEM

DEC-8I-H6MA-D

# PDP-8 KV GRAPHIC DISPLAY SYSTEM MAINTENANCE MANUAL

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

APRIL 1970

Copyright 1970 © by Digital Equipment Corporation

The following are registered trademarks of Digital Equipment Corporation, Maynard Massachusetts:

DEC FLIP CHIP DIGITAL

PDP FOCAL COMPUTER LAB

### TABLE OF CONTENTS

| Chapter |

|---------|

|---------|

3

| apt | er                     |                                                                                                       | Page       |

|-----|------------------------|-------------------------------------------------------------------------------------------------------|------------|

| 1   |                        | GENERAL INFORMATION                                                                                   |            |

|     | 1.1<br>1.2             | General                                                                                               |            |

|     | 1.3                    | Basic System Description                                                                              | . 1-1      |

|     |                        | 1.3.1       KV Controller         1.3.2       Type VT01 Storage Tube Display Unit                     |            |

|     |                        | 1.3.2Type VT01 Storage Tube Display Unit                                                              |            |

|     |                        | 1.3.4     Model 33 Automatic Send-Receive Keyboard                                                    |            |

|     | 1.4                    | Options                                                                                               |            |

|     |                        | 1.4.1Multiplex Interface Option                                                                       |            |

|     |                        | 1.4.2       Type RVGT Graphic Display Unit         1.4.3       VS08 Storage Tube Controller Interface |            |

|     | 1.5                    | Accessory Equipment                                                                                   |            |

|     |                        | 1.5.1 Hardware                                                                                        | . 1-5      |

|     | 1.6                    | 1.5.2 Software                                                                                        | . 1-5      |

|     | 1.0                    | Specifications                                                                                        | . 1-5      |

| 2   |                        | INSTALLATION                                                                                          |            |

|     | 2.1                    | General                                                                                               | . 2-1      |

|     |                        | 2.1.1 Power Requirements                                                                              |            |

|     |                        | 2.1.2 Space Requirements                                                                              |            |

|     |                        | 2.1.3 Environmental Considerations                                                                    |            |

|     | 2.2                    | Unpacking                                                                                             |            |

|     | 2.3                    | Modification Data                                                                                     |            |

|     |                        | - Torre                                                                                               |            |

|     | 2.4                    |                                                                                                       |            |

|     | 2.4                    | Installation and Checkout                                                                             |            |

|     |                        | 2.4.1       Installation                                                                              |            |

| ~   |                        |                                                                                                       | . 2-5      |

| 3   |                        | OPERATION AND PROGRAMMING                                                                             |            |

|     |                        | Section I Operation                                                                                   |            |

|     | 3.1                    | General                                                                                               | . 3-1      |

|     | 3.2                    | Operating Controls                                                                                    |            |

|     |                        | Section II Programming                                                                                |            |

|     | 3.3                    | General                                                                                               | <b>a</b> t |

|     | 3.3<br>3.4             |                                                                                                       |            |

|     | 3. <del>4</del><br>3.5 | Display Capabilities                                                                                  |            |

|     | 5.5                    | The Oscilloscope Display                                                                              | . 3-5      |

|     |                        |                                                                                                       | . 3-5      |

|     |                        | 3.5.2 Visible Image Area                                                                              | . 3-5      |

### TABLE OF CONTENTS (cont)

### Chapter

4

| 3.6  | 3.5.4Circle-Drawing Capabilities                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|      | PRINCIPLES OF OPERATION                                                                                                                       |

|      | Section I Fundamentals of Operational Amplifiers                                                                                              |

| 4.1  | Operational Amplifiers                                                                                                                        |

| 4.2  | Field-Effect Transistors                                                                                                                      |

| 4.3  | Sample and Hold                                                                                                                               |

|      | Section II System Analysis                                                                                                                    |

| 4.4  | General                                                                                                                                       |

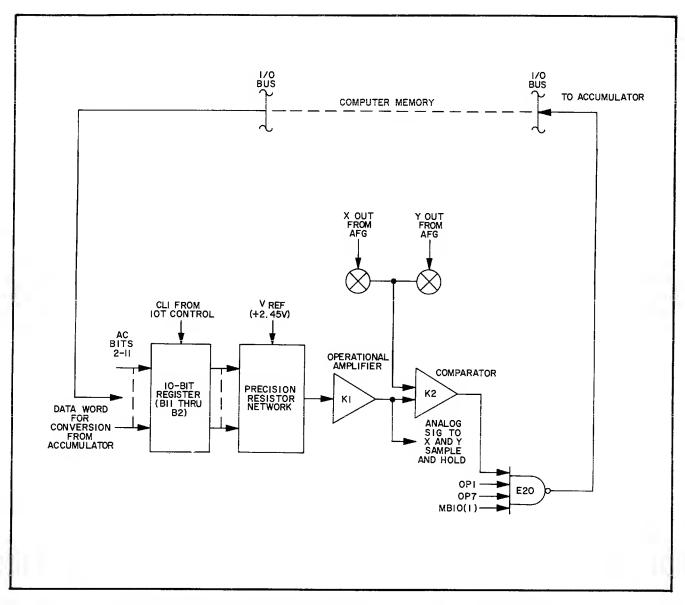

|      | Conversion Facilities                                                                                                                         |

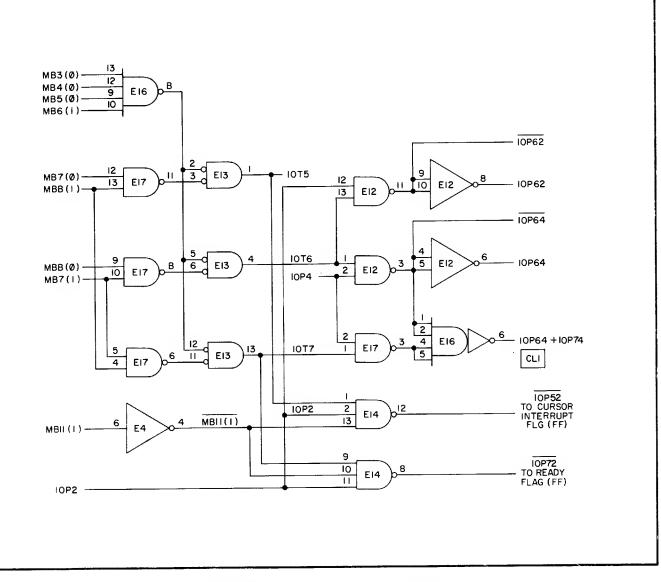

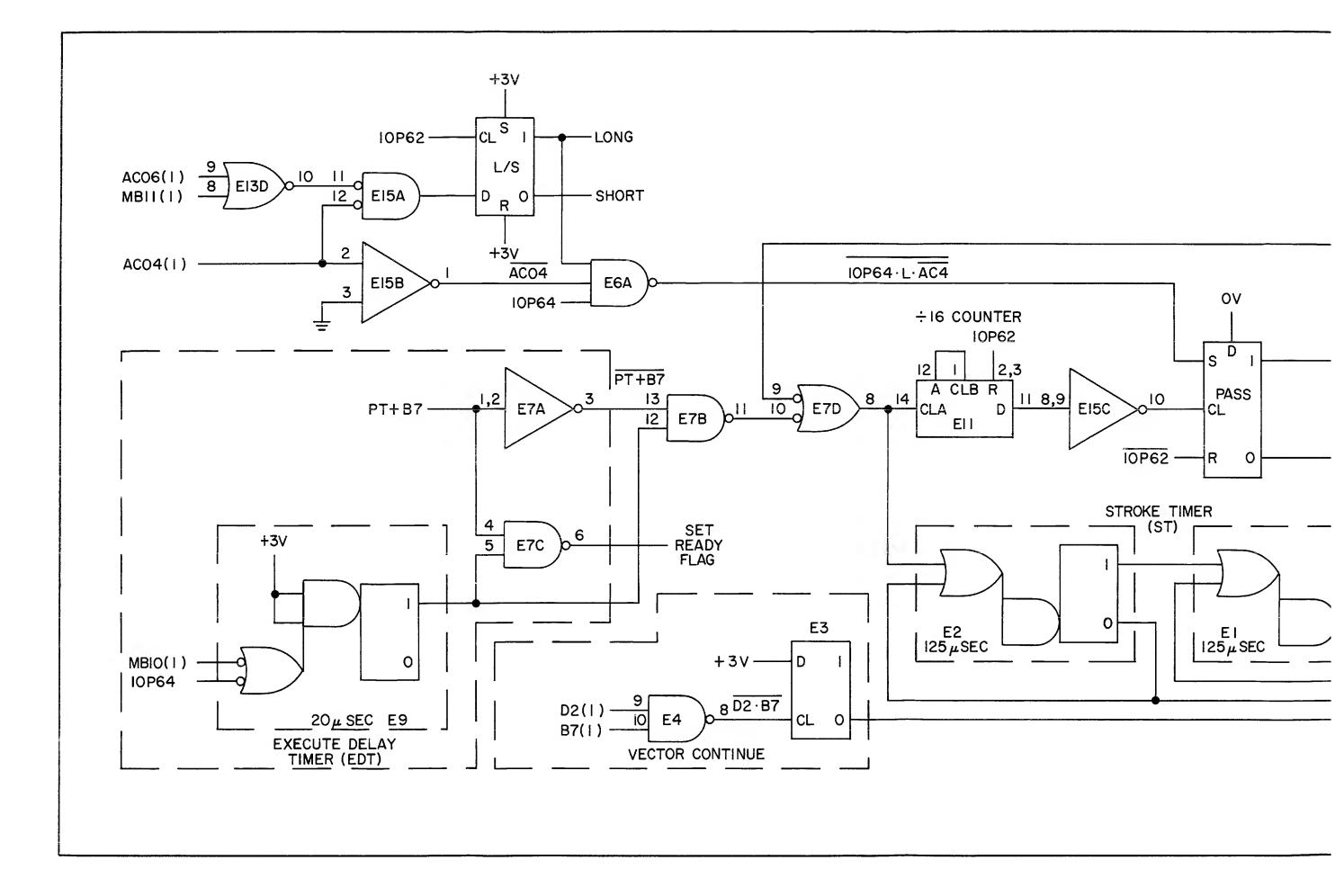

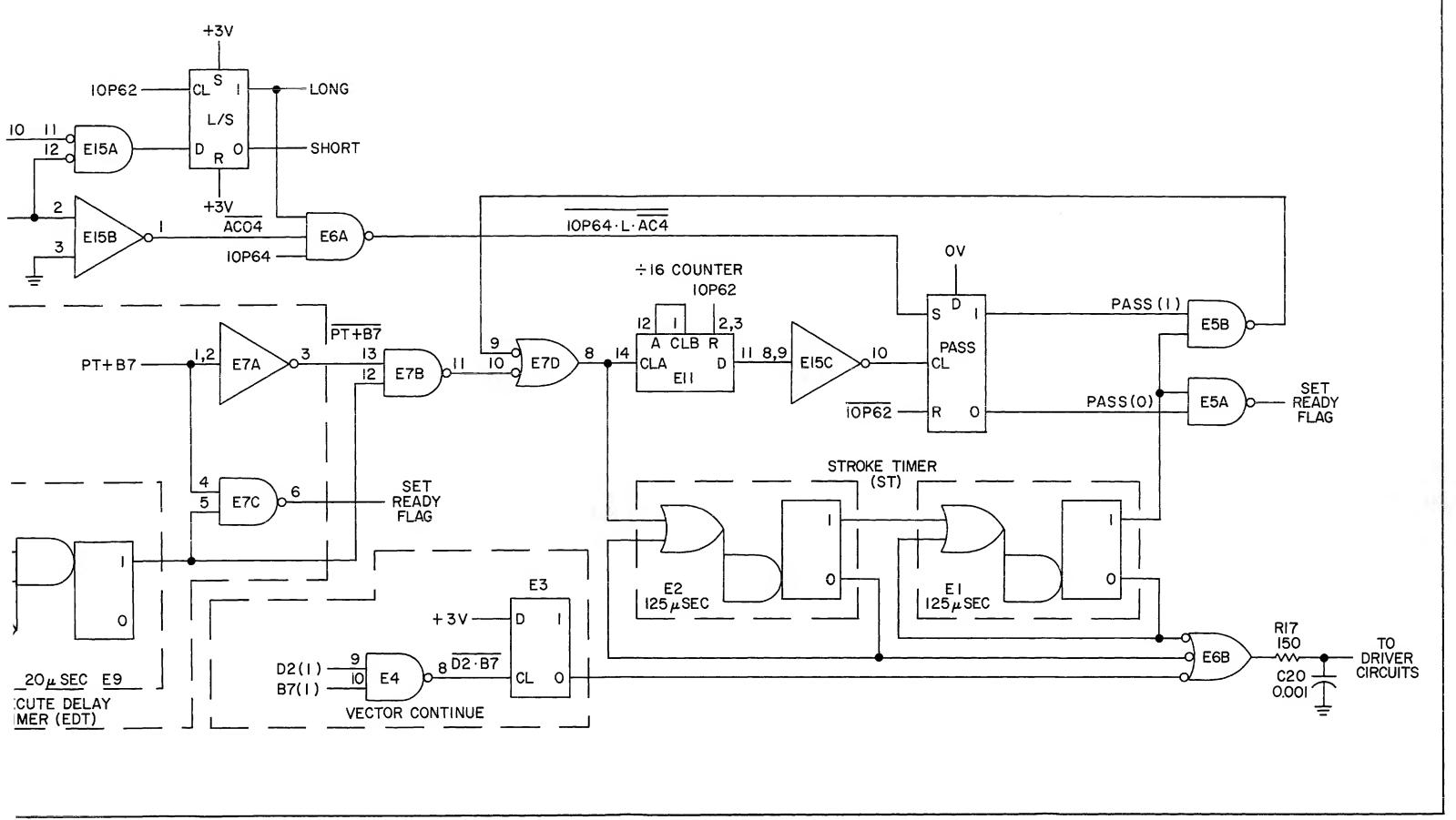

| 4.5  | Control Circuits4-94.5.1Input/Output Transfer Control4-94.5.2Skip and Interrupt Control Facilities4-12                                        |

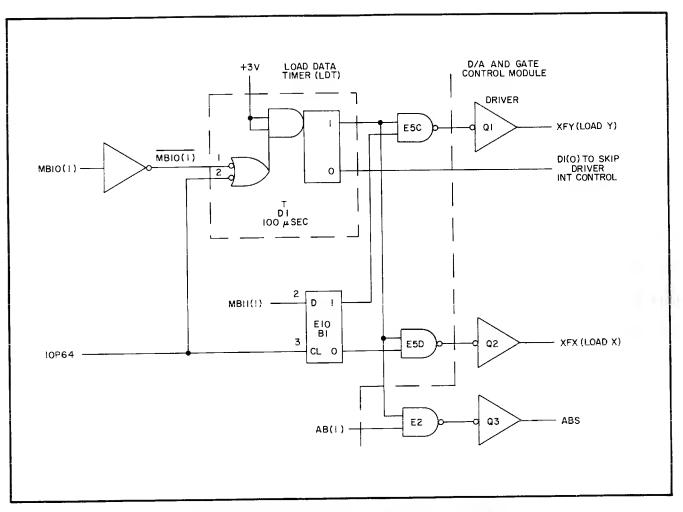

| 4.6  | Timing Circuits4-124.6.1Load Data Timer4-124.6.2Execute Delay Timer4-124.6.3Long and Short Vector Timing Circuit4-12                          |

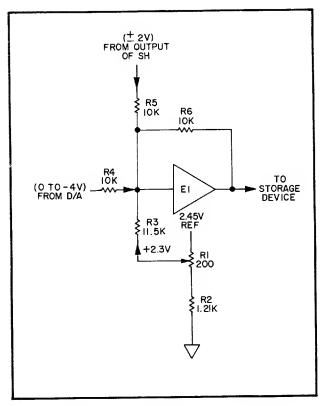

| 4.7  | Digital-to-Analog and Analog-to-Digital Conversions4-144.7.1Digital-to-Analog Converter4-144.7.2Analog-to-Digital Converter4-14               |

| 4.8  | Sample and Hold                                                                                                                               |

| 4.9  | Integrators                                                                                                                                   |

| 4.10 | Output Drivers         4-18                                                                                                                   |

| 4.11 | Modes of Operation                                                                                                                            |

|      | 4.11.1 Point Mode                                                                                                                             |

|      | 4.11.2 Vector Mode       4-18         4.11.3 Cursor Mode       4-21                                                                           |

| 4-12 | 4.11.3 Cursor Mode       4-21         Power Supplies       4-21                                                                               |

| 4-12 | $-10 \text{ were supplied} \dots \dots$ |

## TABLE OF CONTENTS (cont)

Page

### Chapter

| 5   | MAINTENANCE                                            |

|-----|--------------------------------------------------------|

|     | Section I Introduction                                 |

| 5.1 | Warranty                                               |

|     | 5.1.1 Modules and Accessories                          |

|     | 5.1.2 Shipping                                         |

|     | 5.1.3 Systems 5.2                                      |

| 5.2 | 5.1.4 Other Warranty Conditions $\ldots$ 5.2           |

| 5.2 | Service Policy $\dots$ $5-2$                           |

| 5.3 | Maintenance Concept                                    |

|     | Section II System Maintenance                          |

| 5.4 | Preventive Maintenance                                 |

|     | 5.4.1 General                                          |

|     | 5.4.2 Mechanical Inspection                            |

|     | 5.4.3 Diagnostic Testing and Minimum Performance Tests |

| 5.5 | Trouble Analysis                                       |

|     | 5.5.1 Power Supply $\ldots \ldots 5-4$                 |

|     | 5.5.2 Analog Faults                                    |

|     | 5.5.3 Joystick Controller                              |

|     | 5.5.4 Component Part                                   |

| 5.6 | Alignment and Alighter t                               |

| 5.0 | Alignment and Adjustment                               |

|     |                                                        |

| 5.7 |                                                        |

|     | Repair and Replacement                                 |

| 6   | REPAIR PARTS LISTS                                     |

7 DIAGRAMS

#### LIST OF ILLUSTRATIONS

| Figure   | Title                                                                                        | Page         |

|----------|----------------------------------------------------------------------------------------------|--------------|

|          | Type KV Graphic Display System         KV Graphic Display System                             |              |

| 1-1      | KV Controller, Simplified Block DiagramType VT01 Storage Tube Display Unit                   | 1-2          |

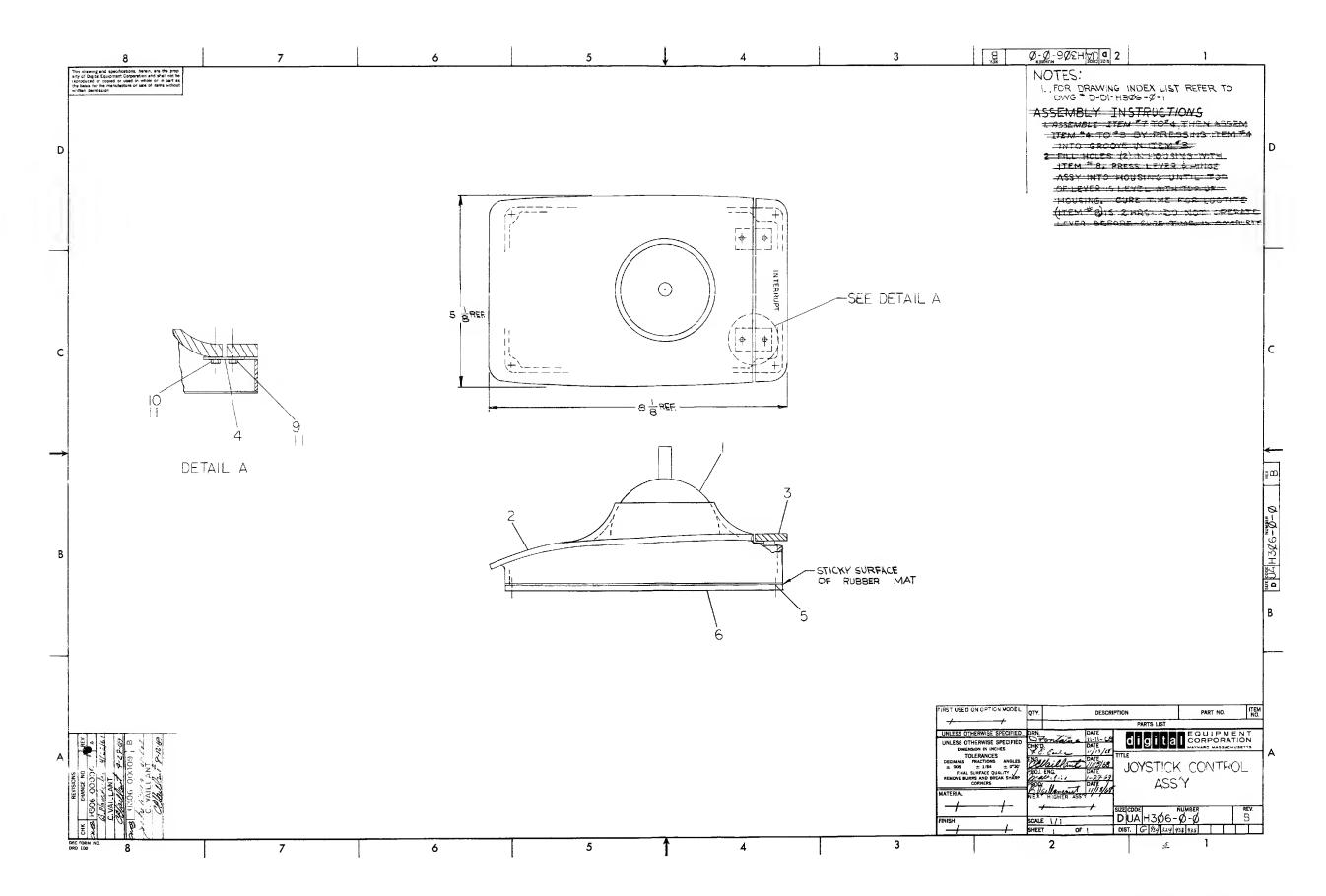

| 1-2      | Type H306 Joystick Control                                                                   |              |

| 1-3      | Type ASR-33 Teletype Keyboard                                                                |              |

| 1-4      | Type KVGT Graphic Display Unit                                                               |              |

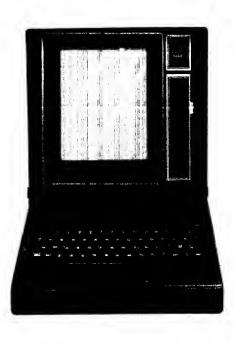

| 1-5      | Storage Tube Display Unit Overall Dimensions and                                             | . 1 1        |

| 2-1      | Location of Remote Programming Connector                                                     | . 2-1        |

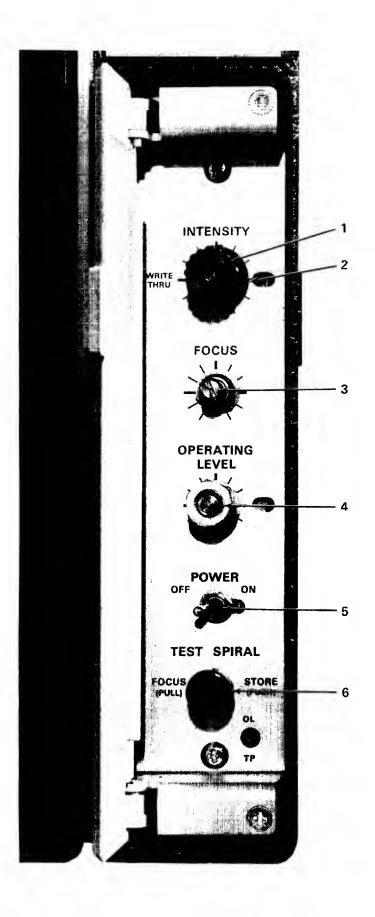

| 3-1      | Storage Tube Display Unit VT01, Location of Controls and Indicators                          | . 3-2        |

| 3-2      | Effective and Visible Image Areas                                                            | . 3-5        |

| 3-3      | Specification of Start and End Linear Vectors                                                |              |

| 3-4      | Specification of Center, Start and Circumference of                                          |              |

| 5 1      | Circular Vectors                                                                             | . 3-8        |

| 3-5      | Basic IOT Instruction Format                                                                 |              |

| 3-6      | Typical Coordinate Reference System for Machine                                              |              |

|          | Language Programming                                                                         | 3-15         |

| 3-7      | Basic Data-Word Format                                                                       | 3-16         |

| 3-8      | Basic Parameter-Word Formats                                                                 | 3-17         |

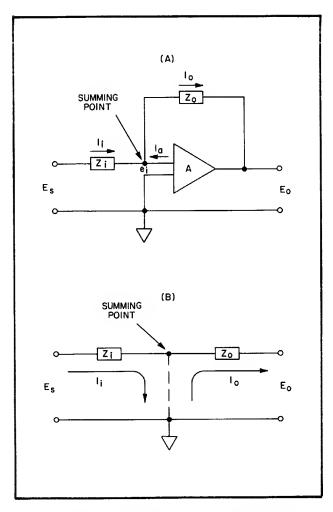

| 4-1      | Basic Operational Amplifier, Idealized                                                       | . 4-2        |

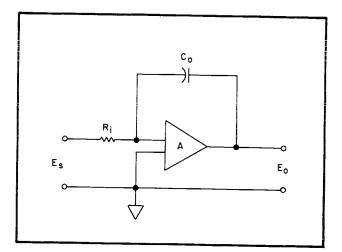

| 4-2      | Integrator, Basic Configuration                                                              | . 4-3        |

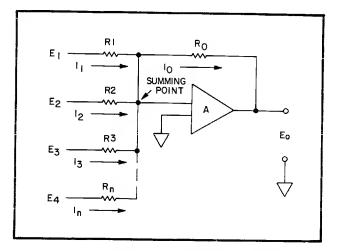

| 4-3      | Scaling Adder, Basic Configuration                                                           | . 4-3        |

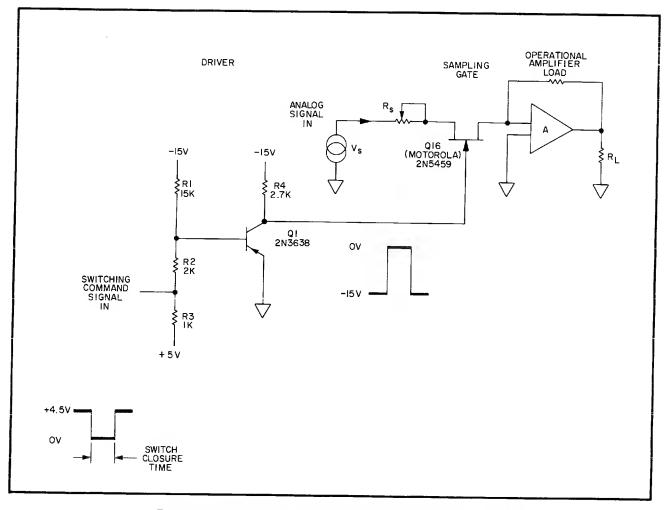

| 4-4      | Typical KV Controller, FET Switching Circuit With Driver                                     | . 4-5        |

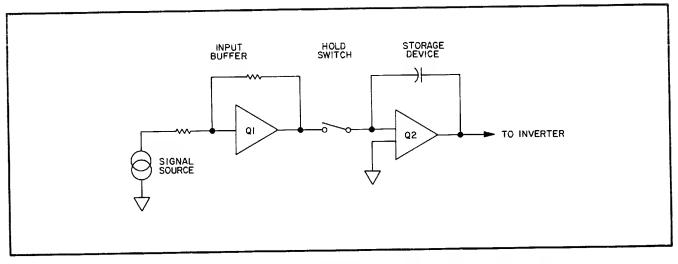

| 4-5      | Sample and Hold Register, Simplified Schematic Diagram                                       | . 4-6        |

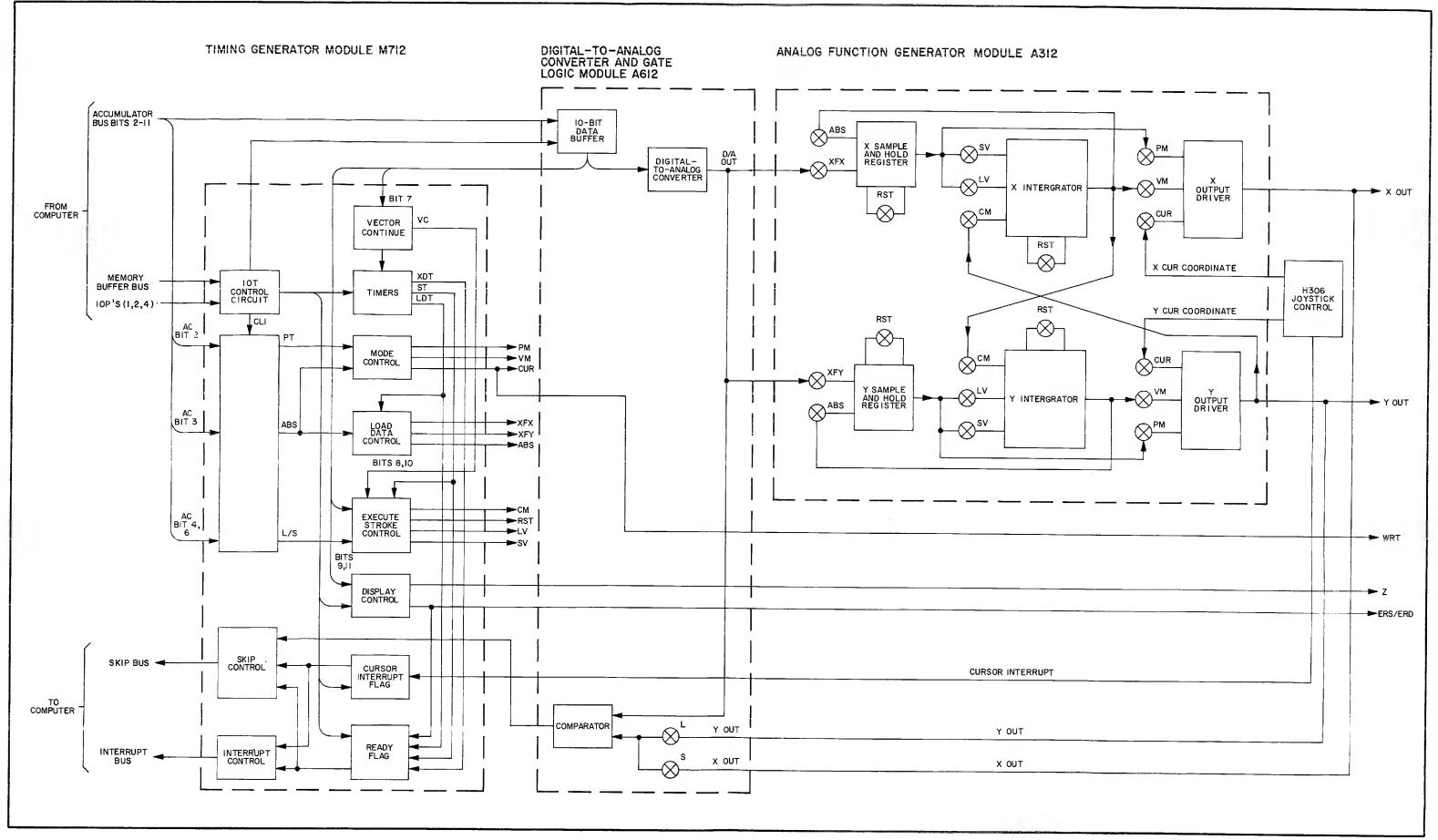

| 4-6      | KV Controller, Functional Block Diagram                                                      | . 4-7        |

| 4-7      | IOT Control Circuit, Logic Diagram                                                           |              |

| 4-8      | IOP Timing Diagram                                                                           |              |

| 4-9      | Load Data Timer (LDT), Simplified Logic Diagram                                              | 4-13         |

| 4-10     | Execute Data Timer, Long/Short Vector and Vector Continue Timing                             |              |

|          | Circuit, Simplified Logic Diagram                                                            | 4-15         |

| 4-11     | Digital-to-Analog/Analog-to-Digital Converter,                                               |              |

|          | Functional Block Diagram                                                                     | 4-17         |

| 4-12     | Sample and Hold Register Input Buffer, Simplified                                            | 1 1 0        |

|          | Schematic Diagram                                                                            | 4-18         |

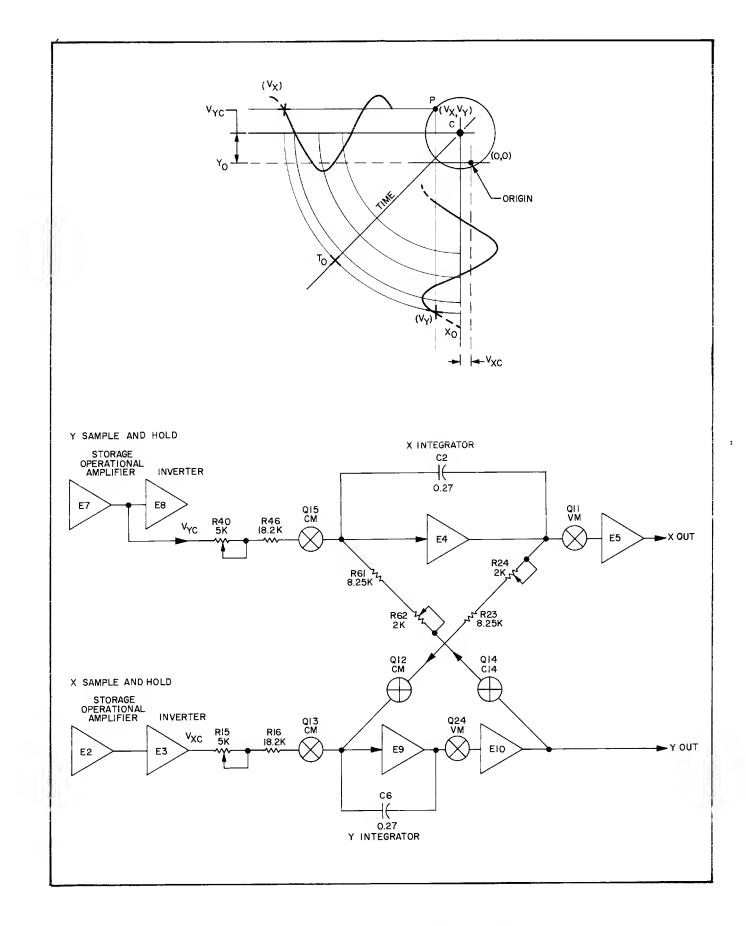

| 4-13     | Analog Function Generator In Circle Mode Configuration                                       | 1 10         |

|          | and Circle Generation Geometry                                                               | 4-19         |

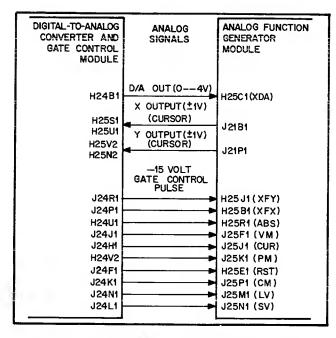

| 5-1      | Digital-to-Analog Converter and Gate Logic Module/Analog                                     | 55           |

| <u> </u> | Function Generator Module Interface                                                          |              |

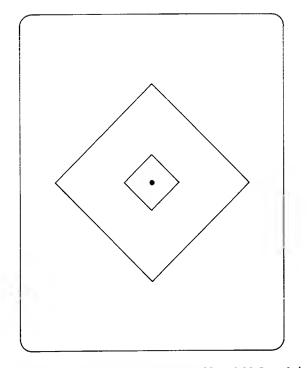

| 5-2      | Circle Mode Zero and X and Y Sample/Hold Zero Adjustment Display Pattern                     |              |

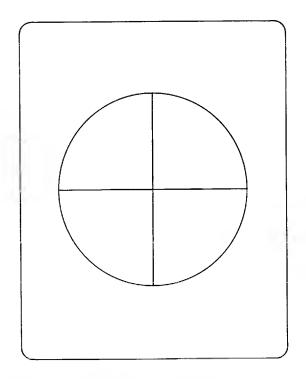

| 5-3      | Circle Mode Rate, Adjustment Display Pattern                                                 | . 3-7        |

| 5-4      | Stroke Timing Generator, Adjustment Display Pattern                                          | . 5-7        |

| 5-5      | Absolute Vector, Adjustment Display Pattern                                                  | . J-0<br>5_2 |

| 5-6      | Circle Mode Center Gain, Adjustment Display Pattern                                          | - 5-0<br>5_0 |

| 5-7      | Short Vector Gain, Adjustment Display Pattern                                                | . J-9<br>5_0 |

| 5-8      |                                                                                              | . 5-9        |

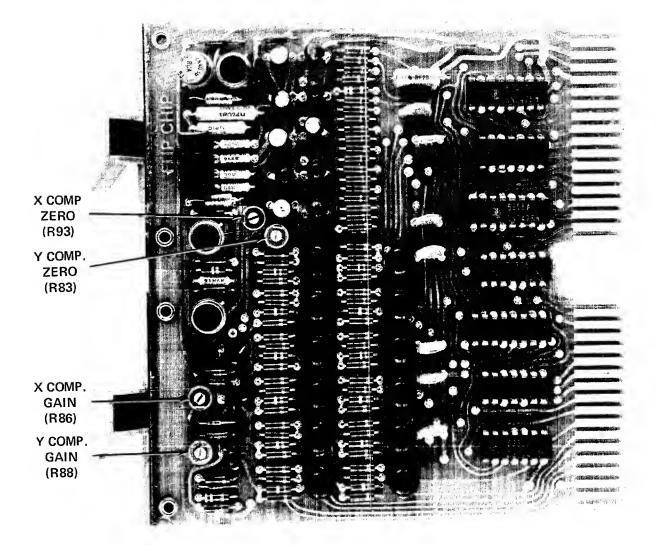

| 5-9      | Digital-to-Analog Converter and Gate Logic Module A612,<br>Adjustable Parts Location Diagram | 5-14         |

### LIST OF ILLUSTRATIONS (cont)

| Figure | Title                                                      | Page         |

|--------|------------------------------------------------------------|--------------|

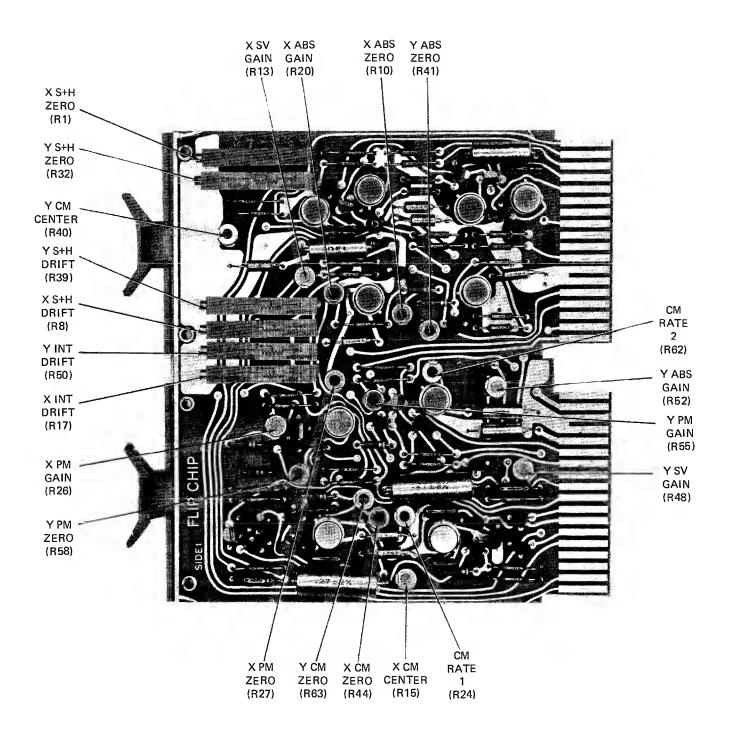

| 5-10   | Analog Function Generator Module A312, Adjustable          |              |

|        | Parts Location Diagram                                     | . 5-15       |

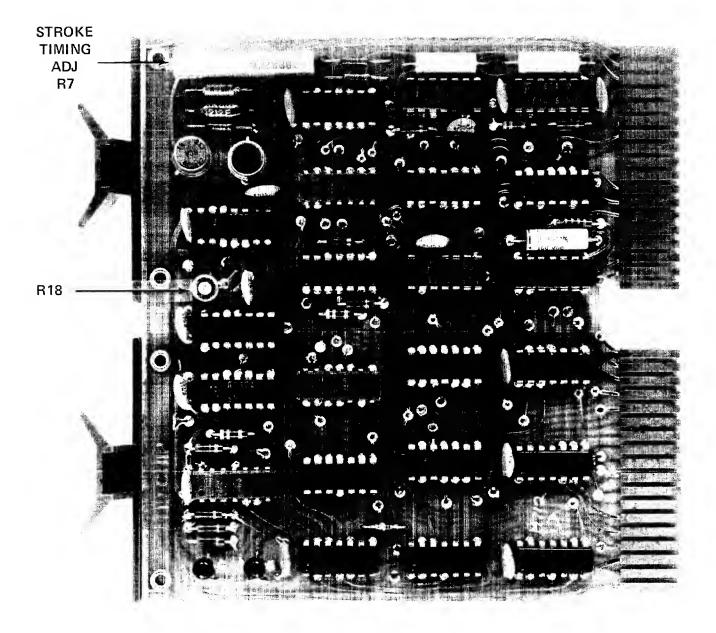

| 5-11   | Timing Generator Module M712, Adjustable Parts             | 10           |

|        | Location Diagram                                           | . 5-16       |

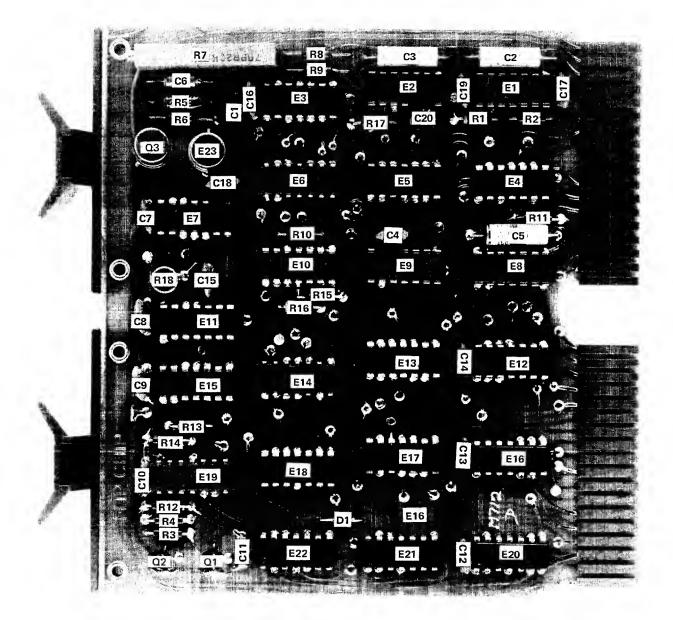

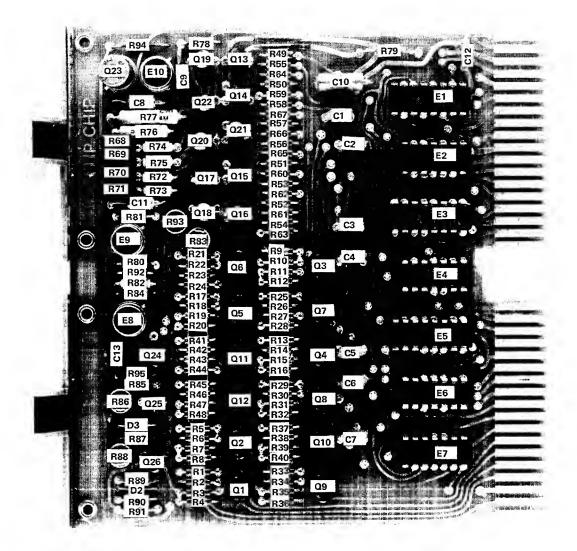

| 6-1    | Timing Generator Module M712, Parts Location Diagram       | 6-2          |

| 6-2    | Digital-to-Analog Converter and Gate Logic Module A612,    |              |

|        | Parts Location Diagram                                     | 6 <b>-</b> 6 |

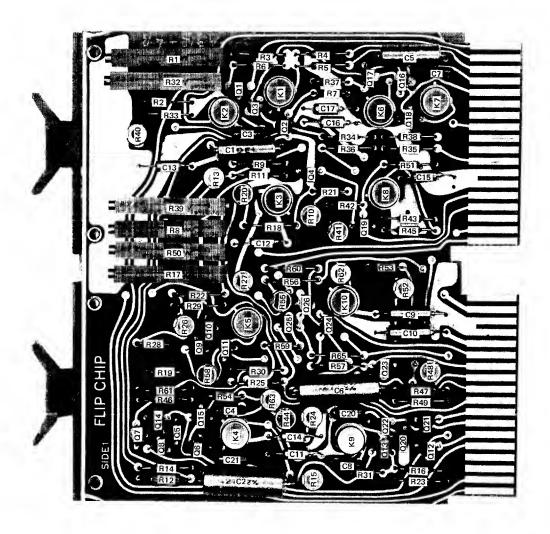

| 6-3    | Analog Function Generator Module A312, Parts               |              |

|        | Location Diagram                                           | . 6-10       |

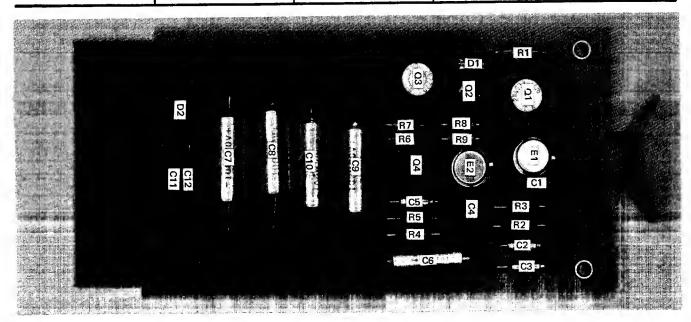

| 6-4    | Voltage Regulator Module, Parts Location Diagram           | 6-13         |

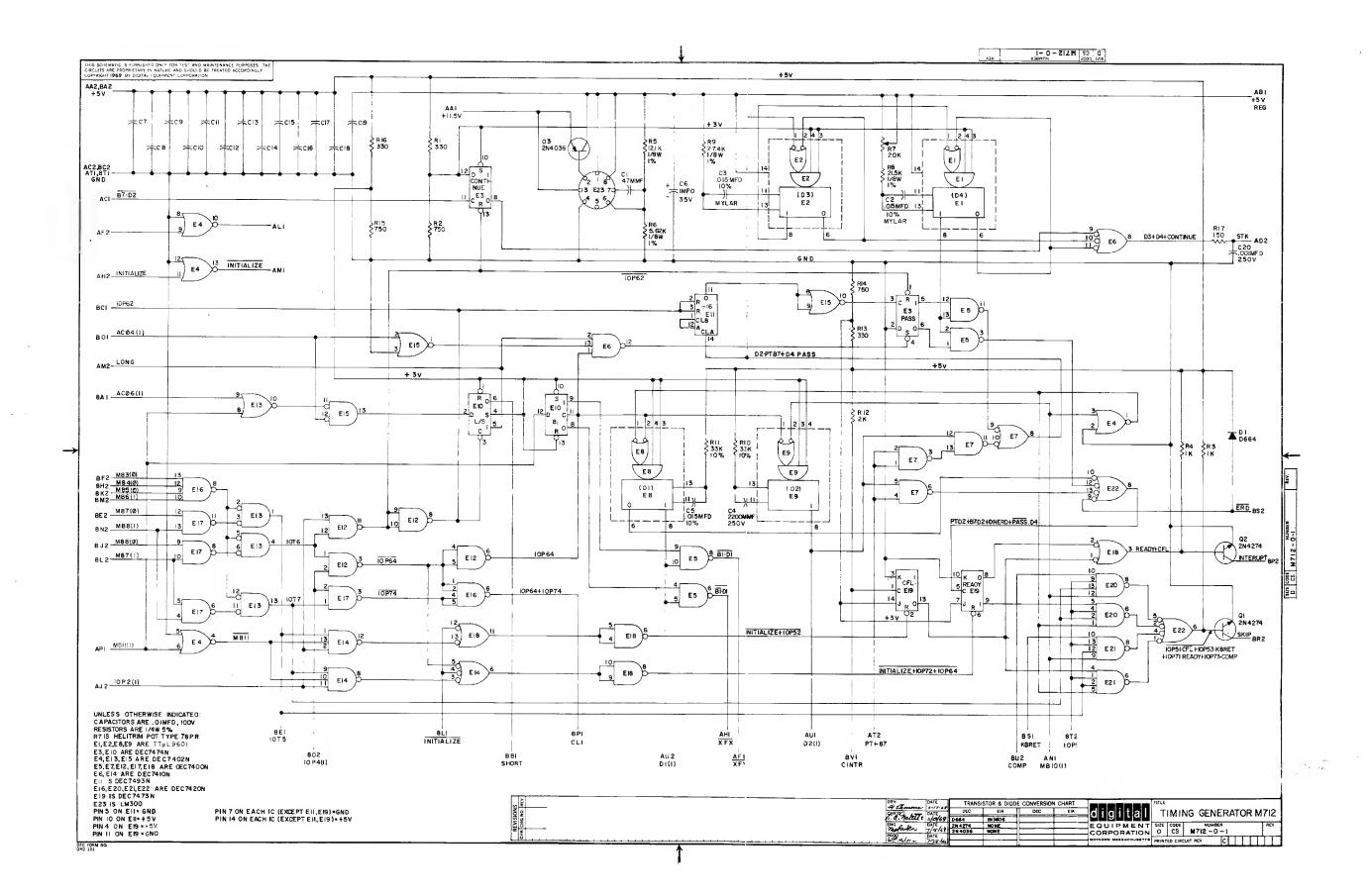

| 7-1    | Timing Generator Module M712, Schematic Diagram            |              |

|        | M712-0-1                                                   | 7-3          |

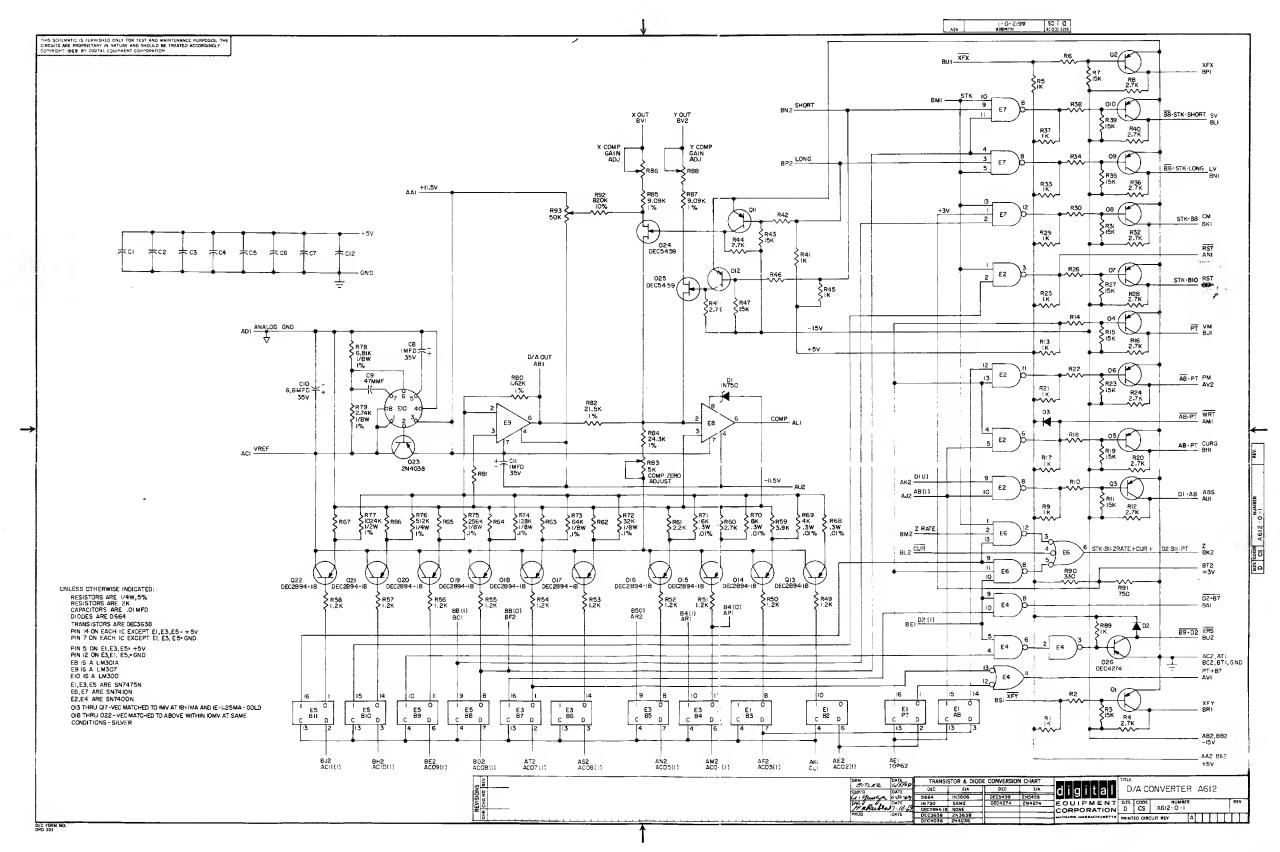

| 7-2    | Digital-to-Analog Converter and Gate Logic Module A312,    |              |

|        | Schematic Diagram, A612-0-1                                | 7-5          |

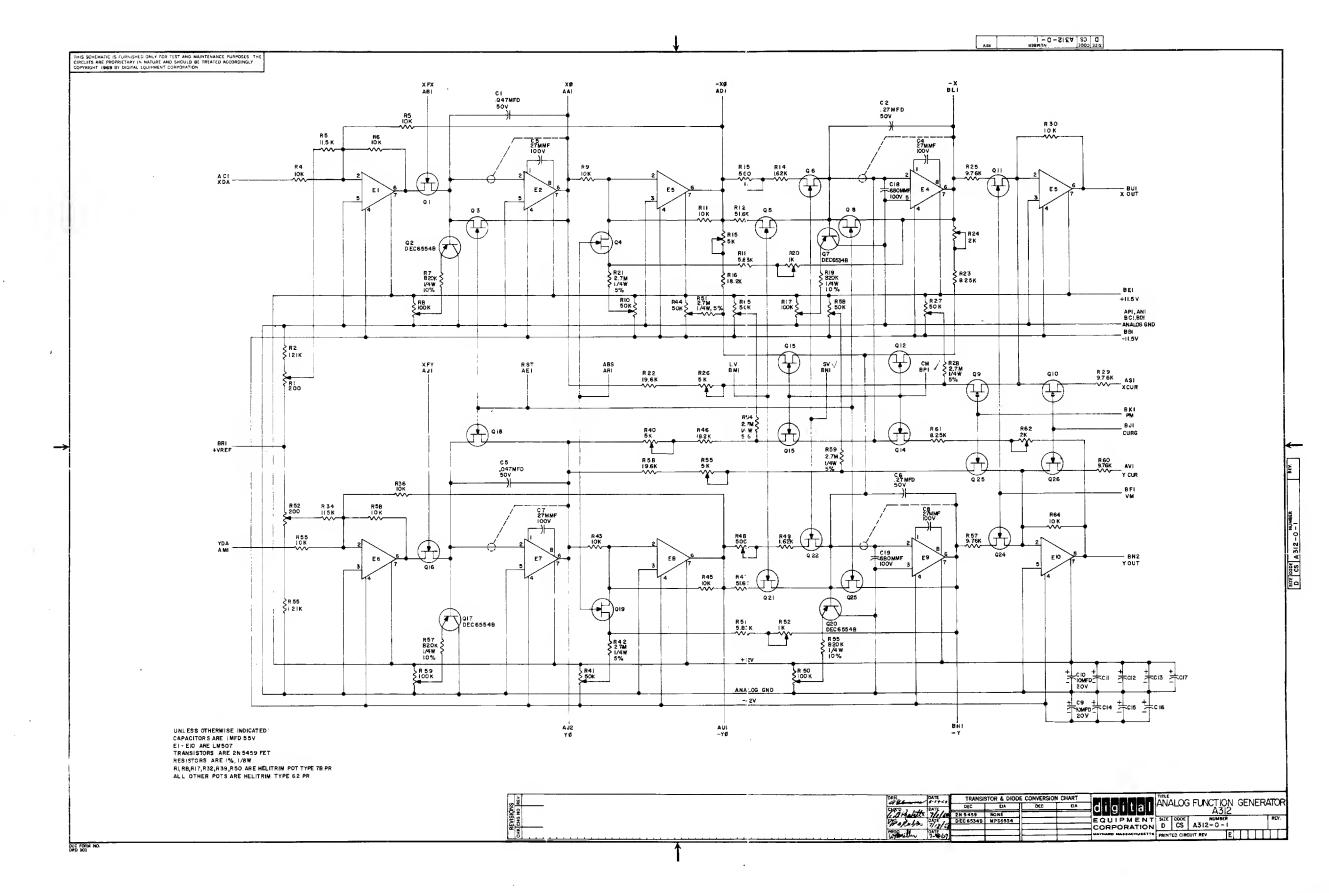

| 7-3    | Analog Function Generator Module A312, Schematic Diagram,  | • • • • •    |

|        | A312-0-1                                                   | 7-7          |

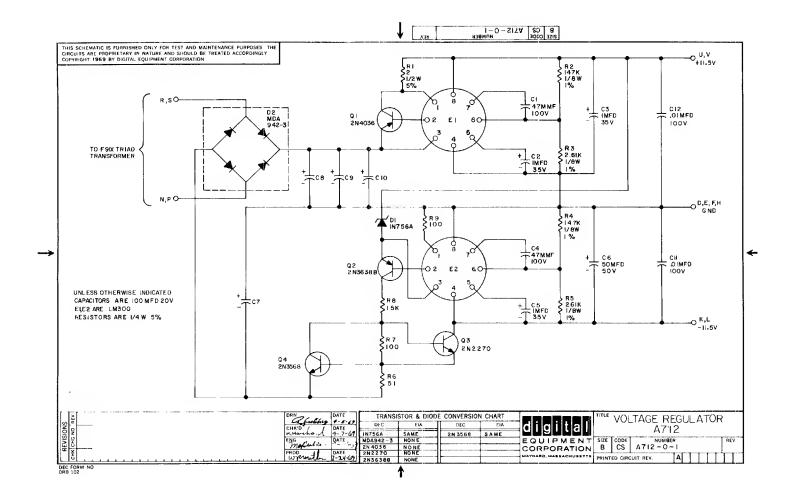

| 7-4    | Voltage Regulator Module A712, Schematic Diagram, A712-0-1 | 7-9          |

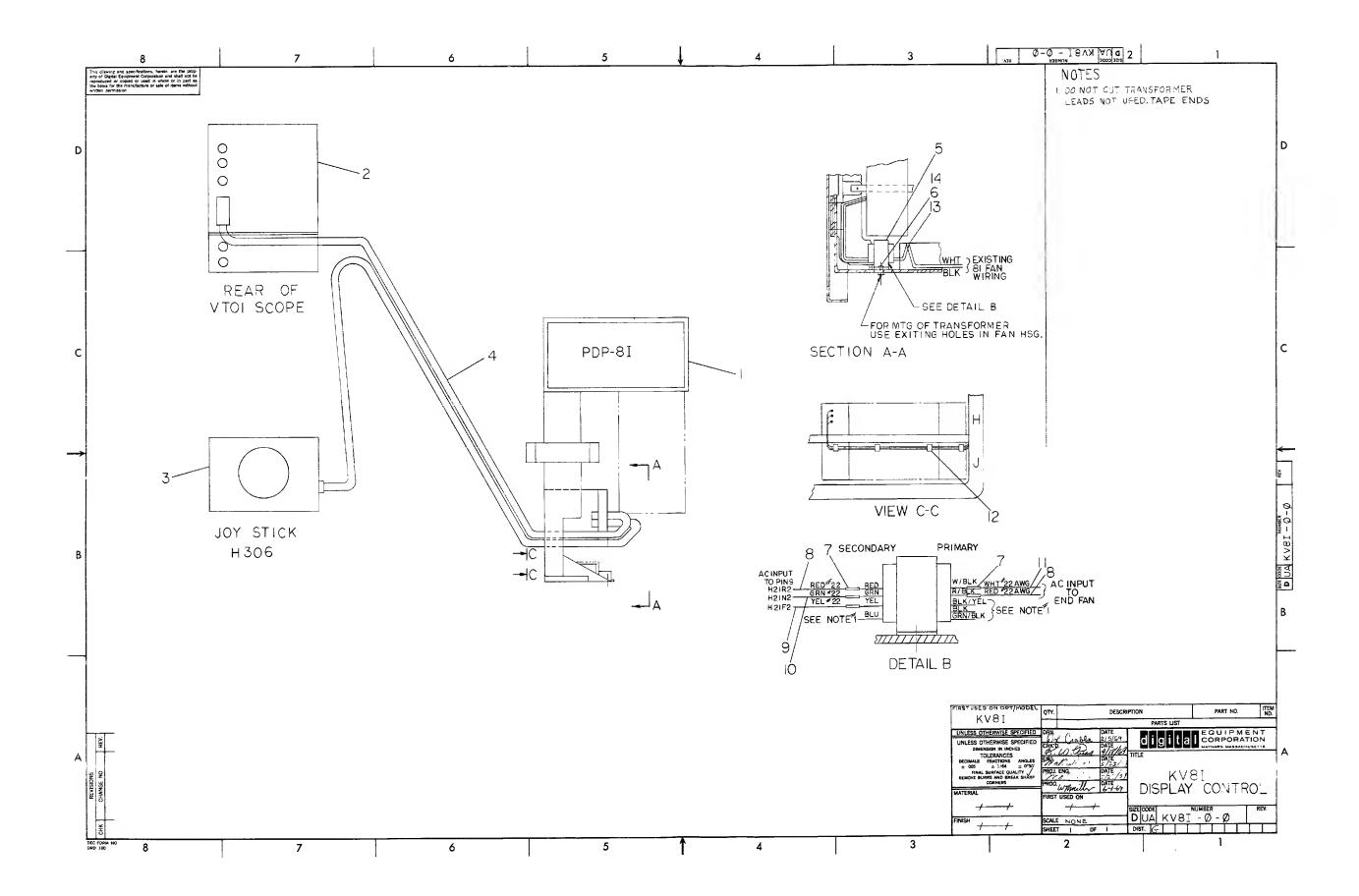

| 7-5    | General Wiring Sheet for KV8I Modification, KV8I-0         | 7-11         |

| 7-6    | KV8I Display Control, KV8I-0-0                             | 7-13         |

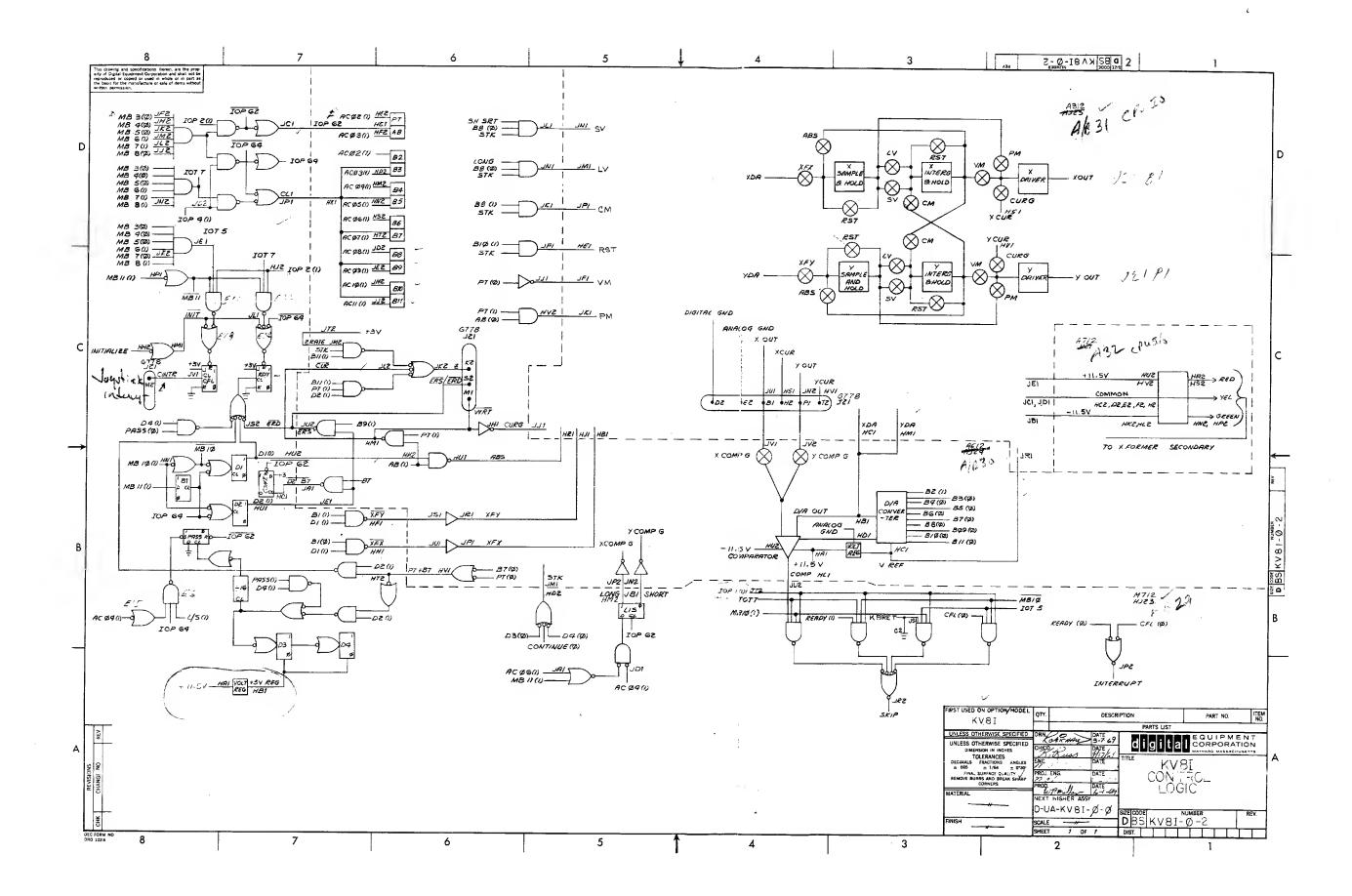

| 7-7    | KV8I Control Logic, KV8I-0-2                               | 7-15         |

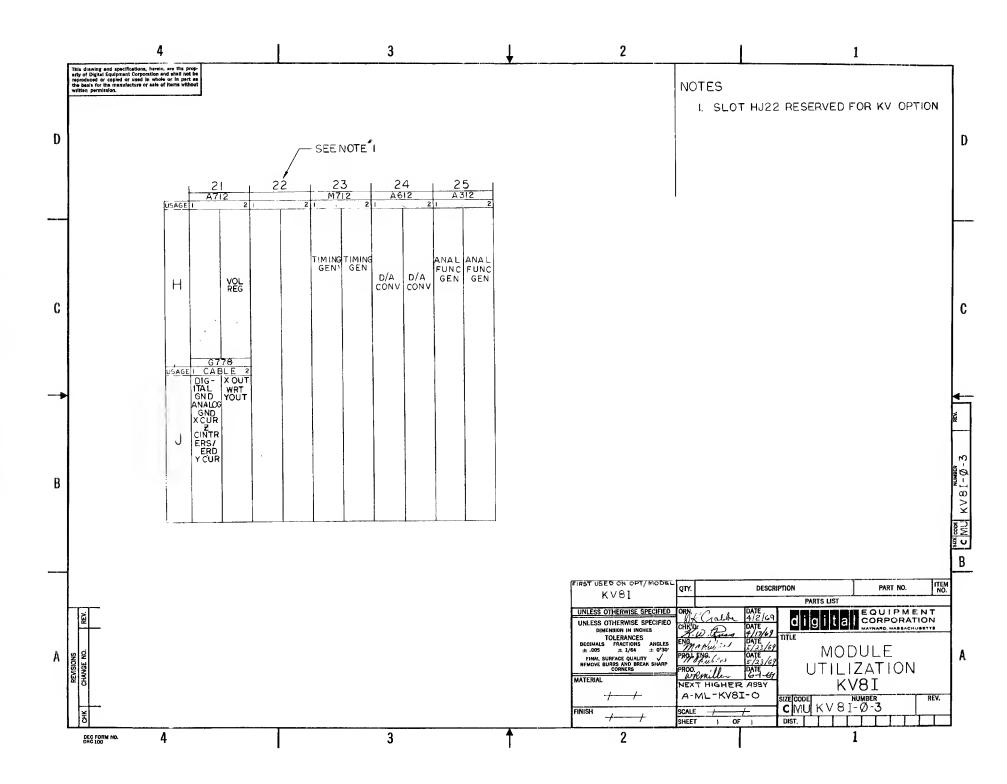

| 7-8    | Module Utilization KV8I, KV8I-0-3                          | 7-17         |

| 7-9    | General Wiring Sheet for KV8I, KV8I-0-5                    | 7-19         |

| 7-10   | KV8I Display Acceptance Procedure, KV8I-0-6                | 7-21         |

| 7-11   | Performance Specifications for KV8I Controller and         | . / 21       |

|        | VT01 Display, KV8I-0-7                                     | 7-23         |

| 7-12   | Joystick Control Assembly, H306-0-0                        | 7-25         |

### LIST OF TABLES

| Number | Title                                                       | Page   |  |  |

|--------|-------------------------------------------------------------|--------|--|--|

| 1-1    | Accessory Hardware Complement                               | . 1-5  |  |  |

| 1-2    | Accessory Hardware Required but not Supplied                | . 1-5  |  |  |

| 2-1    | PDP-8/I Modification Wiring List                            | . 2-3  |  |  |

| 3-1    | Function of Controls and Indicators, Graphic Display System | . 3-3  |  |  |

| 3-2    | Type KV Controller Instruction Set                          | 3-12   |  |  |

| 3-3    | Table of Absolute and Relative Coordinates for Figure 3-6   | 3-16   |  |  |

| 4-1    | Analog Function Generator, Input/Output Signals             | 4-9    |  |  |

| 4-2    | Analog Function Generator Digital Control Signals           | . 4-10 |  |  |

| 5-1    | X or Y Sample and Hold or Integrator Calibration Tests      | . 5-11 |  |  |

| 5-2    | X and Y Sample and Hold and Integrator Drift Rate           |        |  |  |

| -      | Adjust Routines Using Reset and the CRT                     | . 5-11 |  |  |

| 5-3    | Analog Function Generator and Timing Generator              |        |  |  |

| 0.5    | Adjustment Routines                                         | . 5-12 |  |  |

| 5-4    | Starting Addresses                                          | . 5-12 |  |  |

| 5-5    | Function of Gain and Centering Potentiometers               | . 5-12 |  |  |

| 5-6    | Function of X and Y Absolute Zero and Absolute Gain         |        |  |  |

| 0.0    | Potentiometers                                              | . 5-12 |  |  |

| 5-7    | Function of X and Y Point Mode Zero and Gain Potentiometers | . 5-13 |  |  |

| 5-8    | Function of X and Y Short Vector Gain Potentiometers        | . 5-13 |  |  |

| 5-9    | Function of Gain and Centering Potentiometers               | . 5-13 |  |  |

| 5-10   | Switch Positions for Visual Check                           | . 5-13 |  |  |

| 6-1    | Repair Parts Cross Reference List                           | 6-1    |  |  |

| 6-2    | Timing Generator Module M712 Repair Parts List              | 6-3    |  |  |

| 6-3    | Digital-to-Analog Converter and Gate Logic Module A612,     |        |  |  |

|        | Repair Parts List                                           | . 6-7  |  |  |

| 6-4    | Analog Function Generator Module A312, Repair Parts List    | 6-11   |  |  |

| 6-5    | Voltage Regulator Module A712, Repair Parts List            | 6-13   |  |  |

| 7-1    | List of Diagrams                                            | . 7-1  |  |  |

# INTRODUCTION

This publication covers maintenance instructions for the KV Graphic Display System manufactured by the Digital Equipment Corporation, Maynard, Massachusetts. The instructions in this manual are directed to the basic configuration of the system (KV Controller, the VT01 Storage Tube Display, and the H306 Joystick Controller) and its implementation into the PDP-8, 8/I, 8/L, 8/S, 12 and LINC processor.

This manual is intended for use by personnel responsible for installation and maintenance of the KV Graphic System and is arranged into the following seven chapters:

Chapter 1 – briefly describes the system and its general specifications.

Chapter 2 - contains instructions for inspecting,installing, performing preliminary checkout and adjusting the equipment.

Chapter 3 — contains a description of the operating controls and indicators and provides the instruction set, along with sample programs, for programming the system.

Chapter 4 - contains a functional block diagramdiscussion of the KV controller together with a detailed circuit analysis of each of the individual functional circuits that comprise the basic controller. In addition, a discussion of operational

**Related Documents**

amplifiers and other circuits is provided to aid in the understanding of the operation of the KV controller.

Chapter 5 – contains maintenance instructions for the equipment. Included in this chapter are warranty and service policies of the Digital Equipment Corporation and alignment and adjustment, preventive and corrective maintenance, and repair and replacement instructions.

Chapter 6 – lists and locates each of the replaceable parts of the KV controller to facilitate repair parts procurement for the equipment.

Chapter 7 - contains the necessary engineering drawings to assist in the performance of maintenance tasks.

|         | Title                                      | Publication No.                   |

|---------|--------------------------------------------|-----------------------------------|

| PDP-8/I | Maintenance Manual                         | DEC-8I-HR1A-D<br>DEC-8I-HR2A-D    |

| PDP-8   | User's Handbook                            |                                   |

|         | Maintenance Manual                         | F-87                              |

| PDP-8/L | User's Handbook                            | С9                                |

| PDP-8/S | User's Handbook<br>Maintenance Manual      | F85S<br>F-875                     |

| PDP-12  | User's Handbook                            | DEC-12-GRZA-D                     |

| LINC-8  | User's Handbook<br>Maintenance Manual      | F-L85P<br>F-L87                   |

| VT01    | Storage Display Unit<br>Instruction Manual | Type 611, Tektronix<br>(Modified) |

Type KV Graphic Display System

# CHAPTER 1 General Information

#### 1.1 GENERAL

The basic KV Graphic Display System (consisting of the KV controller, the VT01 Storage Tube Display Unit, the optional H306 Joystick Controller, and associated cabling as shown in the frontispiece) may be used with a PDP-8, 8/I, 8/S, 8/L, 12 or LINC computer. The system can be expanded to a multi-terminal (up to eight display units on line) with the addition of the Multiplex Interface Option and VT02 Storage Tube Display Units with keyboards.

#### 1.2 PURPOSE OF THE EQUIPMENT

Common applications of computer graphic display systems permit immediate solution of a broad range of electrical, physical, and mechanical design and analysis problems. While there can be little doubt about the value of the computer in solving complex design problems, the graphic display system accelerates the exchange of data between the user and the computer. Visualization of a problem, whether it be a simple curve that displays the interaction of two variables or a complex network synthesis, permits rapid selection of new parameters. Graphical output permits the user to create a visual model of an electrical, hydraulic, mechanical, or other system while the computer operates on its mathematical counterpart. Thus, parameters that define a point outside a curve can be immediately displayed as irrelevant data, the change in the

cross section of a beam can immediately reveal its ability to withstand a given load, and a change in the value of a resistor can immediately demonstrate the relative stability of an electrical circuit.

#### 1.3 BASIC SYSTEM DESCRIPTION

The basic KV Graphic Display System, shown in Figure 1-1, consists of a Type KV Controller, a VT01 Display (Modified Tektronix Type 611 Storage Display Unit), a Type H306 Joystick Control (that permits the user to locate a visual nonstored spot or cursor anywhere on the usable image area of the display), and a Teletype Model 33 Automatic Send-Receive (ASR-33) Keyboard, all working into an 8-family, LINC or PDP-12 Central Processor. Software includes a 64-character (ASCII-compatible) symbol generator, a general-purpose text editor, a graphics interactive programming system called EDGRIN (for EDitor with GRaphic INterpreter), and a cursor reading subroutine that can be used to define the position of the joystick-generated cursor upon command of the user.

#### 1.3.1 KV Controller

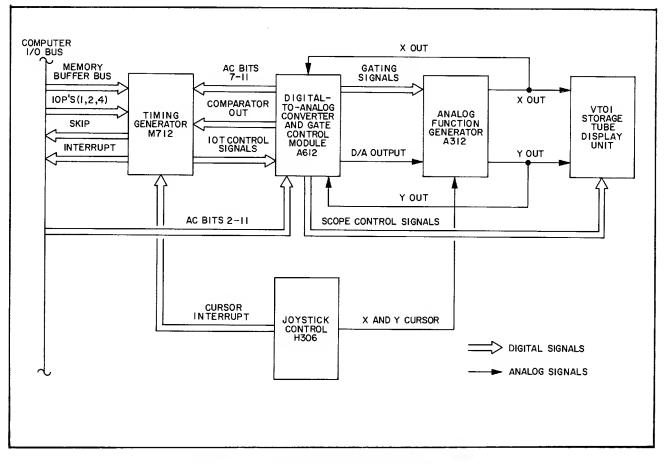

The basic KV Controller, shown in Figure 1-1, consists of the four modules: (1) Type A712 Voltage Regulator, (2) Type M712 Timing Generator, (3) Type A612 Digital-to-Analog Converter and Gate Logic Module and (4) Type A312 Analog Function Generator. These modules are described in the subsequent paragraphs.

Figure 1-1. KV Controller, Simplified Block Diagram

#### Type A712 Voltage Regulator Module

The A712 module converts 60-cycle power to regulated  $\pm 11.5$  volts which is used by the modules in the controller. Primary a-c power is supplied to the module by a step-down transformer which must be installed onto the CPU main frame. Other dc voltages required by the KV controller are supplied from the CPU.

#### Type M712 Timing Generator Module

This module decodes the input IOT instructions from the computer and generates system timing signals in synchronism with the computer machine cycle. This module has an internal adjustment that controls vector stroke timing.

# Type A612 Digital-to-Analog Converter and Gate Module

This module contains a digital-to-analog converter (D/A) which converts a 10-bit word to a dc analog signal ranging from 0 to -4 volts. Included in the D/A is a comparator which permits program controlled analog-to-digital conversions to locate the position of the joystick in the cursor mode. This module contains four controls for adjustment of the comparator. The module also contains the input data buffer, which receives data-word inputs from the computer, and generates gating signals which are applied to the A312 Analog Function Generator module. These gating signals establish analog signal paths; hence, the mode of operation of the system.

#### Type A312 Analog Function Generator

The Type A312 Analog Function Generator receives 10 gated outputs and the analog output of the D/A from the Type A612 D/A converter. The gating signals establish the permanent signal paths of the module. The module converts the analog output of the D/A to the appropriate X and Y deflection voltages for the VT01 display. This module contains 22 controls for adjustment of point, vector, and circle patterns on the VT01 display.

#### 1.3.2 Type VT01 Storage Tube Display Unit

The Type VT01 Storage Tube Display Unit (Figure 1-2) is a modified Tektronix Type 611 Storage Display Unit that is driven by the output signals from the KV Controller. The VT01 Storage Display Unit contains a Type T6110 bistable direct view storage tube, which has an aspect ratio of 3/4 and which measures  $16 \times 21$  centimeters ( $6-1/2 \times 8-1/4$  inches). The display has a resolution of 400 vertical and 300 horizontal stored line pairs. Two front panel pushbuttons allow the user to select either a VIEW or an ERASE mode.

An additional mode that is utilized by the KV Controller is the write-through mode. The write-through mode of operation is used to locate and position the cursor with the Type H306 Joystick Controller. When the cursor is moved, the small generated circular spot will not be stored by the display nor will it destroy previously stored information.

#### 1.3.3 The H306 Joystick Controller

The H306 Joystick Controller (Figure 1-3) is the means by which the user can interact directly with the graphical or text information presented by the system. The joystick is used to position the cursor anywhere in the effective image area of the display. The joystick output produces two analog voltages corresponding to the X and Y position coordinates (address) of the cursor. The coordinate addresses are read into the computer, when commanded by the interrupt button. A successive approximation program together with the digital-to-analog circuits of the KV Controller produce a digital representation of the cursor position in the accumulator of the computer.

Figure 1-3. Type H306 Joystick Control

# 1.3.4 Model 33 Automatic Send-Receive Keyboard

The Teletype ASR-33 keyboard (Figure 1-4) is the means by which the user enters the digital data into the computer. The keyboard is the link between the user, the display and the computer. Commands entered into the computer through operation of the keyboard are processed by the computer and stored as data, or perform some manipulation of the viewed display.

#### 1.4 **OPTIONS**

#### 1.4.1 Multiplex Interface Option

The KV Graphic Display System can also accommodate a multiplex interface option (which consists of an eight-channel multiplexer module and a line driver module) that permits up to eight remote graphic display consoles to be operated in a time share mode through a single KV Controller. The multi-terminal Graphic Display System combines the assemblies of the basic KV Controller and up to eight VT02 graphic terminals.

#### 1.4.2 Type KVGT Graphic Display Unit

The KVGT Graphic Display Unit (Figure 1-5) is a complete remote station consisting of a VT01 and a keyboard which includes the appropriate interface logic. The KVGT, in multi-station systems, is used with the multiplex interface option exclusively.

#### 1.4.3 VS08 Storage Tube Controller Interface

The VS08 Storage Tube Controller Interface provides a location for basic KV Controller modules in a half-rack of logic circuitry together with a suitable power supply and interface modules to permit operation of the KV Graphic System with the PDP-8, PDP-8/S and LINC Computer Systems. The multiplex interface option can be added to the VS08 interface so that up to eight remote KVGT graphic terminals can be on line in a multi-terminal system.

Figure 1-5. Type KVGT Graphic Display Unit

#### 1.5 ACCESSORY EQUIPMENT

Each KV Graphic Display System is shipped with an accessory complement including both hardware and software. The hardware and software complements are described in the subsequent paragraphs.

#### 1.5.1 Hardware

Table 1-1 lists the tools that are supplied with KV Controller. Table 1-2 lists tools that are not

supplied, but should be available to properly install and maintain the system.

#### 1.5.2 Software

The type KV software complement is listed in Chapter 7.

#### 1.6 SPECIFICATIONS

The specifications covering the KV Controller are listed in detail in Chapter 7. (Refer to Table 7-1 for page location.)

| Name                   | Туре   | Qty | Purpose                                                                                    |

|------------------------|--------|-----|--------------------------------------------------------------------------------------------|

| Double Module Extender | W983   | 1   | Used to gain access to contacts or components on modules during alignment and maintenance. |

| Alignment Tool         | Bourns | 1   | Use to access potentiometers for adjustment.                                               |

# TABLE 1-1. ACCESSORY HARDWARE COMPLEMENT

# TABLE 1-2. ACCESSORY HARDWARE REQUIRED BUT NOT SUPPLIED

| Name            | Туре | Qty | Purpose                                                                        |

|-----------------|------|-----|--------------------------------------------------------------------------------|

| Wrapping Tool   | H811 | 1   | Used to wire-wrap terminals of module connectors during maintenance or repair. |

| Unwrapping Tool | H812 | 1   | Used to unwrap terminals of module connectors during maintenance or repair.    |

# CHAPTER 2 INSTALLATION

#### 2.1 GENERAL

This chapter covers installation of the Type KV Graphics Display System. Instructions are provided for unpacking, transformer installation and wiring, installation of modules and system intercabling. The instructions are based on the assumption that the entire modification and installation will take place at the customer's facility. In cases where this is not true, disregard those instructions that are not applicable.

#### 2.1.1 Power Requirements

Controller – The controller operates from the 115-volt, 60-Hz, single-phase fan power bus of the computer. Internal power supplies provide  $+11.5 \pm 1$  and  $-11.5 \pm 1$  volts dc, each at 100 mA. Additional +5 volts at 395 mA and -15 volts at 37 mA are supplied to the controller from the power supplies of the computer.

VT01 – The VT01 operates from a 115-volt, 60-Hz, single-phase source. For 230-volt operation, refer to the Tektronix 611 manual.

Joystick Controller – The Joystick Controller operates from the +11.5- and -11.5-volt power supply of the controller.

#### 2.1.2 Space Requirements

Adequate space should be provided to permit access to the computer and VT01 for maintenance. The outline dimensions of the VT01 are shown in Figure 2-1. (Refer to the applicable computer User's Handbook for computer dimensions.) The equipment should be arranged so that the display unit is clearly visible and the computer console, teletype and Joystick Controller are readily accessible to the operator.

Figure 2-1. Storage Tube Display Unit Overall Dimensions and Location of Remote Programming Connector

#### 2.1.3 Environmental Considerations

The controller operates in an environment ranging in temperature from  $10^{\circ}$  to  $40^{\circ}$ C ( $50^{\circ}$  to  $104^{\circ}$ F) with a maximum temperature deviation of  $\pm 3^{\circ}$ C ( $\pm 5^{\circ}$ F). The humidity at the installation must not exceed 70%. (Refer to the VT01 instruction manual for environmental considerations for the VT01.)

#### 2.2 UNPACKING

Carefully unpack the equipment and ascertain that the appropriate items have been supplied and that no damage was incurred in shipping.

The following items comprise a typical Type KV Graphics Display System:

- 1 Programmed Data Processor and Maintenance Manual

- 1 Type VT01 Storage Display Unit and Instruction Manual

- 1 Type H306 Joystick Controller (optional)

- 1 20-foot Dual I/O Cable Assembly (Part No. D-IA-7006289-0-0)

- 1 Type A712 Power Supply Module

- 1 Type M712 Timing Generator Module

- 1 Type A612 D/A Converter Module

- 1 Type A312 Analog Function Generator Module

- 1 Triad F91X Power Transformer

- 1 Alignment Tool

- 1 Type W983 Module Extender

#### 2.3 MODIFICATION DATA

2.3.1 Computer

The computer modification procedure is applicable to KV Graphics Display Systems that will

use a computer that has not been factory wired for the controller. The modification consists of mounting and wiring the Triad 91X step-down power transformer and wiring of the option panel. Perform the following modifications, as required:

#### NOTE

Refer to Chapter 7 for location of module compartment connectors, associated wiring list and for transformer mounting instructions.

a. Align the transformer mounting holes with the holes in the fan housing and fasten with hardware provided.

b. Connect transformer leads in accordance with the wire list of Table 2-1 using Hand Wire Wrap Tool.

#### 2.3.2 Storage Tube Display Unit

The Storage Tube Display Unit modification alters the write-through and deflection amplifiers to reduce phosphor burnout and noise hazards.

#### 2.4 INSTALLATION AND CHECKOUT

#### 2.4.1 Installation

Install the Type KV Display System as follows:

a. Check the voltage and range selectors at the rear of the VT01 and set them, if necessary, to agree with the line voltage source.

b. Remove the module cover from the PDP-8/I. Check the wiring runs associated with the Triad transformer mounted on the fan housing for physical damage. If no damage is found,

| Wire Color | From       | То             | Function  |

|------------|------------|----------------|-----------|

| Blk/Wht    | Fan Pwr AC | Xfmr Primary   | AC Input  |

| Blk/Red    | Fan Pwr AC | Xfmr Primary   | AC Input  |

| Grn        | H21N2      | Xfmr Secondary | AC Output |

| Ye1        | H21F2      | Xfmr Secondary | AC Output |

| Red        | H21R2      | Xfmr Secondary | AC Output |

TABLE 2-1. PDP-8/I MODIFICATION WIRING LIST

plug the A712 power supply modules into location H21 and power up the computer. Using a voltmeter or oscilloscope check for  $\pm 11.5 \pm 1$ volts dc at H21-U2 and  $\pm 11.5 \pm 1$  volts dc at H21-K2. Turn off the computer.

c. Place VT01 in a convenient location to the CPU and teletype and within the limits of the Dual I/O Cable Assembly. The H306 Joystick Controller is placed beside the VT01 either to the left or right side depending on the operator. Plug the G778 module end of the Dual I/O Cable into location J21 and route the cable to the back of the CPU, teletype and VT01 so as not to interfere with the operator. Plug the cannon connector into the remote program connector located at the rear of the VT01. Plug the 9-pin amphenol connector into the back of the H306 Joystick Controller. This completes the cable connections.

d. Install the remaining modules in their proper compartment locations.

#### 2.4.2 Checkout

#### **VT01** Operating Precautions

To prolong the useful life of the cathode ray tube, observe the following precautions when operating the equipment.

a. Adjust the DRIVE control for the minimum writing gun-beam current level that will

produce a clear, well-defined display. Excessive beam current may cause either a bright burn condition or, if intense enough, a more serious dark burn condition. A bright burn condition is the appearance of a residual display image after erasure. Bright burn images can be erased by adjusting the OPERATING LEVEL control to establish a fade-positive condition. The time required for a fade-positive condition to effect a complete erasure is dependent on the severity of the burn. A severe burn may require up to 12 hours for complete erasure. Operate the instrument in the fade-positive mode only as long as necessary, since in addition to the loss of useful operating time, extended fade-positive operation will decrease the life expectancy of the CRT. A dark burn condition is the destruction of the cathode ray tube phosophor by the intensive beam current. This condition is evidenced by a spot or area that will not react to the writing gun. As with a conventional CRT, the only remedy for this condition is replacement of the cathode ray tube.

b. Erase the display when the information is no longer needed. If a display is left on the CRT for an extended period of time, it can cause a residual image that may appear as a negative image of the erased display or a positive image superimposed on the new display. Whether the image appears positive or negative will depend on the brightness level of the image phosphor as compared to the brightness level of the new display's background phosphor. The residual image may be erased by establishing a fadepositive condition.

#### VT01 Set-Up

This procedure positions the front panel controls prior to the application of power.

#### **Preliminary Instructions**

a. Disconnect all external signal cables from the rear panel connectors.

b. Set the front panel controls as follows:

| POWER             | OFF                                             |

|-------------------|-------------------------------------------------|

| WRITING INTENSITY | CCW                                             |

| OPERATING LEVEL   | Do not change the setting of this con-<br>trol. |

| FOCUS             | Midrange                                        |

TEST SPIRAL NORMAL

c. Ensure that the rear panel VOLTAGE and RANGE selectors are set to the appropriate positions for the available power source and then connect the power cord to the power source.

#### VT01 Energizing Procedure

a. Turn the POWER switch to ON. The ERASE switch should illuminate and as the instrument warms up, the display area of the CRT should assume the bright luminance of a fadepositive condition.

b. Press and release the ERASE switch. The instrument should cycle through an erase function and assume a ready-to-write condition. The display should appear to be at a uniform luminance level, much lower than the brightness level of the fade-positive condition.

c. Slowly turn the WRITING INTENSITY control in a clockwise direction while observing the display for the indication of a bright spot. If a bright spot appears, immediately turn the control counterclockwise. If the control can be turned fully clockwise without a spot appearing, this test of the instrument operating condition is normal. Set the WRITING INTENSITY control to midrange and proceed. Storage capability and resolution are affected by the interaction of the OPERATING LEVEL, WRITING IN-TENSITY and FOCUS control settings.

d. The OPERATING LEVEL control provides adjustment of the Storage Target Backplate potential. The procedure for this adjustment is given in Chapter 3 of the Tektronix Manual.

e. Pull the TEST SPIRAL switch to its FO-CUS position. A spiral waveform should appear on the display. Adjust the FOCUS and WRIT-ING INTENSITY controls for an overall clear, well-defined display of the desired viewing brightness.

f. Push and hold the TEST SPIRAL switch to its spring-loaded STORE position for about 3 seconds or until a stored spiral waveform appears on the display. The stored spiral should remain clearly visible for about 60 to 90 seconds, then appear to be almost erased as the VIEW switch is illuminated. An illuminated VIEW switch indicates that the instrument is in a holding mode of operation.

g. Press and release the illuminated VIEW switch. The stored spiral should again appear on the display and the VIEW switch should be extinguished. The instrument should remain in this condition for about 60 to 90 seconds and again assume a holding mode of operation.

h. Press and release the ERASE switch. The instrument should cycle through an erase function and assume a ready-to-write condition. This completes the instrument-energizing procedure.

#### Type KV Graphics Display System Checkout

Refer to Chapter 5 and load and run the MainDEC diagnostic self test routines. Perform the alignment and adjustment procedure contained in Chapter 5 to the extent required to align the system.

# CHAPTER 3 OPERATION AND PROGRAMMING

This chapter is divided into two sections which provide operation and programming instructions for the Graphic Display System described in this manual. With the exception of oscilloscope adjustments and joystick manipulation, there are no special operating procedures described in Section I. The techniques for programming described in Section II are at the machine-language level. Source level programs are generated using EDGRIN, a special source-language assembler that simplifies the work of originating a graphic display. EDGRIN commands deal almost exclusively with input-output program modifications, line and text display, compilation and execution of programs written in the EDGRIN language. This language gives EDGRIN the properties of an editor, compiler and operating system.

# SECTION I OPERATION

#### 3.1 GENERAL

With the exception of some VT01 Display adjustments, required prior to operation, and the MAINDEC diagnostic routines, described in Chapter 5, there are no special operating procedures for the graphic display system. Operation of the VT01 Display and the H306 Joystick Cursor Control (with the exception of manually selected coordinate positions and a program interrupt), is determined entirely by the KV Controller and the source program. However, during maintenance checkout, certain controls on the computer console and certain adjustments at the KV Controller modules must be made. Switches and controls on the VT01 Display are shown in Figure 3-1.

#### 3.2 OPERATING CONTROLS

Visible on the VT01 Display front panel are two pushbuttons; below these pushbuttons is a panel door which, when opened, exposes the power switch and five vernier controls. The functions of these controls are described in Table 3-1.

Figure 3-1. Storage Tube Display Unit VT01, Location of Controls and Indicators

| Index<br>No  | Name                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Not<br>Shown | ERASE pushbutton                                      | Used to delete all stored information from the storage tube (oscilloscope).                                                                                                                                                                                                                                                                                                                                                                                           |  |

|              |                                                       | NOTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|              |                                                       | The VT01 display has a hardware<br>safety feature that controls the<br>intensity of the display. When an<br>image has been displayed for 90<br>seconds, and no additional in-<br>formation has been added to the<br>display, this device reduces the<br>intensity of the display. Thus,<br>the display appears to vanish;<br>however, this reduction in the<br>intensity of the display has no<br>effect on the information stored<br>on the oscilloscope image area. |  |

| Not<br>Shown | VIEW pushbutton                                       | Used to restore the display to full intensity for a new 90-second period.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1            | INTENSITY control (outer concentric)                  | Used to adjust the intensity of the writing beam during normal writing functions.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 2            | Write-Thru<br>INTENSITY control<br>(inner concentric) | Used to adjust the intensity of the writing beam during write-thru writing functions.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 3            | FOCUS control                                         | Used to obtain a sharply defined writing beam.<br>This switch is used in conjunction with the<br>TEST SPIRAL pushbutton (6).                                                                                                                                                                                                                                                                                                                                          |  |

| 4            | OPERATING LEVEL control                               | Used to adjust the storage properties of the oscilloscope. This control, adjusted during in-<br>stallation, does not normally require a change in setting.                                                                                                                                                                                                                                                                                                            |  |

| 5            | POWER switch                                          | Used to energize the Storage Display Unit.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 6            | TEST SPIRAL pushbutton                                | Used to change the oscilloscope circuits from a<br>normal operating configuration to either of two<br>test configurations. The test positions are Store<br>and Focus.                                                                                                                                                                                                                                                                                                 |  |

# TABLE 3-1. FUNCTION OF CONTROLS AND INDICATORS,GRAPHIC DISPLAY SYSTEM

| TABLE 3-1. | FUNCTION OF CONTROLS AND INDICATORS, |

|------------|--------------------------------------|

|            | GRAPHIC DISPLAY SYSTEM (cont)        |

| Index<br>No. | Name                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>(cont)  | Normal                                             | When the TEST SPIRAL pushbutton is in its center position, the oscilloscope circuits are configured for normal operation.                                                                                                                                                                                                                                                                                                                                                                      |

|              | Store test                                         | When the TEST SPIRAL pushbutton is depressed<br>and held in for one second or longer, a stored spiral<br>waveform should appear on the oscilloscope. This<br>spiral waveform should remain intensified for<br>between 60 and 90 seconds whereupon the VIEW<br>switch will light and the displayed image will<br>appear to be erased. When the VIEW switch is<br>illuminated, the oscilloscope will enter its store<br>mode. Depressing the VIEW switch again will<br>restore the spiral image. |

|              | Focus test                                         | When the TEST SPIRAL switch is pulled out to its focus test position, a spiral waveform should appear on the oscilloscope. The FOCUS control should then be adjusted for the sharpest image on the display.                                                                                                                                                                                                                                                                                    |

| Not<br>Shown | TYPE H306 JOYSTICK<br>CONTROLLER INT<br>pushbutton | When depressed, a software routine automatically places the digital equivalent of the coordinate value of the cursor position in the PDP-8/I accumulator.                                                                                                                                                                                                                                                                                                                                      |

| Not<br>Shown | Joystick control                                   | This control can be moved in two axes. Its position<br>defines the position of a spot, called a cursor, on<br>the image area of the oscilloscope.                                                                                                                                                                                                                                                                                                                                              |

# SECTION II PROGRAMMING

#### 3.3 GENERAL

The descriptions in this section are addressed to machine-language programming requirements and acquaint maintenance personnel with the controller instruction-word set. Parameter and data-word formats are described so that simple machine-language programs can be compiled for the purpose of testing and checkout of the KV Graphic Display System. Also, simple display routines are given as samples.

#### 3.4 **DISPLAY CAPABILITIES**

The KV Graphic Display System, which comprises the controller and the VT01 display, has four primary line-drawing capabilities and a software-controlled text generation capability. The four graphic constructions are:

| a. Straight Lines | c. Circles |

|-------------------|------------|

| b. Points         | d. Arcs    |

#### 3.5 THE OSCILLOSCOPE DISPLAY

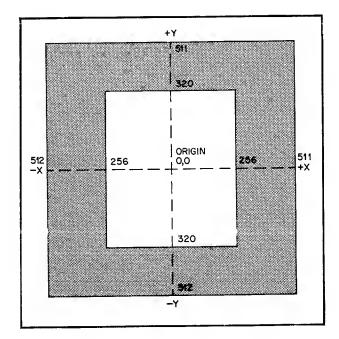

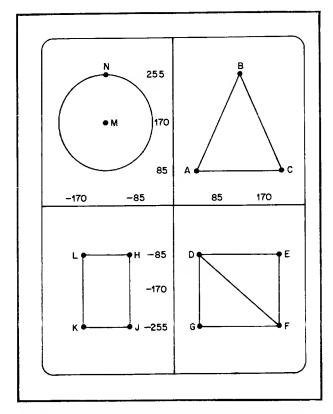

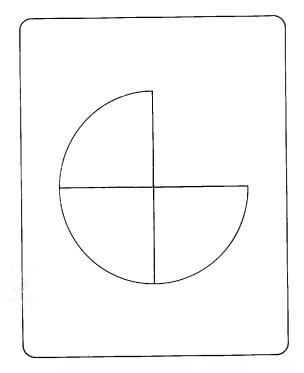

The oscilloscope display (or image) area (Figure 3-2) is divided into a square four-quadrant rectangular coordinate system whose effective area limits are  $\pm$  512 decimal (1000 octal) units along both the X and Y axes (this is approximately 85 decimal (125 octal) units/linear inch). Of this effective area, the visible image-area limit along the X-axis is  $\pm$  256 decimal (0400 octal) units; along the Y-axis the visible limit is  $\pm$  320 decimal (0500 octal) units.

#### 3.5.1 The Addressable Coordinates

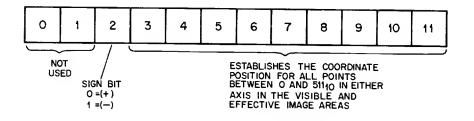

All coordinates are expressed either in terms of their displacement from the origin or with respect to the last program-named coordinate position. Any point within the image area must be defined by both its X-axis and Y-axis coordinates with the X-axis coordinate always expressed first. If the desired position of a coordinate is given as absolute, its displacement is taken from the origin. If the desired coordinate position for either axis is expressed as relative, its displacement is taken from the last named position for that axis.

In machine-language programming the characteristics of the desired graphic form, such as point, line, arc, or circle, must be specified together with the X- and Y-axis coordinates that locate the position of the line form in the display. These requirements are met by two distinct word formats that are used to define the characteristics and the coordinates; the parameter word defines the desired line form characteristics and the data word locates the X- and Y-position coordinates of the line form. In this description, both parameter and data words are expressed as octal numbers, but are written into the accumulator or memory registers of the computer and the registers of the controller, as binary numbers. When using EDGRIN as the source language, the parameter words are predetermined through programmer selected ASCII characters by the EDGRIN assembler. The Xaxis and Y-axis coordinates, however, are expressed as digital numbers by the programmer but assembled as binary numbers by EDGRIN.

#### 3.5.2 Visible Image Area

The visible image area of the display oscilloscope is normally used when defining a coordinate position. Any definable point in the visible image area is considered as the hardware limit. Any definable point between the visible image area and the effective image area (shaded area, Figure 3-2) is considered a software limit. All addressable coordinates should lie within the visible image area unless origin shifting, scaling, or light button features of EDGRIN are used. Origin shifting, scaling, and light button features of programming are described in the EDGRIN Programming Manual and are beyond the scope of this publication.

#### 3.5.3 Line-Drawing Capabilities

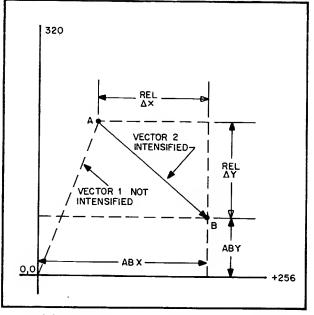

The KV controller draws lines on the oscilloscope screen through a linear vector stroke that is generated by the controller analog function generator module. Depending on whether the

Figure 3-2. Effective and Visible Image Areas

starting and end-point coordinates for the linear stroke to be generated are referenced to the origin or to the last named coordinate positions, the stroke generation format is expressed as absolute, or relative, respectively.

#### **Linear Vectors**

Parameters that define a wanted linear vector are short or long, relative or absolute, and intensified (visible) or unintensified (invisible). Such linear vectors are always drawn between a given coordinate location and an end point which can be specified in either absolute or relative mode and are executed in either a short or long format. The vector can be drawn visible or invisibly between the given starting point and specified end point.

The end-point coordinates may be specified relative to the given starting point coordinates by specifying the relative mode and sequentially entering the X and Y coordinate positions, which define the incremental displacement ( $\Delta X$ and  $\Delta Y$ ) of the line along the X- and Y-axes (Figure 3-3), into the X and Y sample and hold registers (XSH and YSH, respectively) of the controller. The end-point coordinates may also be entered absolutely (with respect to the origin) by specifying the absolute mode and sequentially entering the coordinate positions, which define the absolute displacement of the end point along the X- and Y-axes, into the X and Y sample and hold registers, XSH and YSH, of the controller.

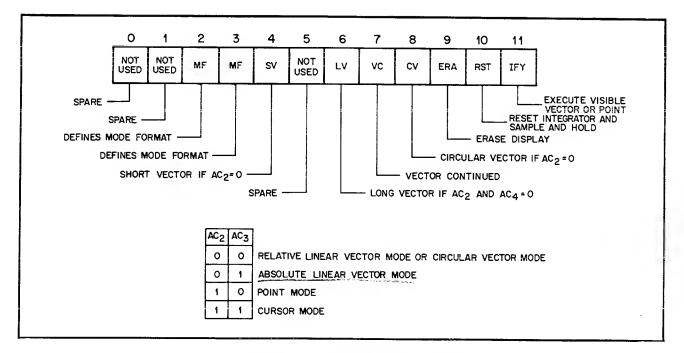

Drawing Modes – Relative and absolute modes are program ordered by depositing the desired parameter as a binary bit of a 9-bit parameter word into the PDP-8 family accumulator and then issuing an execute input-output transfer instruction. Other line-vector parameters that are defined by the 9-bit parameter word are long and short format, the intensification of the wanted line, erasure of the display currently shown on the oscilloscope screen, and integrator reset. An integrator reset ensures that the line-vector will be properly referenced to the origin. If the integrator reset is not specified by one of the bits in the parameter word, the line vector should start from the last named end point.

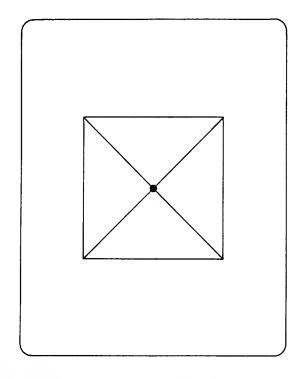

Figure 3-3. Specification of Start and End Linear Vectors

Figure 3-3 shows two linear vectors: vector 1, which is illustrated as the dashed line, has its starting point at the origin and is drawn unintensified (invisibly). The coordinates of endpoint A of vector 1 are (85,255). This vector can be expressed in relative mode if the integrator reset bit in the parameter word was previously set, or directly in absolute mode. The coordinates of end-point B of vector 2 are 255,85 absolute or 170, 170 relative. This vector would be specified as long because it is greater than 3/8 inch in length and should be drawn intensified so that it will be displayed on the oscilloscope image area.

Long and Short Linear Vectors - The length of the generated linear vector stroke is determined by the stroke-control timing circuits in the controller. For line vectors, the stroke-control timer operates at two discrete time intervals depending upon whether a long- or short-stroke bit is set in the 9-bit parameter word. When a long stroke is chosen, the stroke control timer will provide a time signal 2700 machine cycles long (for a total of 4.05 milliseconds at 1.5 microsecond/machine cycle). When a short stroke is chosen, the stroke control timer will provide a time signal that is 1/16 the period of the long stroke time period (for a total of 250 microseconds). The vectors illustrated in Figure 3-3 are long.

#### Long Linear Vectors

A long vector execution is required if the vector length exceeds 3/8 inch. Choosing the longvector bit in the 9-bit parameter control word for a line less than 3/8 inch in length will cause deterioration of the line quality which will result in excess line width and low resolution.

Whenever the vector length is over 3/8 inch but less than 6 inches, the long vector bit should be specified in the parameter word. When the starting X- and Y-axis coordinates for the vector are chosen, and if these coordinates do not occur at the origin in the display, an invisible vector must first be drawn to the starting point of the visible vector. The visible vector A·B in Figure 3-3 is drawn in just this manner. The programming sequence is as follows:

a. The oscilloscope display is first erased and the integrators in the controller are reset to obtain an origin (0, 0) starting-point setting both the X and Y integrators.

b. Next the X-axis coordinate is loaded into the X-axis sample and hold register and the Y-axis coordinate is loaded into the Y-axis sample and hold register. This occurs as two sequential subroutines in the program.

c. The parameters for the vector are then loaded into the computer accumulator in their proper bit positions and an absolute long nonintensified vector is executed. When the output voltage from the integrators equals the same voltage level as that of the analog value of the end-point (A) coordinates in the respective sample and hold registers, an invisible vector will have been executed to point A.

d. When the vector is executed, the program is held in a waiting-loop microprogram called a skip test, until the vector is completed. At the completion of the vector, the controller returns a skip signal (ready flag) to the interfacing computer to permit the program to continue.

e. To generate the visible vector  $A \cdot B$  the X-axis coordinate of point B is loaded into the X-axis sample and hold register and the Y-axis

coordinate of point B is loaded into the Y-axis sample and hold register.

f. The parameters for the visible vector are then entered into the accumulator of the computer in their proper bit positions so that an absolute (or relative, depending on how the Xand Y-axis coordinates were chosen) long intensified vector is generated. The execution of this vector causes the output voltage of the respective X and Y integrators to be driven to the same analog levels as those held in the respective X and Y sample and hold registers.

g. The program is held in the skip test waiting loop until the ready flag is detected. This completes the execution of the visible vector  $\mathbf{A} \cdot \mathbf{B}$ .

#### NOTE

Unlike digital registers a property of analog registers is their inability to remember their values over long periods of time. Thus, all analog registers are subject to drift. In the KV Controller this drift is not greater than 30 spot positions per second in the sample and hold registers and 6 spot positions per second for the integrate and hold registers, over a  $\pm$  3° C ( $\pm$  5° F) range about the ambient temperature when they are initially adjusted. This spec means that some care must be taken to reset the integrators when analog data is not renewed. Hence, it is a good practice to reset whenever a vector sequence is broken.

#### Short Linear Vectors

A short vector execution is desired if the vector length is less than 3/8 inch. Choosing the short vector bit in the 9-bit parameter control word, for a line greater than 3/8 inch in length, may exceed the storage capability of the oscilloscope and the accuracy of the KV-8 Controller.

#### 3.5.4 Circle-Drawing Capabilities

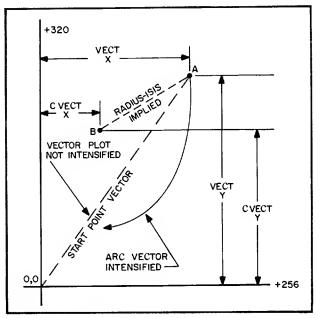

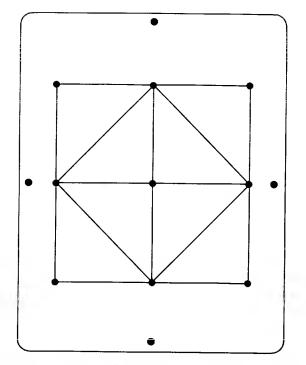

The KV-8 controller is capable of drawing arcs and circles on the oscilloscope with a circular vector stroke that is generated by the controller analog function generator module. An arc or circle is drawn by first specifying the X- and Y-coordinates of a point on the circumference of the wanted circle and then initializing the integrators to these values using the linear vector mode and drawing an invisible linear vector to this point. This point defines the start of the arc or circle vector. Next, the X- and Y-coordinates of the center of the circle are determined relative to the origin at 0.0 and then the arc or circle is drawn in circular vector mode using the coordinates of the center. Depending on the length of the arc, it may be executed in either short, long, or continuous circular vector mode. The difference between the center coordinates and the circumference coordinates determines the radius of the circle or arc.

#### **Circular Vectors**

Parameters that define a wanted circular vector are short, long, or continuous; and intensified or unintensified. Circular vectors are always drawn clockwise with respect to the starting location. The arc or circle can be drawn visibly or invisibly between a given starting point and the end point. The starting point coordinates must be specified first; then the center of the arc or circle is computed to give the radius. In Figure 3-4, the circular vector is specified by giving the X and Y coordinates of starting point A as absolute from the origin. A linear vector is then drawn invisibly to point A to give the start of the wanted arc. Next, the coordinates of point B are specified and the circular vector is drawn. (The coordinates for the center of a circle in circular arc mode are always referenced to the origin 0,0.) If a short vector has been chosen, the arc will subtend 5.625°; if a long vector has been chosen, the arc will subtend 90°; and if a continuous vector has been chosen, the arc will be continuously drawn until the arc is stopped by giving the suitable stop command.

Long and Short Circular Vectors – The arc angle of a generated circular vector stroke is deter-

Figure 3-4. Specification of Center, Start and Circumference of Circular Vectors

mined by the stroke-control timing circuits in KV controller. For arc vectors the stroke-control timer operates at two discrete intervals depending upon whether a long or short circular stroke bit is set in the 9-bit parameter word. When a long stroke is chosen, the stroke control timer will provide a time signal that permits an arc of 90 degrees to be subtended. The circular vector illustrated in Figure 3-4 is long.

Whenever the circular vector to be generated subtends an integer multiple of  $5.625^{\circ}$ , the short vector mode bit should be specified in the parameter word. The desired arc angle is then obtained by executing the correct number of short circular arc vector commands. When this is done, it may not be necessary to reload the coordinates of the center prior to each execution if the arc can be completed in less than 20 milliseconds (that is, if there is no long wait between the completion of each  $5.625^{\circ}$  segment and the initialization of the next  $5.625^{\circ}$  segment).

Continuous Circular Vectors – When a circular arc with an arc angle not divisible by  $90^{\circ}$  or  $5.625^{\circ}$  is to be generated, it is necessary that the bit controlling the continuous mode of the 9-bit parameter word be set. Setting this bit disables the vector stroke timer in the controller. Hence,

timing must be controlled externally by the program in a real-time mode. The arc writing rate is 0.1 degree per 4.5 microsecond. Continuous mode may also be used for angles divisible by  $90^{\circ}$  or  $5.625^{\circ}$  if desired.

To draw the circular arc shown in Figure 3-4, the following programming sequence is required:

a. The oscilloscope display is first erased and the integrators in the controller are reset to obtain an origin (0, 0) setting in the X and Y integrators.

b. Using the load format to obtain the absolute vector mode, the X-axis coordinate of the linear vector is loaded into the X-axis sample and hold register and the Y-axis coordinate is loaded into the Y-axis sample and hold register. The loading of these registers occurs as two small sequential subroutines in the program:

c. The required parameters are then loaded into the computer accumulator in their proper bit positions and the absolute long nonintensified linear vector is executed. When the output voltage from the integrators equals the same voltage level as that of the analog value of the end-point (A) in the respective sample and hold registers, an invisible vector will be executed to point A.

d. When the linear vector is executed the program is held in the skip-test waiting-loop until the vector is completed. At the completion of the vector, the controller returns a skip signal (ready flag) to the interfacing computer to permit the program to continue.

e. Then, to generate the visible circular vector, the circular vector load format is chosen and the X-axis coordinate of point B is loaded into the X-axis sample and hold register and the Y-axis coordinate of point B is loaded into the Y-axis sample and hold register as in (b) above.

f. The parameters for the visible circular vector are then entered into the accumulator of the computer in their proper bit positions so that a long intensified arc vector is generated. The execution of this vector causes the output voltage of the X and Y integrators to be driven by quadrature sinusoidal signals in such a manner that they trace out the parametric path of a circular arc on the face of the display.

g. The program is held in the skip-test waiting loop until the ready flag is detected. This completes the execution of the visible arc vector.

#### NOTE

Whenever a circular vector is executed, bit 3 of the parameter word must be set to zero. The parameters for the wanted vector should always be loaded into the accumulator before the execute command is given. Refer to sample programs at end of chapter.

#### 3.5.5 Point-Plotting Capabilities

The KV controller plots points on the oscilloscope screen simply by reading the data-word analog value stored in the sample and hold registers. When a point-plot graph is to be generated it is only necessary to specify the X and Y coordinates of each wanted point in point mode. Spot diameter is 0.008 inch approximately and the distance between addressable screen coordinates is approximately 0.012 inch so that specifying X and Y coordinates in continuous increments of 1 will generate what will appear essentially as a continuous graph of the function of two variables. For points more widely separated, or for estimates of a general direction of the variables, the vector mode should be used to connect the separated points. A short vector (3/8 inch in length) will contain approximately 32 decimal (40 octal) coordinates.

#### 3.5.6 Joystick And Cursor

Any coordinate on the display viewing area can be identified with the Type H306 Joystick Control which slews a small light spot (cursor) anywhere in the visible viewing area in both the X and Y planes. The Joystick control moves in two planes and its physical position corresponds with the position of the cursor in the viewing area. An interrupt button on the Joystick behind the control permits the computer program to be interrupted on demand from the user. When the program is interrupted, and if the computer is programmed to recognize the interrupt, a routine is entered that obtains the coordinate of the current position of the cursor. The routine must be executed twice, once for each coordinate. (Refer to ADCONV Program Example at end of chapter.)

#### 3.6 BASIC MACHINE-LANGUAGE PRO-GRAMMING

All parameter-word and data-word transfers between the PDP family computer and the VT01 graphic display take place through the accumulator. Hence, each accumulator-held word must be transferred to the digital register in the controller through an input-output transfer (IOT) instruction. These input-output transfer (IOT) instructions tell the controller whether the word held in the accumulator is a parameter or data word and also what action should be taken by the controller in processing the parameter or data word.

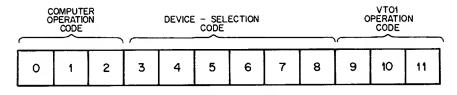

#### 3.6.1 The KV Controller