DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

# DF32 DISK FILE AND CONTROL INSTRUCTION MANUAL

.

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

1st Printing March 1968 2nd Printing October 1968 3rd Printing November 1968

# Copyright C 1968 by Digital Equipment Corporation

.

Instruction times, aperating speeds and the like are included in this manual for reference only; they are nat ta be taken as specifications.

The following are registered trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP DIGITAL PDP FOCAL COMPUTER LAB

•

## CONTENTS

# Page

## CHAPTER 1 INTRODUCTION

| 1.1   | Purpose and Scope                  | 1-1 |

|-------|------------------------------------|-----|

| 1.2   | Reference Documents and Programs   | 1-2 |

| 1.2.1 | Manuals                            | 1-2 |

| 1.2.2 | Operation and Maintenance Programs | 1-2 |

| 1.3   | System Specifications              | 1-3 |

| 1.4   | Physical Description               | 1-4 |

| 1.4.1 | Disk File Assembly                 | 1-5 |

## CHAPTER 2 OPERATION AND PROGRAMMING

| 2.1   | Operating Controls  | 2-2 |

|-------|---------------------|-----|

| 2.2   | IOT Instructions    | 2-2 |

| 2.3   | Interrupt Flags     | 2-7 |

| 2.4   | Error Flags         | 2-7 |

| 2.4.1 | DRL Flag            | 2-7 |

| 2.4.2 | PER Flag            | 2-8 |

| 2.4.3 | WIA Flag            | 2-8 |

| 2.4.4 | WIB Flag            | 2-8 |

| 2.4.5 | EWL Flag            | 2-8 |

| 2.5   | ADC Flag            | 2-8 |

| 2.6   | Status Evaluation   | 2-8 |

| 2.7   | Programming Example | 2-8 |

## CHAPTER 3 PRINCIPLES OF OPERATION

| 3.1   | Disk Format                                  | 3-1 |

|-------|----------------------------------------------|-----|

| 3.2   | NRZI Recording                               | 3-2 |

| 3.3   | General Operation of Search, Read, and Write | 3-2 |

| 3.4   | Timing Pulses                                | 3–5 |

| 3.5   | Detailed Logic Discussion                    | 3–5 |

| 3.5.1 | Address Searching                            | 3–8 |

# CONTENTS (Cont)

|       |                                | Page |

|-------|--------------------------------|------|

| 3.5.2 | Read                           | 3-10 |

| 3.5.3 | Write                          | 3-11 |

| 3.5.4 | Track Head Selection           | 3-12 |

| 3.5.5 | Continuous Data Transfers      | 3-12 |

| 3.5.6 | Disk Expander Operation        | 3-12 |

| 3.5.7 | Errors                         | 3-13 |

| 3.5.8 | Timing Track Writer            | 3-13 |

| 3.6   | Special Circuits               | 3-16 |

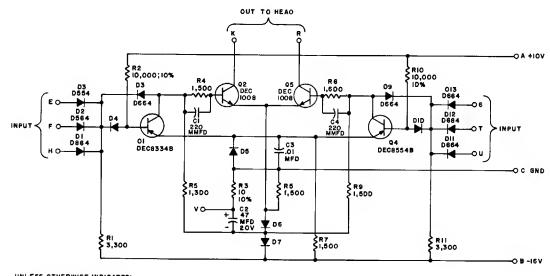

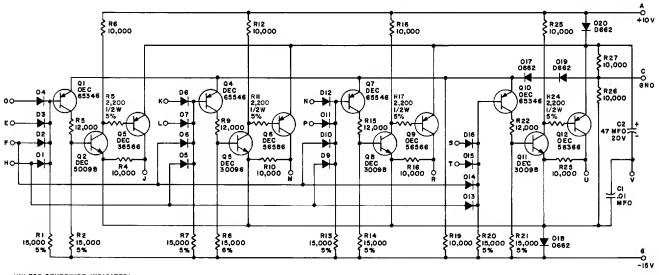

| 3.6.1 | G083 Differential Preamplifier | 3-16 |

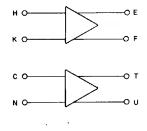

| 3.6.2 | G284 Disk Writer               | 3-17 |

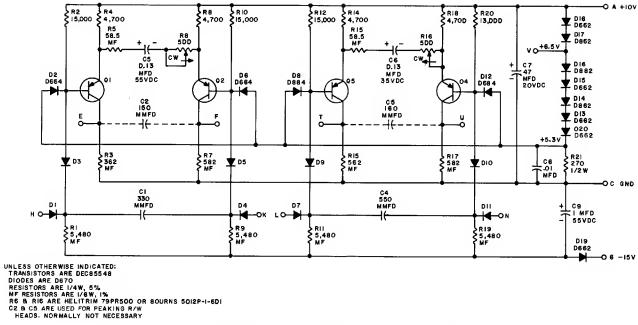

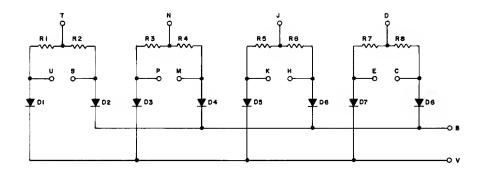

| 3.6.3 | G285 Series Selector Switch    | 3-17 |

| 3.6.4 | G286 Center Tap Selector       | 3-18 |

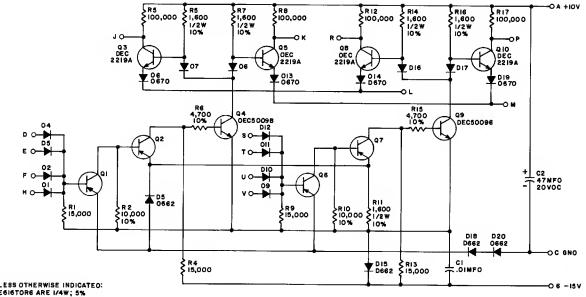

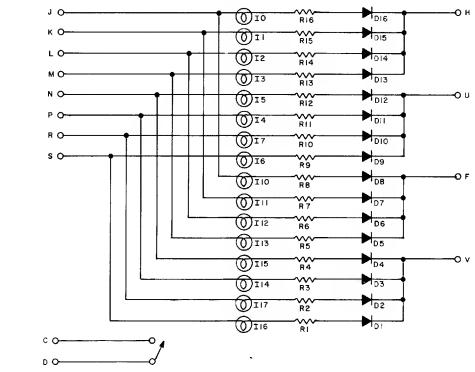

| 3.6.5 | G702 Disk Simulator            | 3-19 |

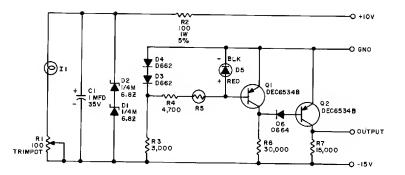

| 3.6.6 | 54–4073 Photocell Amplifier    | 3-20 |

| 3.6.7 | G680 Disk Head and Matrix      | 3-20 |

|       | CHAPTER 4<br>INSTALLATION      |      |

| 4.1   | Power and Cable Requirements   | 4-1  |

| 4.2   | Mounting Suggestions           | 4-2  |

## CHAPTER 5 MAINTENANCE

| 5.1   | Disk/Head Cleaning Procedure                          | 5-1 |

|-------|-------------------------------------------------------|-----|

| 5.1.1 | Disk Removal                                          | 5-1 |

| 5.2   | Troubleshooting                                       | 5-3 |

| 5.3   | Disk Operating Procedure for Timing Track Writer DF32 | 5-7 |

|       | ILLUSTRATIONS                                         |     |

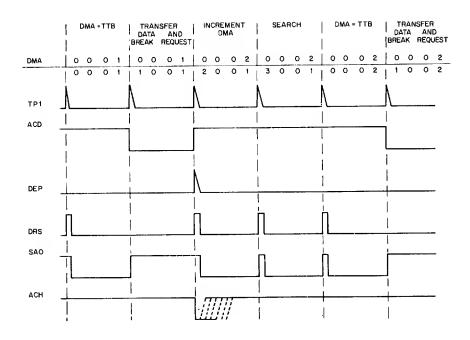

| 1-1 | DF32 System Block Diagram                     | 1-1 |

|-----|-----------------------------------------------|-----|

| 1-2 | DF32 Unit, Rack Mounted on Slide              | 1-4 |

| 1–3 | Disk File Assembly                            | 1-5 |

| 1-4 | Disk File Assembly, Read/Write Head Locations | 1-6 |

,

# ILLUSTRATIONS (Cont)

|     |                                                      | Page |

|-----|------------------------------------------------------|------|

| 2-1 | DF32 Operating Control Panels                        | 2-3  |

| 2-2 | DS32 Operating Control Panel                         | 2-3  |

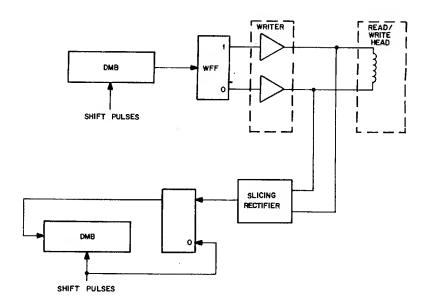

| 3–1 | Simplified Diagram of NRZI Recording                 | 3-3  |

| 3-2 | Simplified Diagram of Read and Write                 | 3-4  |

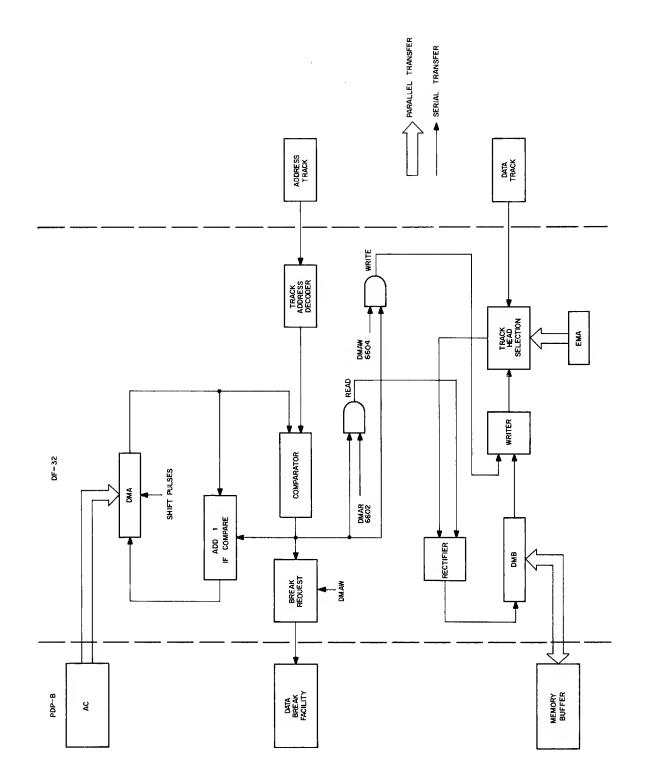

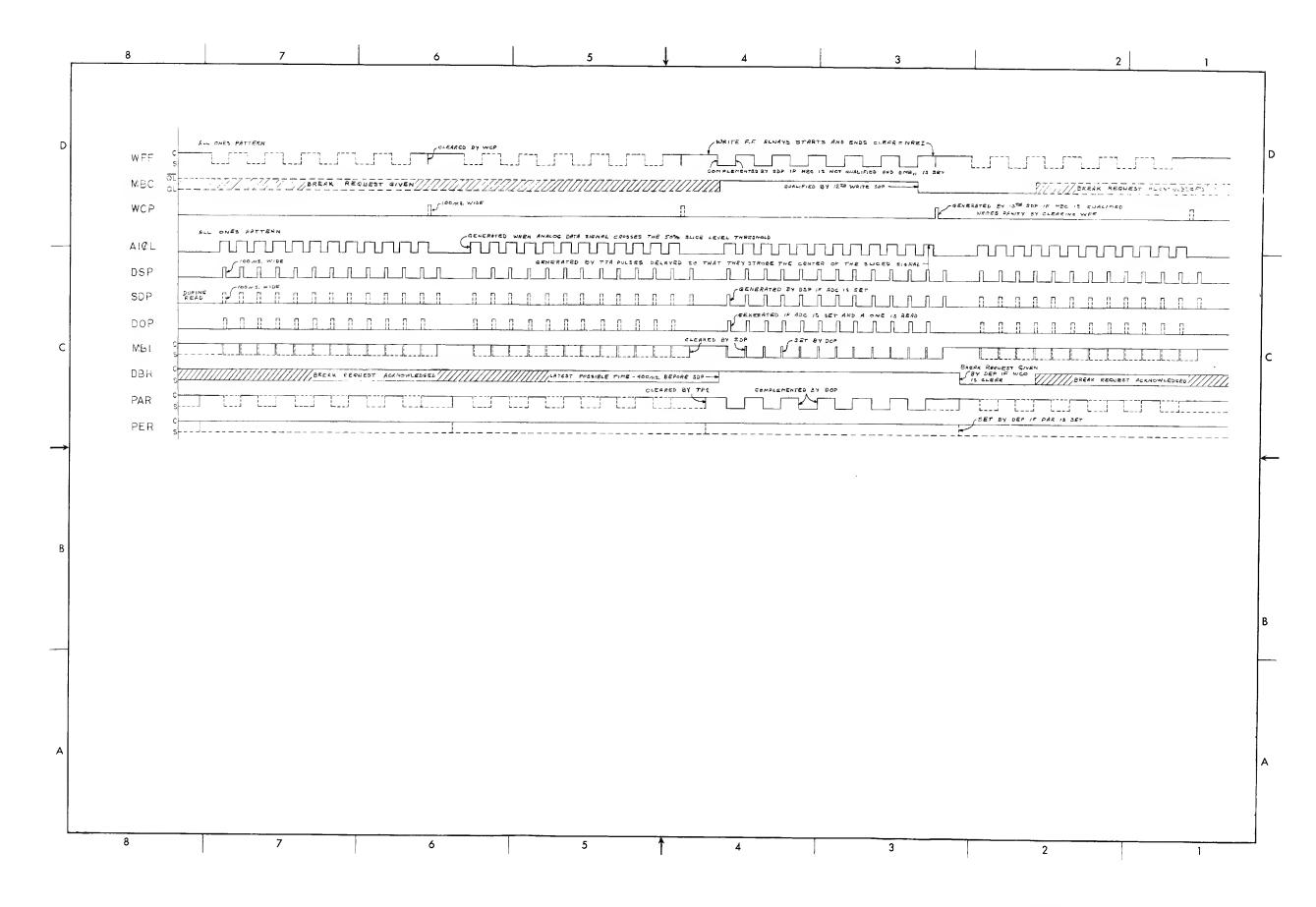

| 3-3 | Timing Diagram                                       | 3-10 |

| 3-4 | Block Diagram, G083 Differential Preamplifier Module | 3-16 |

| 3-5 | Block Diagram, G284 Disk Writer Module               | 3-17 |

| 3-6 | Block Diagram, G285 Series Selector Switch Module    | 3-18 |

| 3-7 | Block Diagram, G286 Center Tap Selector Module       | 3-19 |

| 3-8 | Block Diagram, G702 Disk Simulator Module            | 3-20 |

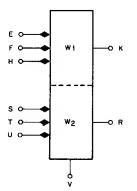

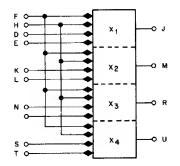

| 3-9 | Block Diagram, G680 Disk Head and Matrix Module      | 3-21 |

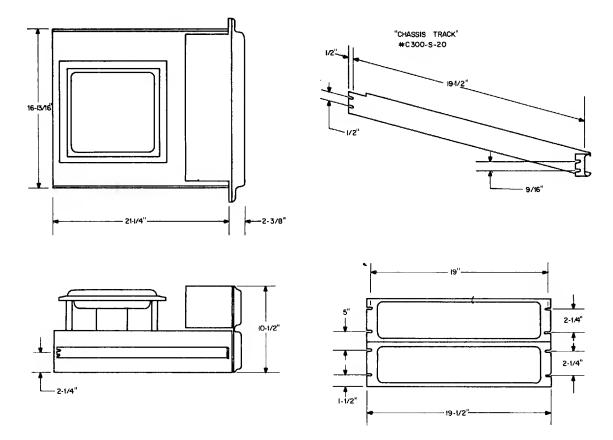

| 4-1 | Mounting Dimensions                                  | 4-2  |

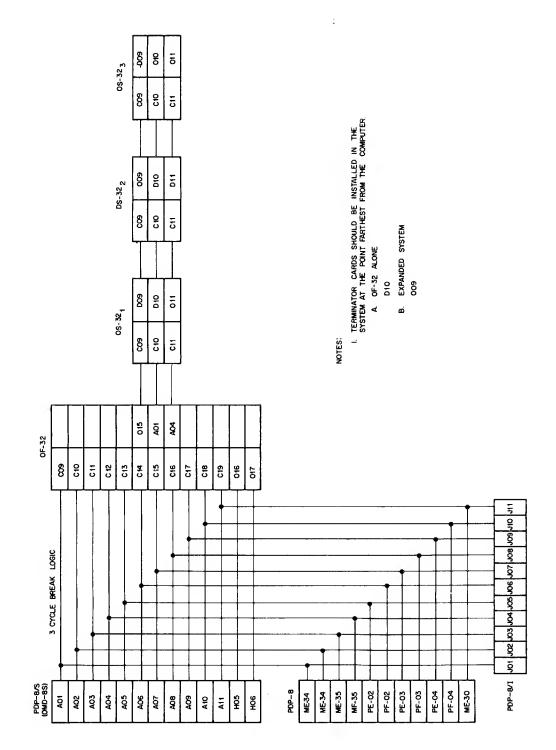

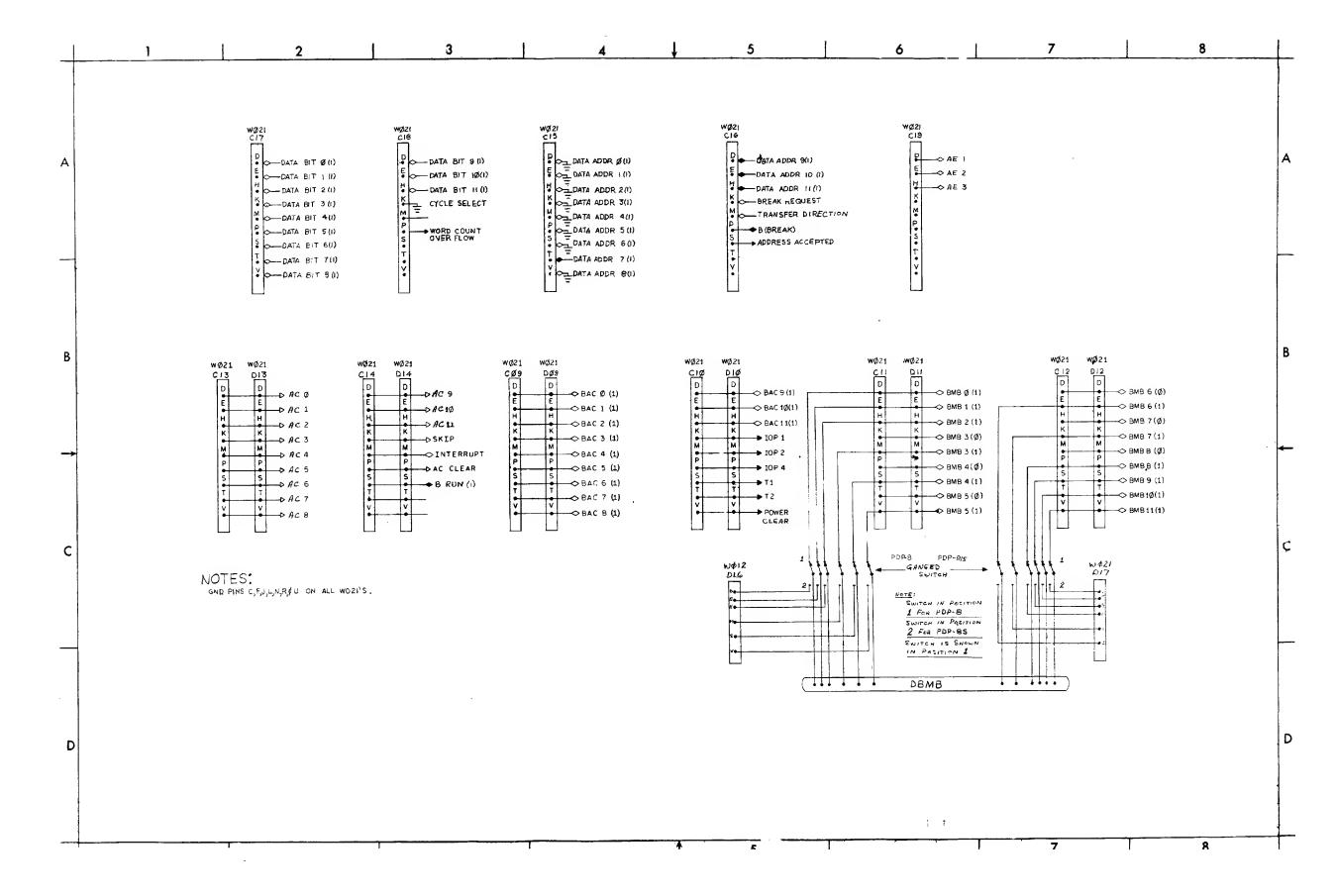

| 4-2 | PDP-8, PDP-8/S, PDP-8/I Cabling                      | 4-3  |

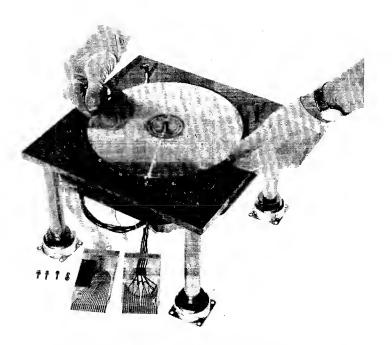

| 5-1 | Disk Removal                                         | 5-2  |

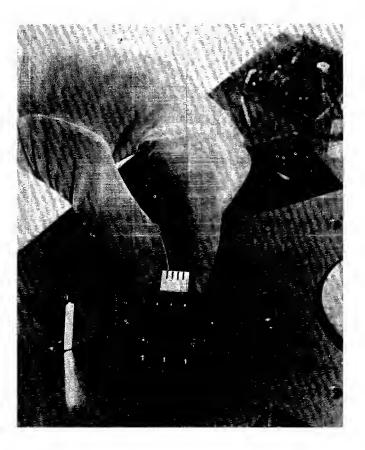

| 5-2 | Head Cleaning                                        | 5-2  |

| 5-3 | Timing Diagram for DF32 Disk Timing Track Writer     | 5-9  |

# TABLES

| 1–1 | Reference Documents                                 | 1-2  |

|-----|-----------------------------------------------------|------|

| 1-2 | Operation and Maintenance Programs                  | 1-3  |

| 1-3 | Disk File System Specifications                     | 1-3  |

| 2-1 | DF32 Logic Rack Controls                            | 2-2  |

| 2-2 | DS32 Logic Rack Controls                            | 2-2  |

| 2-3 | IOT Instructions                                    | 2-4  |

| 2-4 | IOT Instruction Analysis                            | 2-5  |

| 3-1 | Mnemonic Codes for DF32 Disk System                 | 3-5  |

| 3-2 | Mnemonic Codes for DF32 DECdisk Timing Track Writer | 3-14 |

Typical PDP-8/S and Disk File Installation

## CHAPTER 1 INTRODUCTION

The Type DF32 Disk File and Control, manufactured by Digital Equipment Corporation, Maynard, Massachusetts is a fast, random or sequential access, bulk storage device used with the PDP-8, PDP-8/S, or PDP-8/1 computers for memory expansion. The DF32 provides a capacity of 32,768 13-bit words which are stored on a rotating disk.

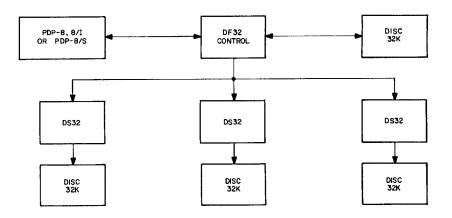

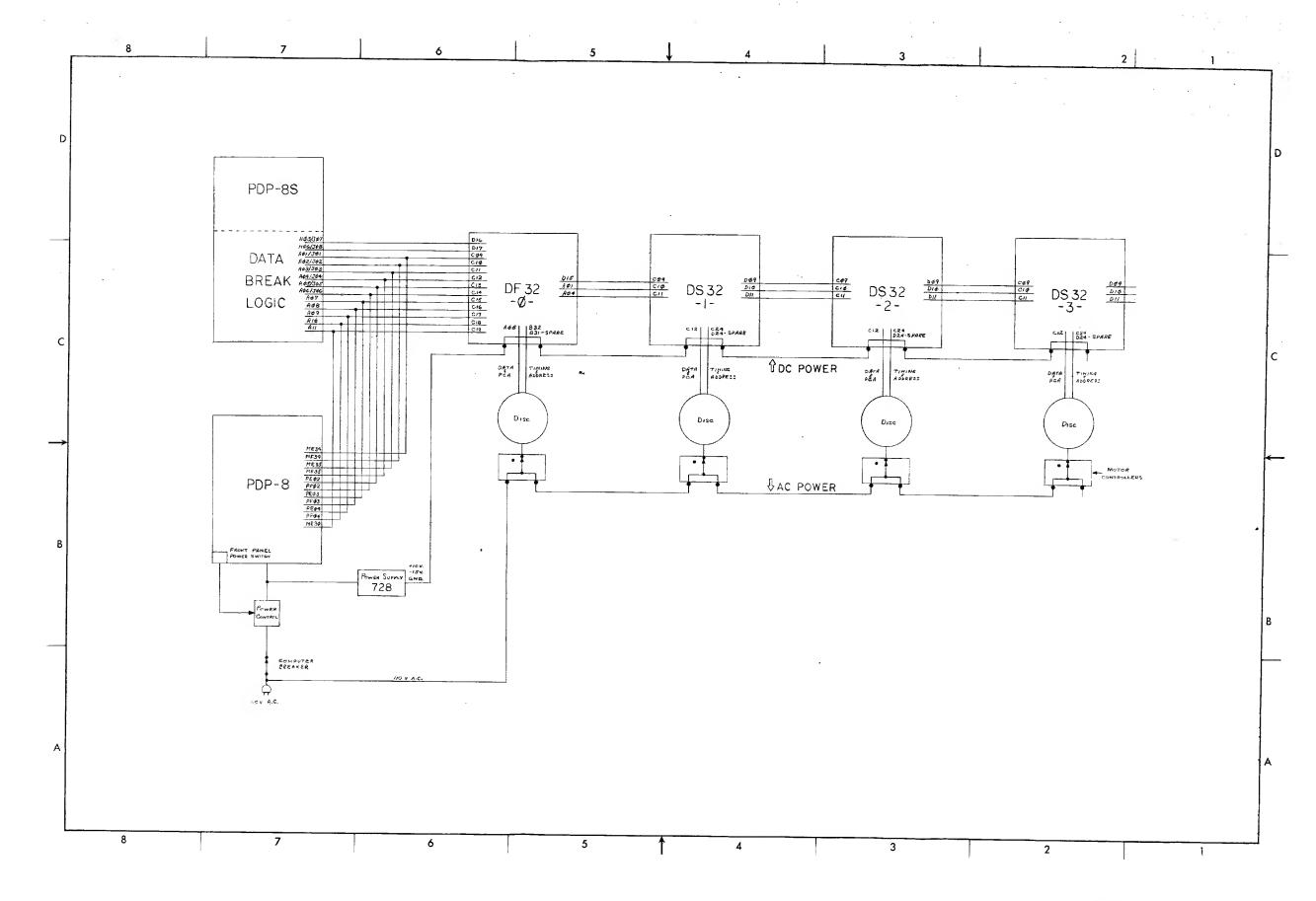

Up to three type DS32 Extender Disks can be attached to the DF32, each of which extends the bit capacity by 32K for a total of 131,072 13–bit words as shown in Figure 1–1.

The disk file is a program controlled device used in conjunction with the PDP-8, PDP-8/S, or PDP-8/I, and operates through the 3-cycle data break facility of the computers.

## 1.1 PURPOSE AND SCOPE

This manual and the referenced documents herein provides operation, programming, and maintenance information on both the Type DF32 Disk File and Control and DS32 Extender Disk. The programming information, which includes sample programs for storage access, is presented in sufficient detail to allow operating programs to be written. Although references throughout this manual are primarily made to the PDP-8 computer, the information may be assumed to apply equally to the PDP-8/I and PDP-8/S except where specifically noted otherwise.

Figure 1–1 DF32 System Block Diagram

The information in this manual is intended for use by persons familiar with DEC digital logic and the operation of the PDP-8, PDP-8/S, and PDP-8/1 computers. The maintenance information and routines require knowledge of the operation of bulk storage devices.

## 1.2 REFERENCE DOCUMENTS AND PROGRAMS

## 1.2.1 Manuals

Table 1-1 is a listing of the available publications which augment the information contained in this manual. These publications may be obtained upon request from the nearest DEC office or from the following address:

> Digital Equipment Corporation Main Street Maynard, Massachusetts

| Document                             | Description                                                                                 |

|--------------------------------------|---------------------------------------------------------------------------------------------|

| Digital Logic Handbook (C105)        | Function and specifications of FLIP-CHIP modules, cabinets, power supplies and accessories. |

| PDP-8 Maintenance Manual (F87)       | Theory, operation, and maintenance information on the PDP-8 Processor.                      |

| PDP-8/S Maintenance Manual<br>(F87S) | Theory, operation, and maintenance information on the PDP-8/S Processor.                    |

| PDP-8/1 Maintenance Manual           | Theory, operation, and maintenace information on PDP-8/I Processor.                         |

| Small Computer Handbook (C500)       | Describes operation and programming of PDP-8 and PDP-8/S computers .                        |

Table 1–1 Reference Documents

## 1.2.2 Operation and Maintenance Programs

Table 1–2 lists the operating and maintenance programs available for the DF32 and DS32 systems.

| Program                                    | Description                                                                                                |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------|

| DF32 Software Package                      | Perforated program tapes and description of symbolic assembly, assembly language, and utility subroutines. |

| DF32 Diskless Logic Tests<br>(Maintenance) | Tests master and extender logic without the disk in operation.                                             |

| DF32 Disk Data, Mini Disk<br>(Maintenance) | Tests the entire disk logic and disk including the interface, addressing and data.                         |

Table 1–2 Operation and Maintenance Programs

# 1.3 SYSTEM SPECIFICATIONS

The general specifications for the disk file systems are listed in Table 1-3.

| Storage capacity          | DF32 32,768 13-bit words<br>DS32 32,768 13-bit words per DS32<br>for a total of 131,072 words per system                                           |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 60-Hz power 50-Hz power                                                                                                                            |

| Data transfer rate        | 66 μs per word 80 μs per word                                                                                                                      |

| Average access time       | 16.67 ms 20.0 ms                                                                                                                                   |

| Write lock switches       | Inhibit writing on lower and/or upper 16K of any 32K disk sur–<br>face, and can inhibit one or more, or all disks in an expanded<br>memory system. |

| Addressing <b>s</b> cheme | Random or sequential addressing from 0 to 32,768 words, with variable block size from one word to 4,096 words.                                     |

| Data assembly             | Read/write to and from disk is in serial, with external transfer in parallel, by word.                                                             |

| Timing track              | One, with one spare.                                                                                                                               |

| Address track             | One, with one spare.                                                                                                                               |

| Data tracks               | 16                                                                                                                                                 |

| Words per track           | 2,048                                                                                                                                              |

| Recording method          | NRZI                                                                                                                                               |

| Density                   | 1100 bpi                                                                                                                                           |

| Operating environment     | Ambient temperature: Maximum: 32 to 130°F<br>Recommended: 70 to 85°F<br>Relative humidity: 20 to 80%                                               |

| Heat dissipation          | 500W                                                                                                                                               |

| Power requirements        | 117V, 60 Hz, single phase, ac, for DF32 or DS32<br>117V, 50 Hz, single phase, ac, for DF32A or DS32A                                               |

Table 1–3 Disk File System Specifications

## 1.4 PHYSICAL DESCRIPTION

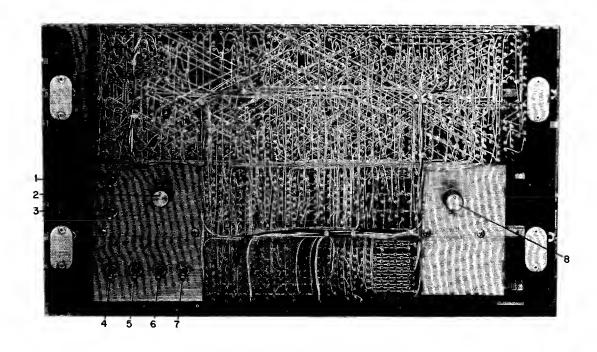

The DF32 interface, control logic, and mechanical components are mounted as an integral unit on a separate frame as shown on Figure 1–2. This unit can be installed within a DEC standard cabinet or any 19-in. relay rack. Track slides, attached on the side, allow the unit to be extended for servicing. The basic DF32 unit consists of two mounting panels for the DEC modules, with the wiring side facing the front of the unit. The disk file, consisting of a disk, drive motor, read/write heads, and photo cell amplifier are mounted separately at the rear of the unit. The overall dimensions of the DF32 are as follows: 10-1/2 in. high, 19 in. wide, 23-1/4 in. deep (21-1/4 in. deep from mounting surface, and 2-3/8 in. in front of mounting surface).

Each DS32 Extender is mounted on a similar frame with track slides and has the same dimensions as listed for the DF32. The DS32 unit, however, containing the disk file and analog-to-digital conversion logic, is controlled by signals and data supplied from the DF32. A complete extended memory system consisting of one DF32, three DS32 units, a Type 728 Power Supply and power control panel can be housed in a single bay of a standard rack or cabinet. When installed, sufficient cooling is provided by a fan mounted on the bottom of each unit. Additional system arrangements are also available to suit customer requirements.

Figure 1-2 DF32 Unit, Rack Mounted on Slide

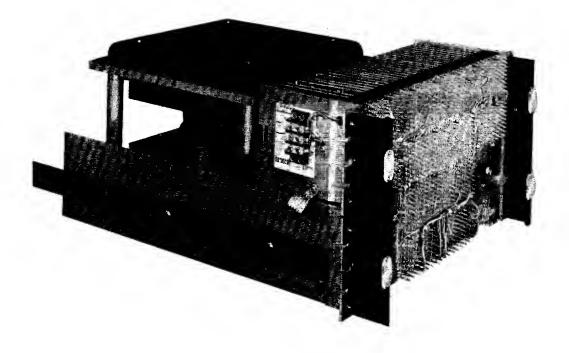

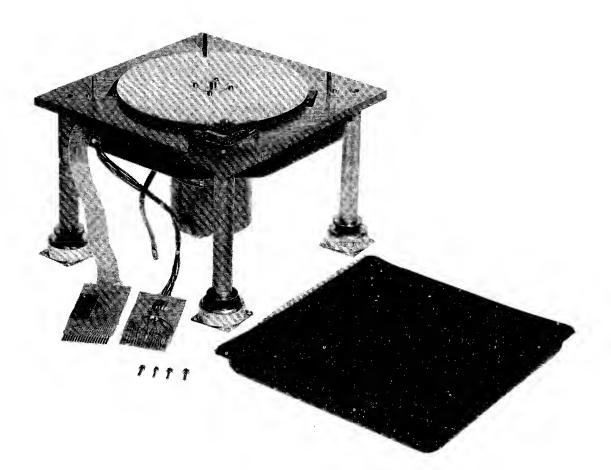

## 1.4.1 Disk File Assembly

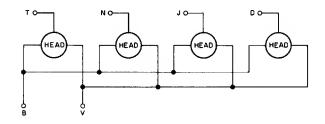

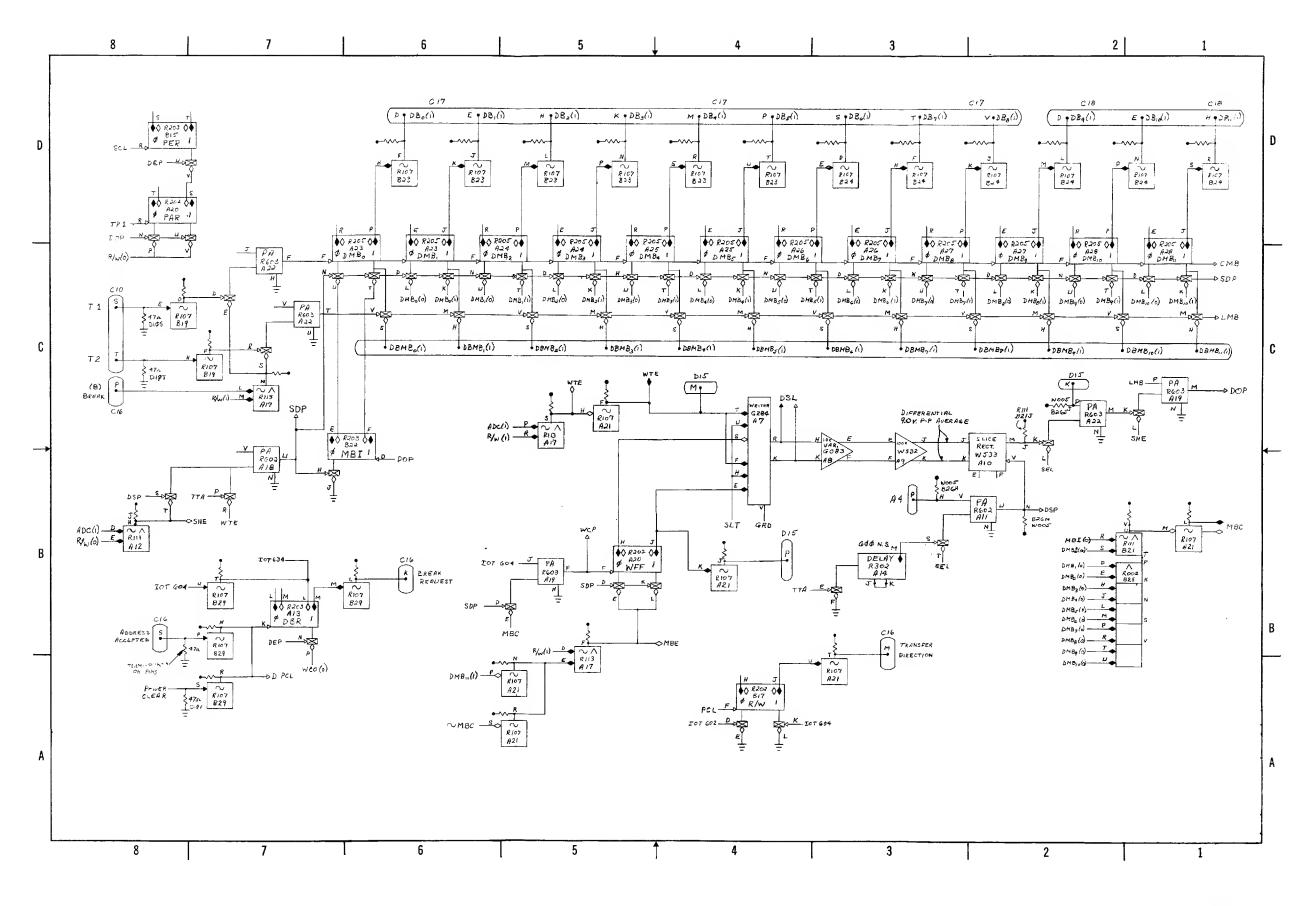

The disk file assembly is shown on Figure 1-3. The 16 read/write heads, four timing and address heads, photocell amplifier circuit, and drive motor are attached to the base plate which is suspended on four shock-absorbing mounts. The storage device is a nickel-cobalt plated disk that rotates with the motor shaft. The base plate and mounted components are completely enclosed by removable dust covers on the top and bottom as shown. Two connector cards provide timing, address signals, and data to the read/write heads cable. The physical position of the read/write heads on the base plate is shown on Figure 1-4.

Figure 1-3 Disk File Assembly (Cover Removed)

Figure I-4 Disk File Assembly, Read/Write Head Locations

## CHAPTER 2 OPERATION AND PROGRAMMING

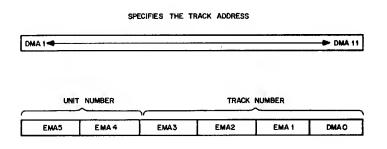

The programming of the DF32 is typical of an I/O device attached to the PDP-8. It uses the IOT instructions to control operation and the 3-cycle data break facility of the PDP-8 to transfer data between core memory and the DF32. The WC register (memory address 7750) of the data break facility specifies the number of word transfers, and the CA register (memory address 7751) of the data break facility specifies the current address of core memory that is to receive or send a word. The DF32 contains a memory buffer (DMB) to buffer the data between core memory and the disk; and a DMA (disk memory address) to specify the track address; the EMA (extended memory address) to specify the track and unit number. The formats of these registers are shown below.

There can be as many as four disk files within a system: one DF32 and up to three DS32 disk extenders. The disk extenders operate under the control of the DF32; therefore, only one disk file can be selected at any one time for data transfers (i.e., the control circuits handle only one block transfer at any one time).

The programming of each disk is functionally identical. Unit number assignment for each disk within the system is accomplished by the setting of a selection switch, provided on the front panel of each disk file unit. The program selects the desired unit by appropriately programming the EMA register. To ensure proper operation, each disk file within a particular system must be assigned its own unique unit number.

The storage capacity of each disk is 32,768 13-bit words, or 16 tracks of 2,048 13-bit words. If the specified data transfer encompasses more than one track, the data transfer operation continues automatically to the next track following one revolution of latency (33 ms). Similarly, operation continues to the next unit when the last track and track address have been accessed, provided that a next unit exists.

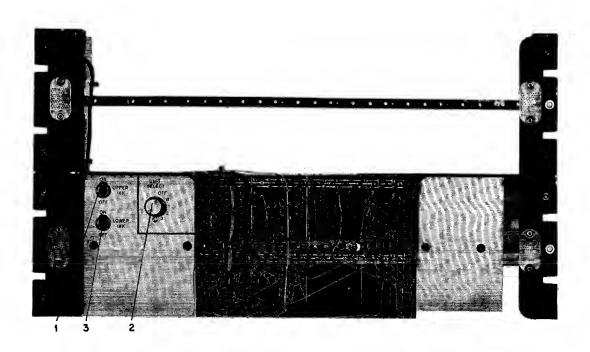

## 2.1 OPERATING CONTROLS

Tables 2–1 and 2–2 show the operating controls for the DF32 and DS32, respectively. Figures 2–1 and 2–2 show the control panels for the DF32 and the DS32, respectively.

# 2.2 IOT INSTRUCTIONS

Table 2–3 shows the IOT instructions for the DF32 system, and Table 2–4 shows a complete analysis of the IOT instructions.

| Number | Controls                     | Function                                                                                         |

|--------|------------------------------|--------------------------------------------------------------------------------------------------|

| 1      | Upper write lockout          | Inhibits writing on the upper 16K word position of the DF32.                                     |

| 2      | Unit select                  | Assigns disk address 0, 1, 2, or 3.                                                              |

| 3      | Lower write lockout          | Inhibits writing on the lower 16K word position of the DF32.                                     |

| 4      | Disk lockout 0               | Enables write lockout selection on unit 0.                                                       |

| 5      | Disk lockout 1               | Enables write lockout selection on unit 1.                                                       |

| 6      | Disk lockout 2               | Enables write lockout selection on unit 2.                                                       |

| 7      | Disk lockout 3               | Enables write lockout selection on unit 3.                                                       |

| 8      | PDP-8, PDP-8/I<br>or PDP-8/S | Processor selection enables the system, through interface, to be employed with both processors . |

Table 2–1 DF32 Control Panel Functions

| Tab          | le 2-2 |           |

|--------------|--------|-----------|

| DS32 Control | Panel  | Functions |

| Number | Controls            | Function                                                                                                                    |

|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1      | Upper write lockout | Inhibits writing on the upper 16K word positions on the extension unit.                                                     |

| 2      | Ųnit select         | Assigns disk address , permitting the extender unit to be operated with the master unit or as an additional extender unit . |

| 3      | Lower write lockout | Inhibits writing on the lower 16K word position on the extend-<br>er unit.                                                  |

Figure 2–1 DF32 Operating Control Panels

Figure 2-2 DS32 Operating Control Panel

| T   | able | 2-  | -3   |    |

|-----|------|-----|------|----|

| IOT | Inst | ruc | tion | ۱S |

| Mnemonic | Octal<br>Code | Operation                                                                                                                                                                                                                                                                                                         |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCMA     | 6601          | Clear the disk memory address register, parity error, and completion flags.<br>This instruction clears the disk memory request flag and interrupt flags.                                                                                                                                                          |

| DMAR     | 6603          | Load the disk memory address with information (initial address) in the ac-<br>cumulator. Then clear the AC. Begin to read information from the disk<br>into the specified core location. Clear parity error and completion flags.<br>Clear interrupt flags AC <sub>0-11</sub> DMA <sub>0-11</sub> .               |

| DMAW     | 6605          | Load the disk memory address register with information (initial address) in<br>the accumulator (AC); then clear the AC. Begin to write information onto<br>the disk from the specified core location. Clear parity error and completion<br>flags. Clear interrupt flags. AC <sub>0-11</sub> DMA <sub>0-11</sub> . |

| DCEA     | 6611          | Clear the disk extended address and memory address extension register.                                                                                                                                                                                                                                            |

| DSAC     | 6612          | Skip next instruction if the address confirmed flag is a 1. Flag is set for 16 $\mu s$ (AC is cleared).                                                                                                                                                                                                           |

| DEAL     | 6615          | Clear the disk extended address and memory address extension register .<br>Then load the disk extended address and memory address extension registers<br>with the track address data held in the accumulator .                                                                                                    |

|          |               | IOT 6615 (TRANSMIT TO DF32)                                                                                                                                                                                                                                                                                       |

|          |               |                                                                                                                                                                                                                                                                                                                   |

|          |               | AC 128K 96K 64K 32K 16K F4 F2 F1                                                                                                                                                                                                                                                                                  |

|          |               | IOT 6616 (RECEIVE STATUS FROM 0F32)                                                                                                                                                                                                                                                                               |

|          |               | AC CELL 128K 96K 64K 32K 16K F4 F2 F1 DATA WRITE PARITY<br>SYNC 128K 96K 64K 32K 16K F4 F2 F1 REQ. LOCK OR ERRORS                                                                                                                                                                                                 |

|          |               | * WRITE LOCK SWITCH STATUS IS TRUE ONLY WHEN<br>DISK MODULE CONTAINS WRITE COMMANO.                                                                                                                                                                                                                               |

| DEAC     | 6616          | Clear the accumulator. Then load the contents of the disk extended address register into the accumulator to allow program evaluation. Skip next in-<br>struction if address confirmed flag is a 1.                                                                                                                |

## Table 2–3 (Cont) IOT Instructions

| Mnemonic | Octal<br>Code | ,<br>Operation                                                                                                                                                      |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFSE     | 6621          | Skip next instruction if the parity error, data request late, or write lock<br>switch flag is a 0 (no error).                                                       |

| DFSC     | 6622          | Skip next instruction if the completion flag is a 1 (data transfer is complete).                                                                                    |

| DMAC     | 6626          | Clear the accumulator. Then load the contents of the disk memory address register into the accumulator to allow program evaluation.<br>$DMA_{0-11}^{>}AC_{0-11}^{}$ |

|          |               | During read the final address will be the last address transferred +1.<br>During write the final address will be the last address transferred.                      |

Table 2–4 IOT Instruction Analysis

| IOT INSTRUCTIONS |     |                                                                                                                                                                                                                                        |  |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| a.               | 660 | 601: DCMA                                                                                                                                                                                                                              |  |

|                  | (1) | Generates SCL (start clear) which clears:                                                                                                                                                                                              |  |

|                  |     | (a)TRC flip-flopTransfer Complete(b)NED flip-flopNonexistent Disk(c)MRS flip-flopMemory Request Sync(d)ADC flip-flopAddress Confirmed(e)ACH flip-flopAddress Compare Hold(f)DRL flip-flopData Request Late(g)PER flip-flopParity Error |  |

|                  | (2) | Generates DTC (Disk Time Clear) which clears:                                                                                                                                                                                          |  |

|                  |     | (a)MWR flip-flopMemory Word Request(b)TCA flip-flopTime Counter "A"(c)TCB flip-flopTime Counter "B"                                                                                                                                    |  |

|                  | (3) | Clears the disk memory address register                                                                                                                                                                                                |  |

| b.               | 660 | 2:                                                                                                                                                                                                                                     |  |

|                  | (1) | Clears the accumulator                                                                                                                                                                                                                 |  |

|                  | (2) | Clears the R/W (read/write) flip-flop setting transfer direction to read.                                                                                                                                                              |  |

|                  | (3) | Generates LAD (load address) which:                                                                                                                                                                                                    |  |

|                  |     | <ul> <li>(a) Does ones transfer from the accumulator to the disk memory address register.</li> <li>(b) Clears WCO flip-flop (word count overflow)</li> <li>(c) Sets MRS flip-flop</li> </ul>                                           |  |

## Table 2–4 (Cont) IOT Instruction Analysis

- 6604: с. (1) Clears the accumulator (2) Sets the R/W flip-flop, setting transfer direction to write. (3) Generates LAD (see Section b, Paragraph 3). (4) Sets DBR flip-flop (data break request). NOTE Combinations of the 660X IOT's are 6603 DMAR (Read) 6605 DMA₩ (Write) d. 6611: DCEA (1) Clears disk extended memory address register. (2) Clears extended address register (for extended memory in computer). e. 6612: DSAC (1) Enables skip bus if ADC flip-flop is set (used primarily in diagnostic programming) (2) Clears the accumulator f. 6614: (1) Does ones transfer from accumulator bits 1 through 5 to the disk extended address register. (2) Does ones transfer from disk "status register" to accumulator bits 0 through 11. NOTE Combinations of 661X IOT's are 6615 DEAL (Clear and Load disk EMA register) 6616 DEAC (0--AC, load AC with disk EMA) 6621: DFSE g. (1) Enables skip bus if no error flags are up (skip on no error) h. 6622: DFSC (1) Enables skip bus if the TRC flip-flop is set and computer MB bit 9 is a zero

- (IOT 6622 used alone).

- (2) Enables clear bus if computer MB bit 9 is a one. (IOT 6622 used with IOT 6624.)

#### Table 2-4 (Cont) IOT Instructions

- i. 6624:

- Does a ones transfer from disk memory address register to accumulator bits 0 through 11.

#### NOTE

#### Combinations of 662X IOT's are

6626 DMAC (0--AC and load AC with DMAR)

#### Maintenance IOT Instructions

- a. 6631: TAS (TTA simulator) Generates false TTA pulses for static logic test.

b. 6632: TBS (TTB simulator) Generates false TTB pulses for static logic test.

c. 6634: DBRS

- Sets data break request flip-flop for static logic test.

## 2.3 INTERRUPT FLAGS

There are two flags that generate an interrupt: the NED (nonexistent disk) and the TRC (transfer complete) flags. The NED flag is set when the program selects (via EMA) a unit which does not exist, or the data transfer operation increments the EMA to next unit and it does not exist. A non-existent unit means that the program has selected a unit number and no disk file is set to that unit number.

The TRC flag signifies the end of the data transfer. It is set at the completion of the last word transfer by the disk, following a word count overflow of the WC register. The completion flag can be sensed by the DFSC instruction.

### 2.4 ERROR FLAGS

The error flags can be sensed by the IOT 6621 instruction. The program skips when no error exists. The error flags are described in the following paragraphs.

#### 2.4.1 DRL Flag

The DRL (data request late) flag signifies: 1) that a data transfer operation occurred between the disk DMB and the disk before the previous transfer was handled by the data break facility, 2) that address accepted was not received back from the computer, leaving the break request flag up.

## 2.4.2 PER Flag

The PER (parity error) signifies that a parity error occurred before the read operation.

#### 2.4.3 WIA Flag

This flag signifies that a write operation was attempted on the lower 16K memory addresses of the DF32 when they were locked ut by the write lockout switches.

## 2.4.4 WIB Flag

Same as WIA except on upper 16K of disk memory.

## 2.4.5 EWL Flag

Signifies that a WIA or WIB error occurred on a selected disk expander. When sensed by the DEAC instruction, WIA, WIB, and EWL are contained in the same list.

## 2.5 ADC FLAG

The ADC (address confirmed) flag is used only in diagnostic programming. It signifies that the DMA corresponds to the track address currently passing under the read/write heads and is available for only 16 µs. It can be sensed by the IOT 6612 instruction which skips if the flag is set.

### 2.6 STATUS EVALUATION

The status of certain conditions can be evaluated by using the IOT 6614 instruction. The IOT 6614 (DEAC) loads the AC with the status as shown below.

- AC0 PSM (photo sync mark) which specifies that the disk gap is presently passing under the read/write head. It is available for  $200 \,\mu s$ .

- AC1-AC5Respectively, EM5 through EM1.AC6-AC8Respectively, EA3 through EA1.AC9DRL flagAC10NED or EWL flagAC11PER flag

## 2.7 PROGRAMMING EXAMPLE

A programming example that writes a block of data onto the disk is shown below. For simplicity, the example assumes that all data and instructions are within the same page, but in actual practice this may not be true.

|      |                                                 |                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUB, | /CALLING SE<br>JMS<br>Ø<br>Ø<br>Ø<br>XXX        | QUENCE<br>WRT           | /JUMP TO WRITE SUBROUTINE<br>/CONTAINS WORD COUNT<br>/CONTAINS INITIAL CORE MEMORY ADDRESS<br>/CONTAINS TRACK AND UNIT NUMBER<br>/CONTAINS TRACK ADDRESS<br>/CONTINUE WITH MAIN PROGRAM                                                                                                                                                                                                                                                                                                                                                            |

|      | /WRITE SUBRC                                    |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WRT, | Ø<br>TAD I<br>DCA<br>ISZ<br>TAD I<br>DCA<br>ISZ | WRT<br>WC<br>WRT<br>WRT | /ENTER WRITE SUBROUTINE<br>/FETCH WORD COUNT<br>/DEPOSIT IN WORD COUNT REGISTER<br>/INCREMENT POINTER<br>/FETCH INITIAL CORE MEMORY ADDRESS<br>/DEPOSIT INTO CURRENT ADDRESS REGISTER<br>/INCREMENT POINTER<br>/FETCH TRACK AND UNIT NUMBER<br>/DEPOSIT INTO REGISTER IN DF32 CONTROL<br>/CLEAR AC<br>/INCREMENT POINTER<br>/FETCH TRACK ADDRESS<br>/TRACK ADDRESS TO DMA IN DISC; START<br>/WRITE OPERATION<br>/JOB DONE?<br>/NO, WAIT<br>/ANY ERRORS?<br>/YES, GO TO ERROR SUBROUTINE<br>/NO, INCREMENT POINTER TO EXIT ADDRESS<br>/EXIT PROGRAM |

The calling subroutine must be set up so that the subsequent locations to SUB (SUB+1, SUB+2, etc.) contain the parameters as shown in the comments column. The format of location SUB+3 must conform to that shown in Table 2-3 for the DEAC instruction.

The JMS WRT instruction causes a subroutine jump to location WRT with the contents of the PC+1 (which contains symbolic address SUB+1) deposited into location WRT. Since location WRT now contains SUB+1, the first instruction of the subroutine (TAD | WRT) loads the AC with the contents of SUB+1 which is the word count. The word count is then deposited into the WC register. Similarly, the initial address is deposited into the CA register. The program then proceeds to set up the EMA and DMA registers and start the write operation. After the DMAW instruction is issued, the data transfer operation begins and continues independently of the program; it operates under the control of the data break facility to transfer data. When the transfer is complete, the TRC (transfer complete) flag comes up and, when sensed by the DFSC control, passes to the DFSE instruction. DFSE then senses for errors, and if any, control jumps to an error or diagnostic (not shown) routine. If no errors, control exits from the subroutine back to the main program to resume main processing.

It should be noted that since the data transfer operates independently of the program, the subroutine could be exited following the DMAW instruction. An interrupt subroutine could handle the post data transfer processing since the TRC flag generates an interrupt.

An identical program could handle data transfers for a read operation except that the DMAW instruction is replaced by the DMAR instruction.

.

#### CHAPTER 3 PRINCIPLES OF OPERATION

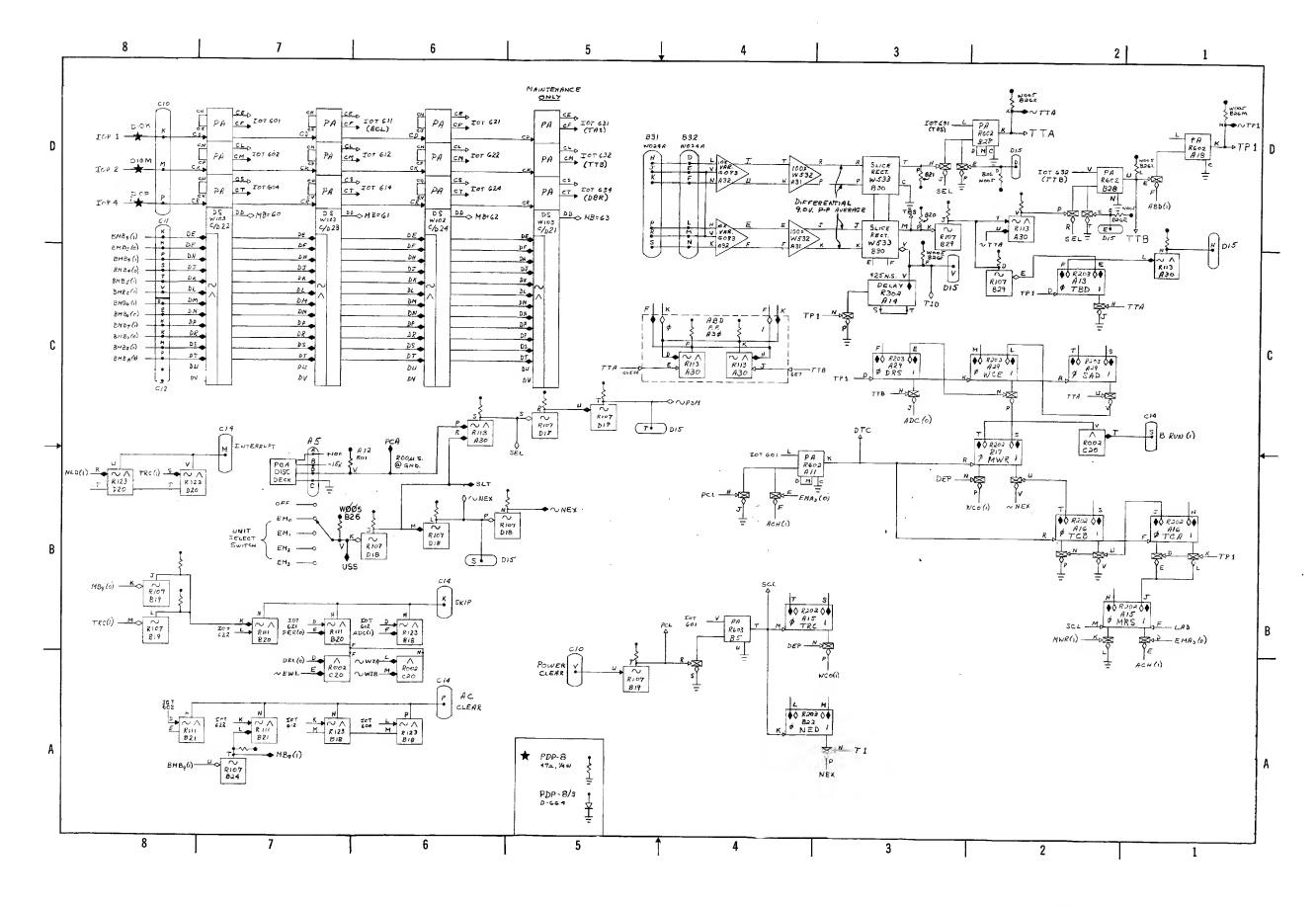

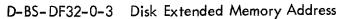

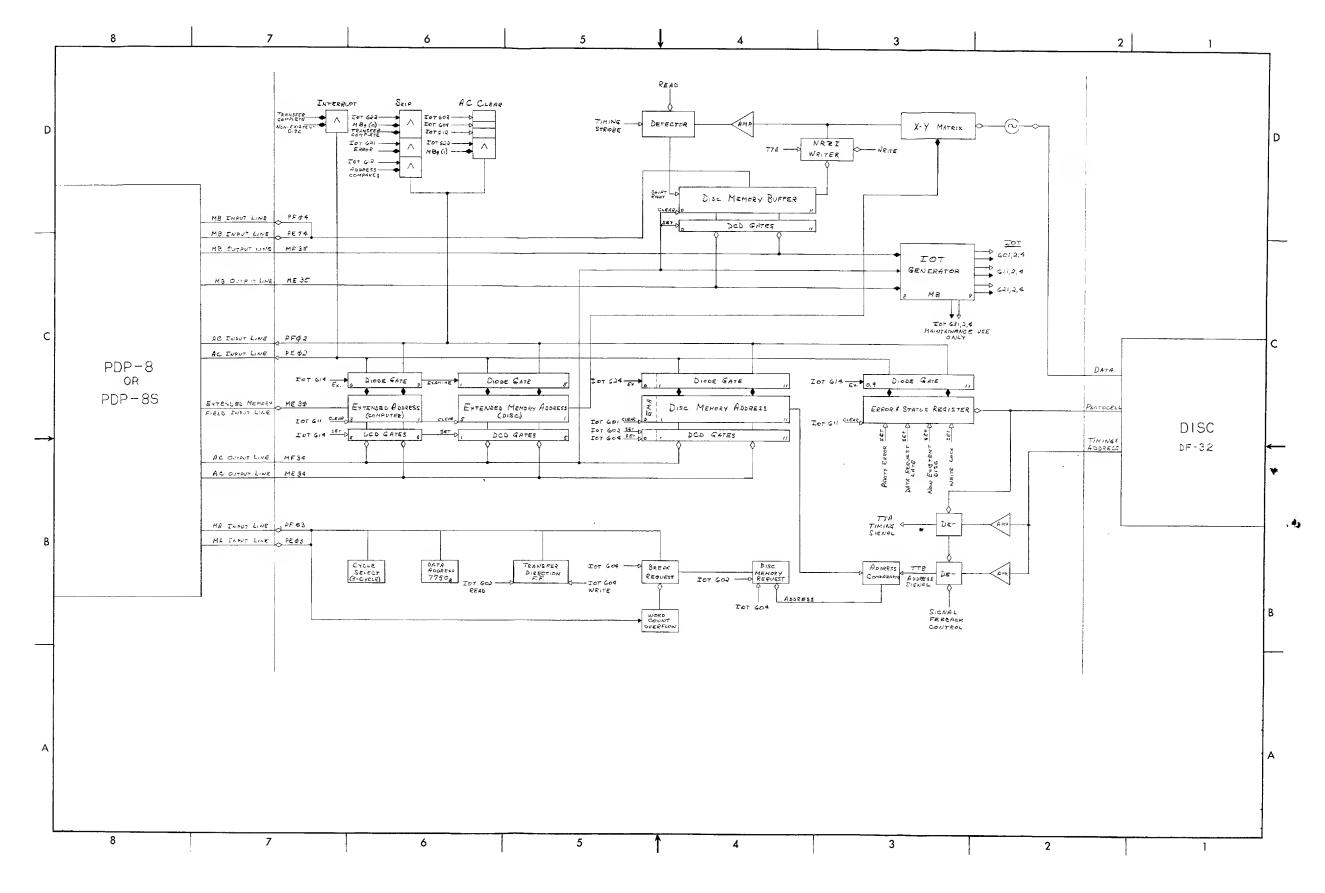

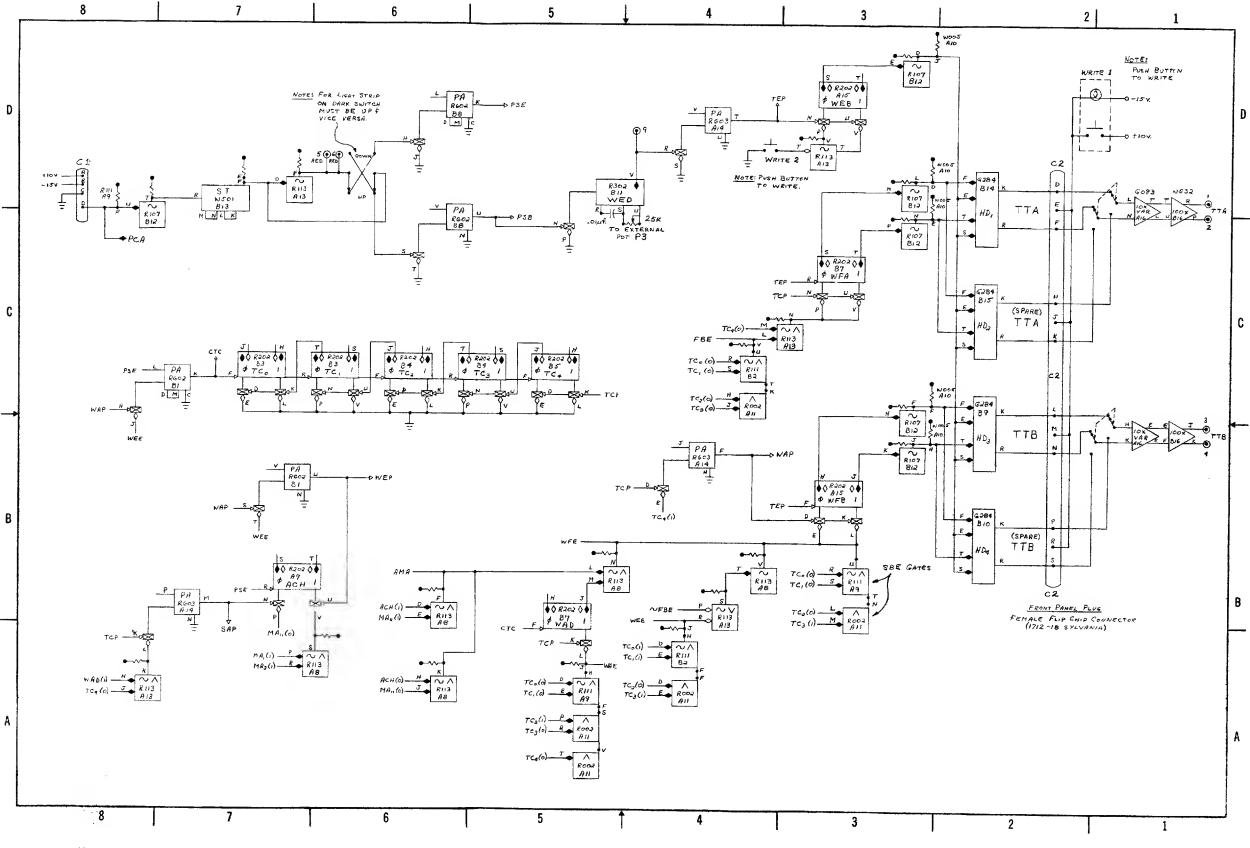

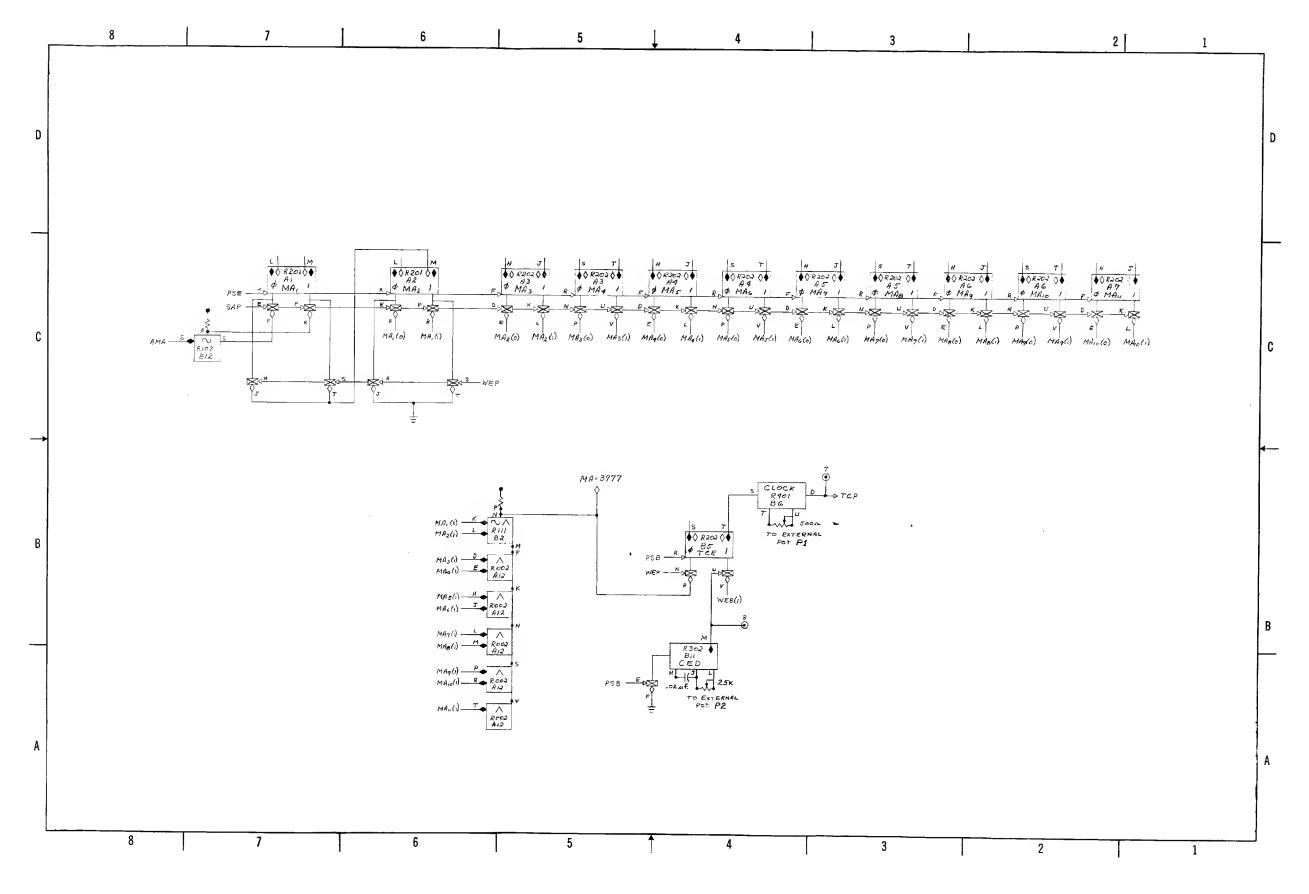

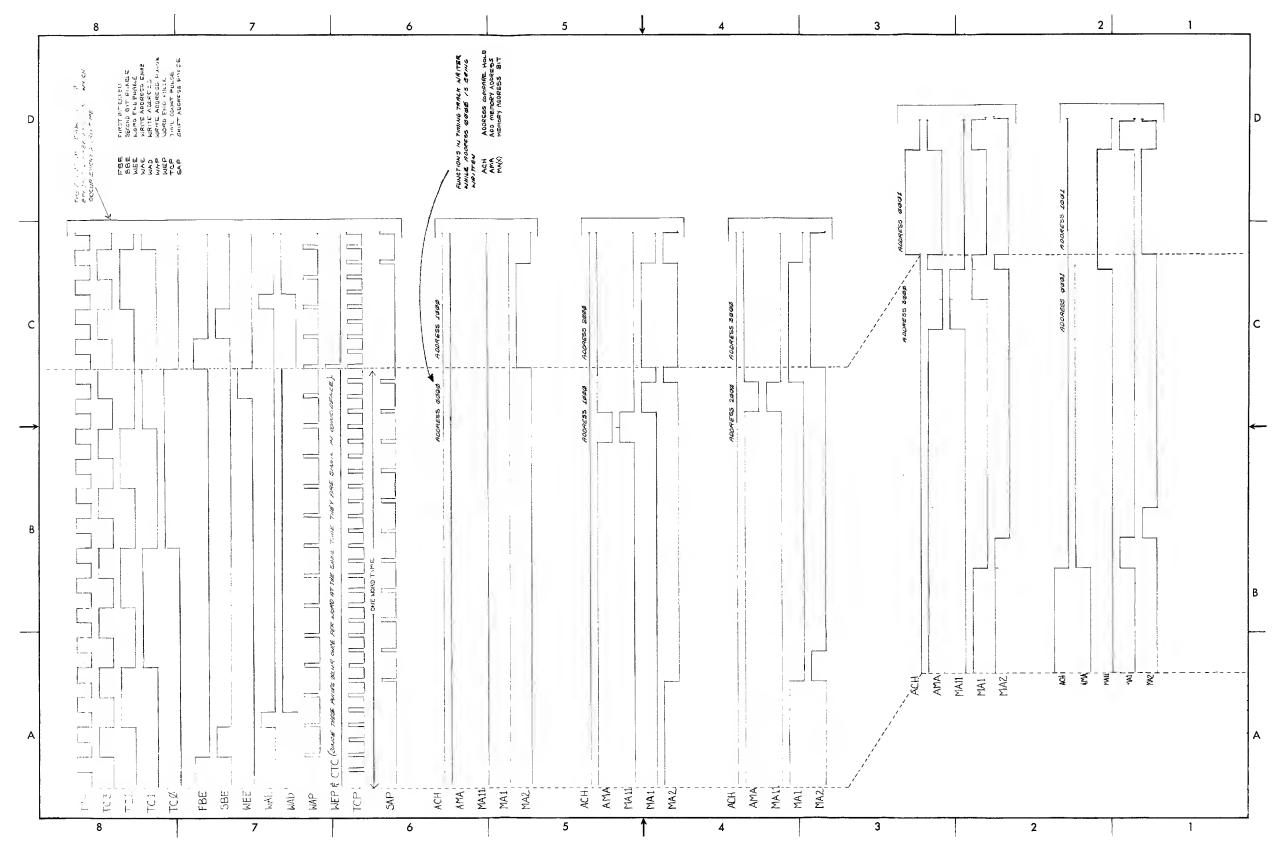

This chapter describes the principles of operation of the DF32 Disk File System. Descriptions of the logic circuits in this chapter refer to the logic drawings included in Chapter 6.

A disk file system can consist of one DF32 Disk File and up to three DS32 Disk Extenders. The Disk Extender is a disk file that operates under the control of the DF32. Each of the disk files has a unit select switch whereby a disk can be assigned a unit number by the operator. The disk file executive program then selects the unit for a data transfer operation. If the program selects a disk file that is not selected by the unit select switch, no data transfer occurs, and the program is notified of this NED (nonexistent disk) condition by an interrupt.

The DF32 system uses the three-cycle data break facility of the PDP-8 to transfer data. The WC (word count) and CA (current address) registers are used to specify the number located in the memory core of the computer and the core memory address, respectively, of the data transfer. Initially, the program loads the WC register with the 2's complement of the number of word transfers and the CA register with the initial core memory address -1. Thereafter, the CA and WC are incremented after each data transfer.

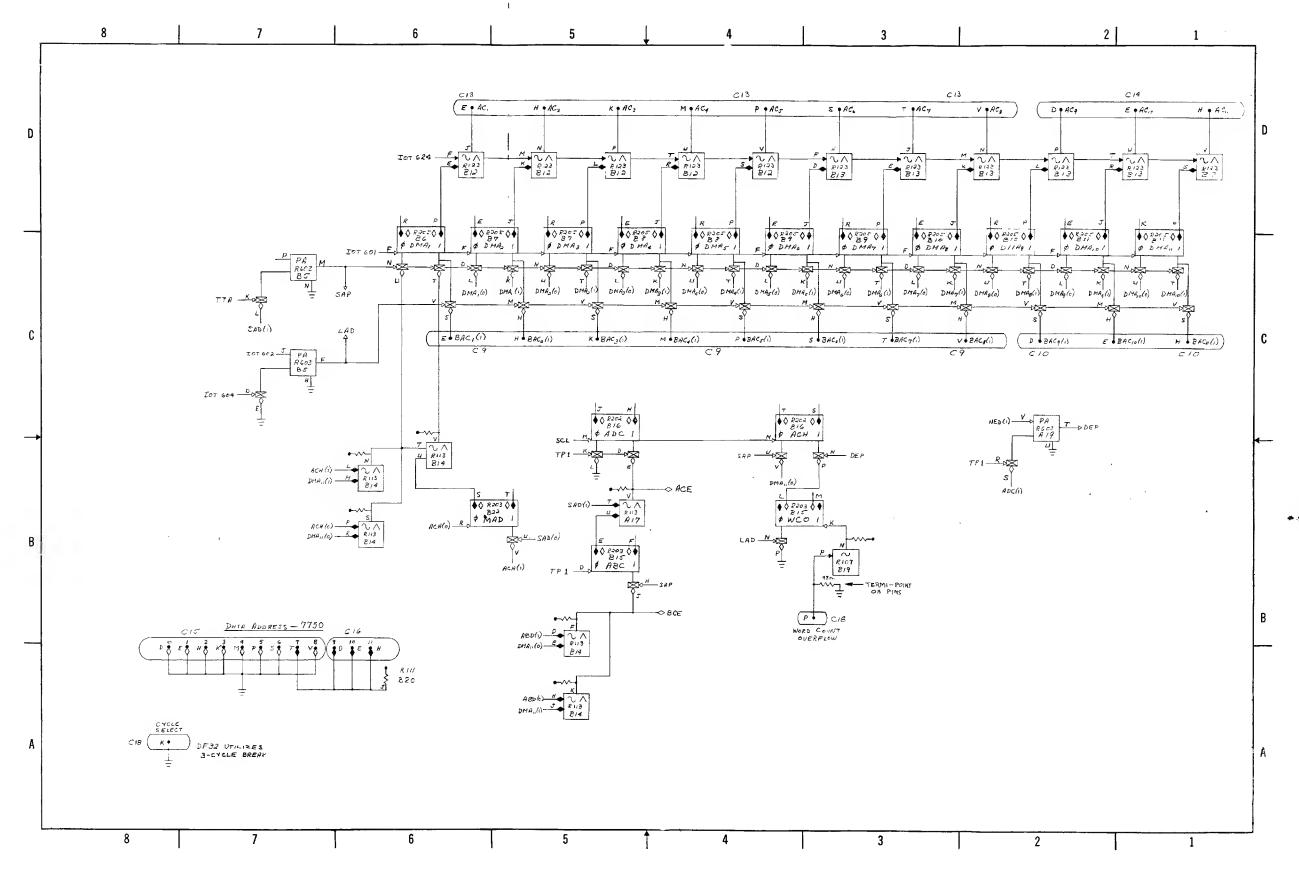

After the program sets up the WC and CA registers, it issues a DEAL instruction to load the EMA (extended memory address) which specifies the track number and the unit number (Dwg No. D-BD-DF32-0-9). If a write operation is specified, the DMAW instruction is issued to load the DMA (disk memory address) register to specify the track word address that is to receive the word transfer. The DMAW also initiates a data break request so that the first word to be recorded is loaded into the DMB (disk memory buffer). The write operation then transfers the content of the DMB to the addressed track. After each transfer, the DMA is incremented to address the next track address. Operation continues until the WC register is reduced to zero. When this occurs, a WCO (word count overflow) signal is sent to DF32 control to terminate operation.

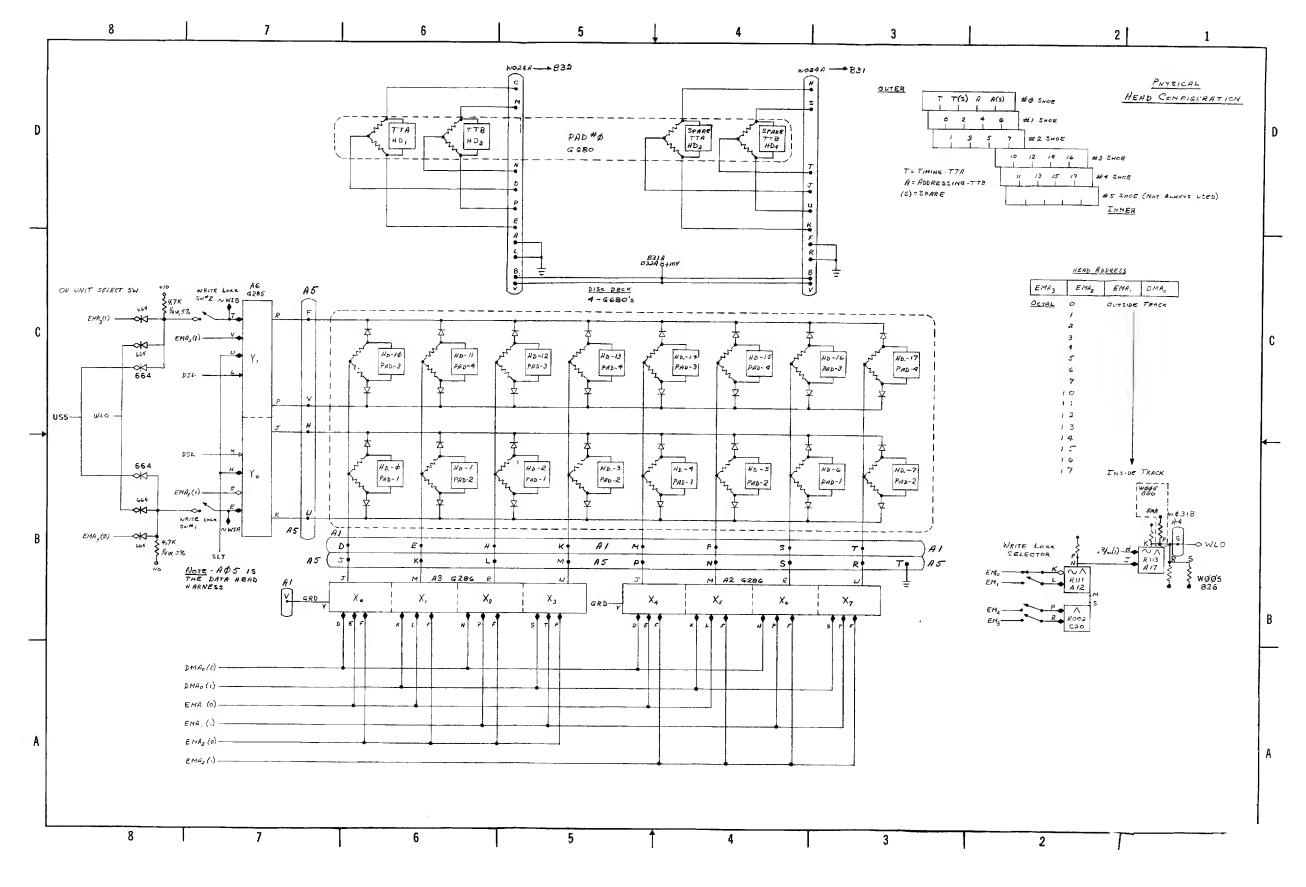

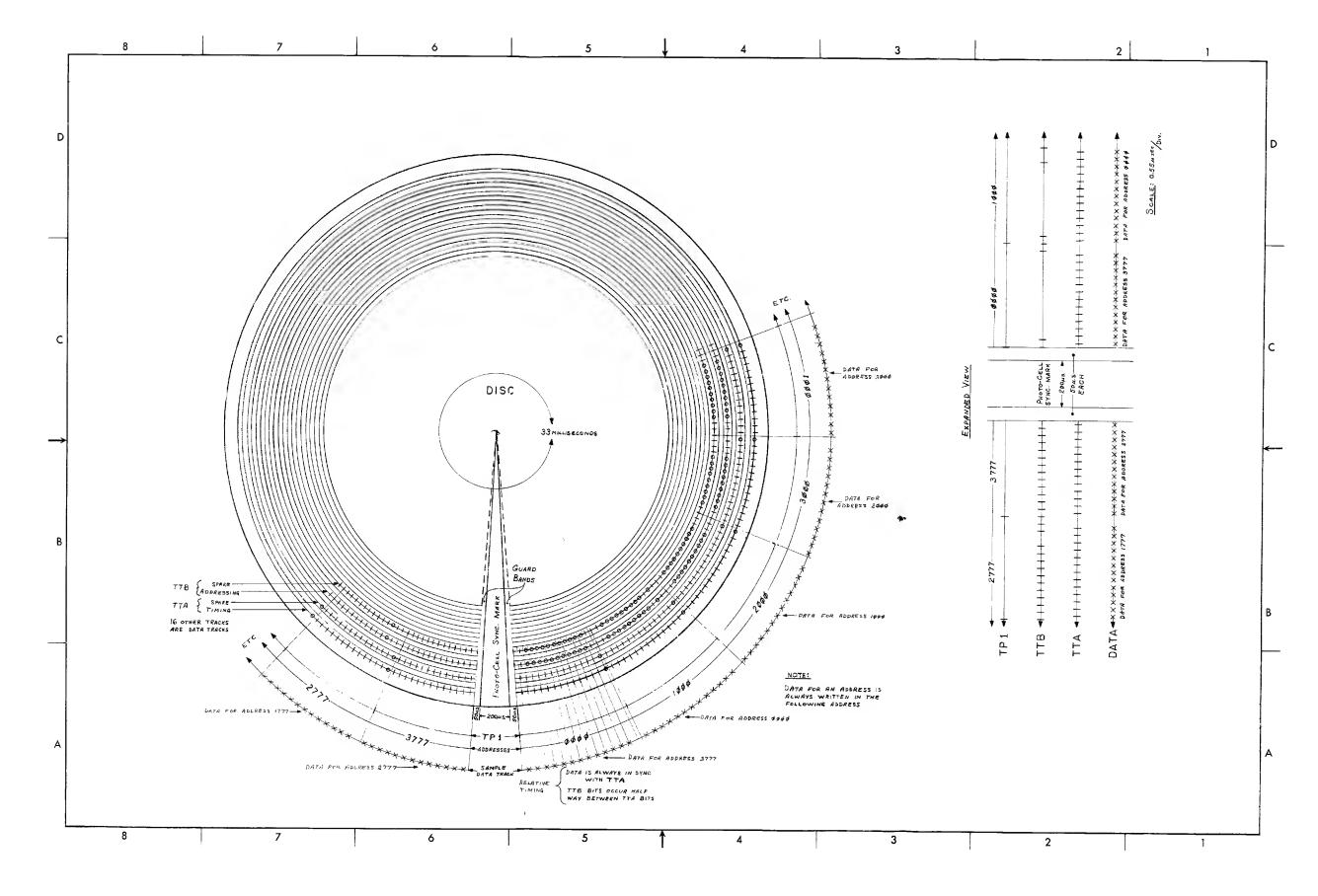

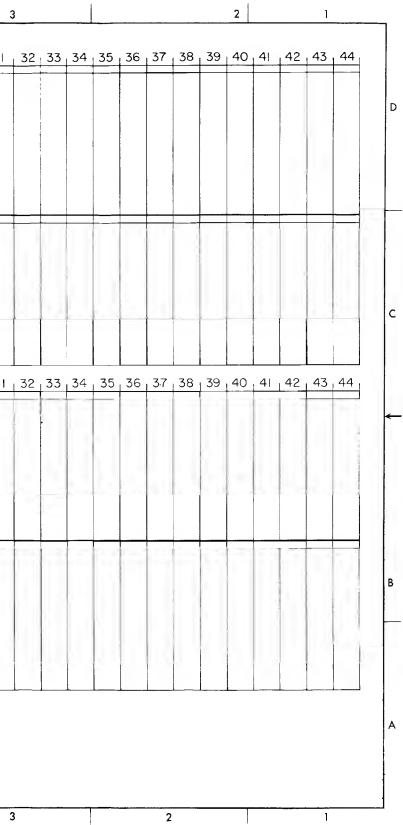

## 3.1 DISK FORMAT

The disk format is shown in Dwg. No. D-TD-DF32-0-11. There are 16 data tracks on which data may be recorded or read. Each track can record 2048 13-bit words (12 data bits plus a parity bit). To synchronize recording or reading, the disk contains two TTA (including one spare) and TTB (including one spare) timing tracks. The TTB track contains the track address information and during operation the TTB pulses provide the control circuits with the track address presently passing under the track head. It requires one track address period (time for the TTB serial pulses to define a track address) for the control circuits to determine the present track address. For example, if the track address is 0000, by the

3-1

time address 0000 is recognized, 1000 is passing under the track head. Therefore, data is always written (or read) on the track address following the one specified. To provide an optimum transfer rate, the track addresses are not sequential. Instead, they are 0000, 1000, 2000, 3000, 0001, 1001, etc., as shown in the format diagram.

#### 3.2 NRZI RECORDING

The technique of recording on the magnetic disk surface is called NRZI (non-return to zero inhibit) recording. In this method, a reversal of the direction of magnetic flux represents a 1 bit and a lack of change represents a 0 bit. Writing is achieved by using a flip-flop to control the direction of magnetizing current on the track. The flip-flop is called the write flip-flop (WFF). By applying the 1's output of the DMB to the complement input of the WFF, the WFF is complemented as each 1 bit is shifted out of the DMB (Figure 3-1). The WFF causes the writer to reverse the flux direction on the disk surface each time the WFF is complemented. After all 12 bits are recorded on the disk surface, the writer records the 13th bit which is the parity bit. Since parity is even, resetting the WFF writes the parity bit. For example, if an odd number of 1's were recorded for the 12 bit word, then the WFF is in the set state; therefore, resetting the WFF reverses the flux on the disk to record a 1 parity bit. If the recorded character contains an even number of 1's, then resetting the WFF does not change its state. Therefore, a 0 parity bit is written.

When data is read from the track, the read head senses the flux changes of the disk to produce bipolar pulses. The pulses are rectified and shaped to produce data pulses. A pulse is defined as a 1 bit and no pulse is a 0 bit.

#### 3.3 GENERAL OPERATION OF SEARCH, READ, AND WRITE

Before explaining the detailed logic of the disk, this paragraph will describe the general operation of read and write (Figure 3-2). To write on the disk file, the DMA (disk memory address) register is loaded with the track address, and the EMA (extended memory address) register is loaded with the track address, and the EMA (extended memory address) register is loaded with the track and unit number. This is accomplished by the DEAL and the DMAW instructions. The DMAW instruction, which specifies the write mode, also initiates operation, enables the writer for the write mode, and generates a break request so that the first data word to be written is loaded into the DMB (disk memory buffer).

A search process then begins, whereby the track addresses are examined to determine when the track address passing under the write head is the correct word. This is accomplished by decoding the track-address pulses which come from the disk in serial fashion. The decoded track address bits are applied to a serial comparator. At the same time, the DMA is shifted end-around (recirculated). The DMA bits are also applied to the serial comparator so that the track address is compared to the address

3-2

Figure 3-1 Simplified Diagram of NRZI Recording

in the DMA. When the two addresses compare identically for the 11 bits shifted through the comparator, a signal is generated to enable the write operation. The DMB is shifted, and as the bits are shifted out of the DMB, they are applied to the write flip-flop (WFF). For each 1 bit shifted, the WFF is complemented, and for each 0 bit shifted, the WFF flip-flop remains in the same state. The output of the WFF flip-flop is applied to the write the indicated bits in NRZI format.

After the word is written, the DMA must be incremented to address the next word, and a break request generated to fetch the next word from memory. Incrementing the DMA is accomplished on the next recirculation of the DMA. As the DMA is shifted end-around, it passes through a serial adder circuit so that it can be incremented. If, at this time, the DMA increments from 3777 to 0000 (meaning a change to the next track), a carry pulse is propagated. This pulse increments the EMA register so that the next track (and, if indicated, the next unit) will be addressed. Writing therefore commences on the next sequential track at address 0000, following one revolution of the disk.

The read operation is similar to the write operation in that the DMA and EMA are loaded to specify the track address, track number, and unit number. The search operation is initiated to find the addressed track word. When the addressed track word is found, the track data is read serially into the data buffer, and a break request is generated so that the data in the data buffer can be transferred to the computer memory. The operation thereafter is similar to the write mode except for the data transfer direction.

Figure 3–2 Simplified Diagram of Read and Write

#### 3.4 TIMING PULSES

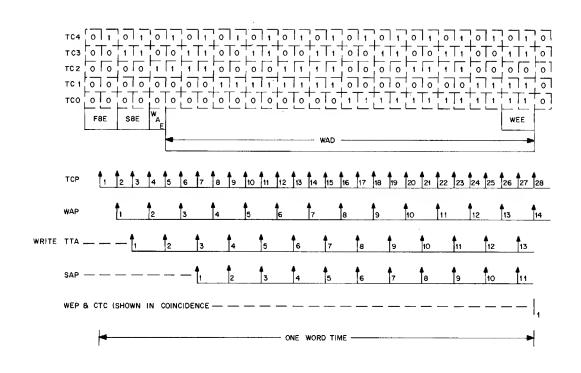

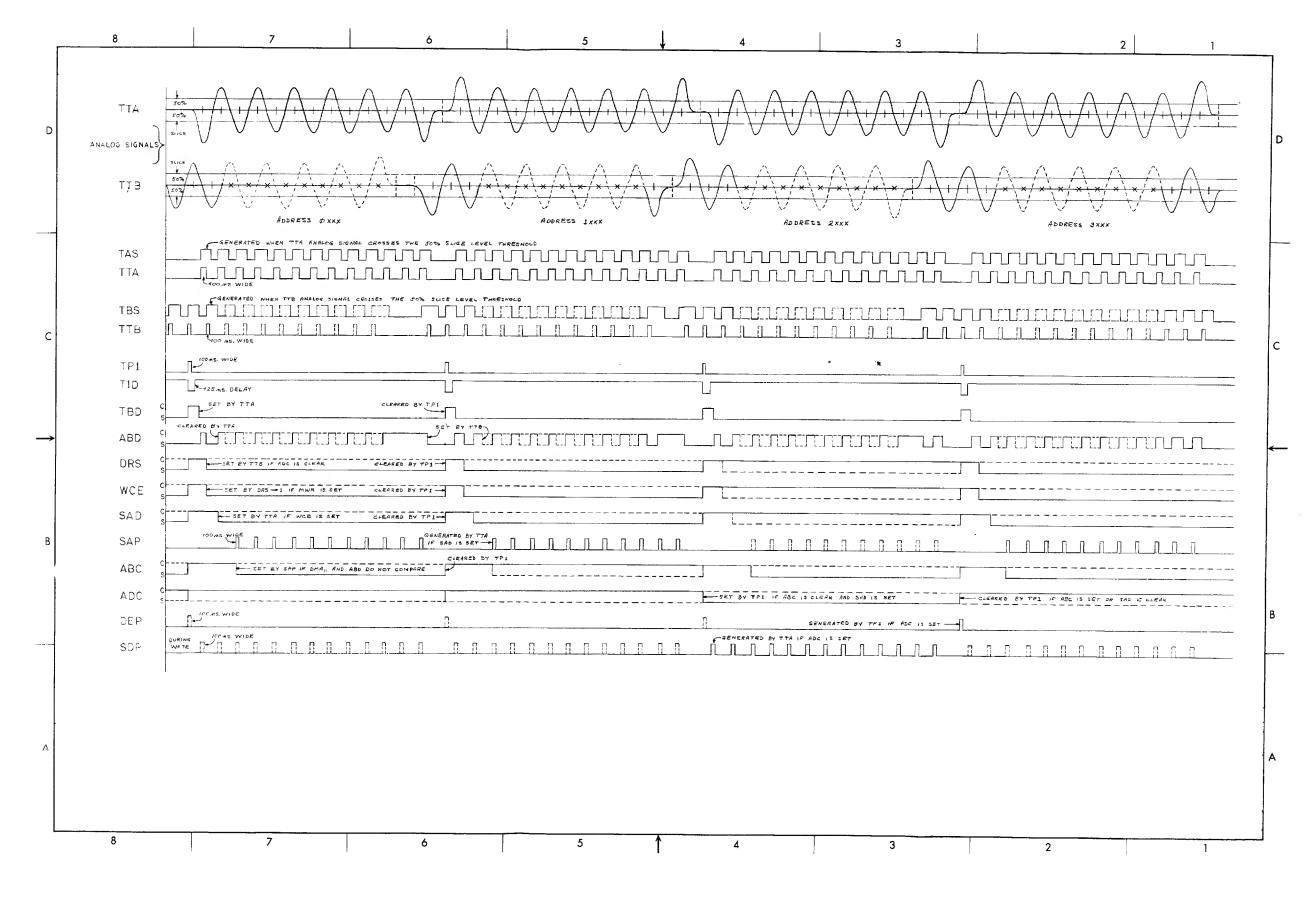

There are two timing tracks on the disk that provide timing pulses to control operation of the disk. They are the TTA and TTB analog signals which are 90° apart (refer to Dwg. No. D-TD-DF32-0-10 and Dwg. No. D-BS-DF32-0-1). The TTB signals contain the track address information. Both the TTA and TTB analog signals are applied to a SLICE RECTIFIER which provides rectified and clipped signals (TAS for TTA and TBS). The clipped signals are provided when the analog signal crosses the 50% slice level threshold. The pulse width of the TAS and TBS are reduced by PA to 400 ns and 100 ns, respectively.

The TTB pulses define the current track address; therefore, the occurrence of TTB pulses fluctuates with the current track address. Note that there are 13 TTA pulses separated by an interval of no TTA pulse. There are always three TTB pulses that are used for control functions for every track address period. The TTA and TTB pulses are combined to produce a TP1 pulse\* every track word address period. The TP1 pulse defines the beginning of a word address period. The TP1 pulse is produced by a TTB pulse when the ABD (address-bit decoder) flip-flop is set. The ABD flip-flop serves a dual purpose; it decodes the address bits during a track address search operation, and it is used in the production of TP1. The TTB pulse sets the ABD flip-flop and TTA resets it. Note on the timing diagram that the first two of the three TTB pulses that always occur do so during the period of no TTA pulse. Therefore, the first TTB pulse sets ABD and since ABD remains set when the second TTB pulse occurs, the second TTB pulse produces a TP1 pulse. The TTA, TTB, and TP1 pulses are used to control the operation of the disk file as explained in subsequent paragraphs.

## 3.5 DETAILED LOGIC DISCUSSION

This section provides a complete logic discussion of the operation of the disk file. As a supplement to this discussion, the reader is referred to Table 2–4 which provides an analysis of each IOT instruction, and Table 3–1 which provides a mnemonic list.

| Mnemonic | Name and Description                                                                                |

|----------|-----------------------------------------------------------------------------------------------------|

| ABC      | Address Bit Compare: This flip-flop is set when BCE is positive (comparison untrue or not matched). |

| ABD      | Address Bit Detector: This flip-flop is set when a one is read from the address track (TTB).        |

| ACE      | Address Confirmed Enable: If this level is positive at TP1 time, it indicates address found.        |

Table 3–1 Mnemonic Codes for DF32 Disk System

\* This is a signal used in the peripheral control logic and should not be confused with "TP1" in the PDP-8/I processor logic.

| Mnemonic | Name and Description                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| ACH      | Address Compare Hold: Cleared, it enables an end around shift in DMA register.<br>Set, it enables address increment while shifting. |

| ADC      | Address Confirmed: Set to indicate address search completed.                                                                        |

| BCE      | Bit Compare Enable: Positive when ABD and MA11 do not compare.                                                                      |

| СМВ      | Clear Memory Buffer                                                                                                                 |

| DBR      | Data Break Request: Signals computer when disk is ready to transfer data.                                                           |

| DEP      | Data End Pulse: After word time in which data was transferred between DMB and disk;<br>in or out. Also on disk overflow.            |

| DMA      | Disk Memory Address: Disk memory address register.                                                                                  |

| DMB      | Disk Memory Buffer: Disk memory buffer register.                                                                                    |

| DOP      | Data Ones Pulse: Each pulse indicates a one read from the disk data tracks.                                                         |

| DRL      | Data Request Late: This error flag indicates a timing problem between disk and computer.                                            |

| DRS      | Data Request Synchronizer: Effectively inhibits SAD while data is being transferred<br>(DMB–DISK).                                  |

| DSL      | Data Sense Lines: Connection between reader G083, writer G284, and heads on disk deck.                                              |

| DSP      | Data Strobe Pulse: Qualifies slicing rectifier at peak of data signal from readers.                                                 |

| DTC      | Disk Timer Clear: Generated by SCL or when switching disks. Clears TCA, TCB and MWR.                                                |

| EA       | Extended Address: Computer data field.                                                                                              |

| EMA      | Extended Memory Address: Disk extended memory address register (track and disk selectors).                                          |

| GRD      | Ground for write current.                                                                                                           |

| LAD      | Load Address: Loads DMA from BAC.                                                                                                   |

| LMB      | Load Memory Buffer: Loads DMB from BMB.                                                                                             |

| MAD      | Memory Address Deposit: Special case, used only when DMA register overflows from 3777 to 0000.                                      |

| MBC      | Memory Buffer Clear: Decoder output goes positive indicating when to write parity.                                                  |

| MBE      | Memory Buffer Enable: Qualifies WFF when a 1 is to be written on disk.                                                              |

| MBI      | Memory Buffer In: Data from disk to DMB comes in through this flip-flop.                                                            |

# Table 3–1 (Cont) Mnemonic Codes for DF32 Disk System

| Mnemonic   | Name and Description                                                                                                          |

|------------|-------------------------------------------------------------------------------------------------------------------------------|

| MRS        | Memory Request Sync: Controls input to TCA                                                                                    |

| MWR        | Memory Word Request: Set during all disk read or write operations (set by TCB overflow).                                      |

| NED        | Nonexistent Disk: Indicates disk overflow, raises interrupt, and sets TRC flip-flop.                                          |

| NEX        | Nonexistent: This level positive indicates unit selection does not exist.<br>(No unit).                                       |

| PAR        | Parity: This flip-flop reads parity from disk.                                                                                |

| PCL        | Power Clear: From PDP-8 computer. (Initialize in PDP-8/I)                                                                     |

| РСА        | Photo Cell Amplifier: Located on disk–deck. Amplifies and sets width of photo sync mark.                                      |

| PER        | Parity Error: This flip-flop is set when an odd number of bits is read in one word.                                           |

| PSM        | Photo Sync Mark: Output of PCA used to synchronize disk operation.                                                            |

| RDE        | Read Enable: Stabilizes timing logic.                                                                                         |

| R∕W        | Read/Write: Transfer direction = write when set; read when cleared.                                                           |

| SAD        | Search Address: This flip-flop is set each word time by the second TTA pulse (except when ADC = 1).                           |

| SAP        | Shift Address Pulse: These pulses are generated by the second through thirteenth TTA pulses (except when $ADC = 1$ ).         |

| SCL        | Start Clear: Is generated by PCL or IOT 6601.                                                                                 |

| SDP        | Shift Data Pulse: Generated by TTA during both read and write when ADC = 1<br>(Burst of 13).                                  |

| SEL        | Select: True when unit select and PSM are true.                                                                               |

| SHE        | Shift Enable: Is time when ADC = 1 and $R/W$ is = 0 (read).                                                                   |

| SLT        | Select: True when unit select is true.                                                                                        |

| TCA<br>TCB | Time Counter "A": Used together to allow a four word time delay when switching from control unit to expander.                 |

| TRC        | Transfer Complete: This flip-flop is set when WCO is true; or when NED is set and WCO = 0.                                    |

| TTA        | Timing Track "A": A burst of 13 pulses and a one pulse time space recorded on the disk (timing).                              |

| ттв        | Timing Track "B": Address information recorded on the disk (11 bits absolute address,<br>3 bits to generate TP1 and set DRS). |

| WCE        | Word Count Enable: Effectively combines MWR=1 and DRS=1 to qualify gating on SAD flip-flop.                                   |

# Table 3–1 (Cont) Mnemonic Codes for DF32 Disk System

| Mnemonic | Name and Description                                                                   |

|----------|----------------------------------------------------------------------------------------|

| wco      | Word Count Overflow                                                                    |

| WCP      | Word Count Pulse: Writes parity if WFF=1 after 12-bit data word has been written.      |

| WFF      | Write Flip–Flop: Is complimented by SDP if MBE is true (to write a one in NRZ method). |

| WIA      | Write Inhibit "A": Write lockout tracks 0 through 7.                                   |

| WIB      | Write Inhibit "B": Write lockout tracks 10 through 17.                                 |

| WTE      | Write Enable: True when ADC = 1 and R/W = 1 (write) (starts current flowing in head).  |

Table 3-1 (Cont) Mnemonic Codes for DF32 Disk System

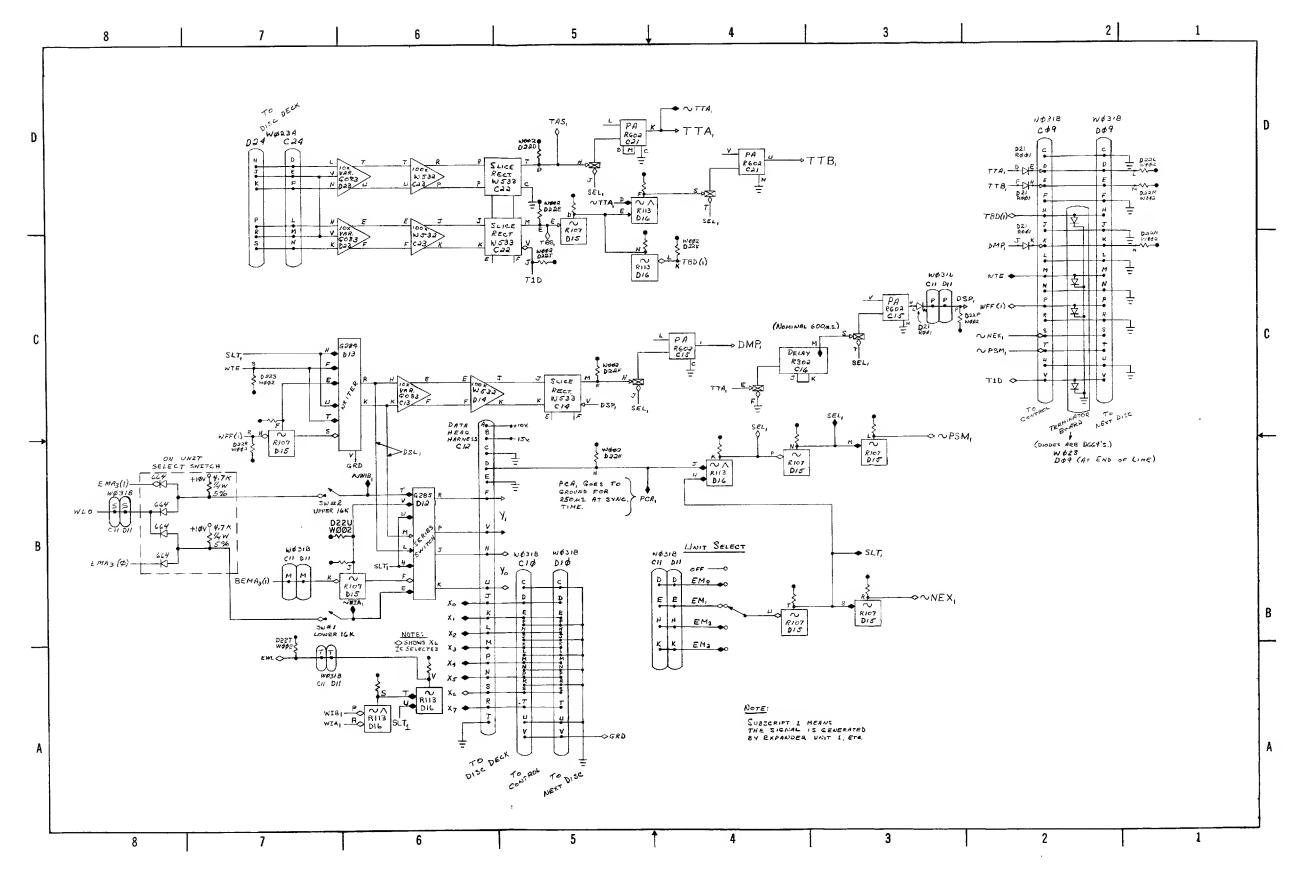

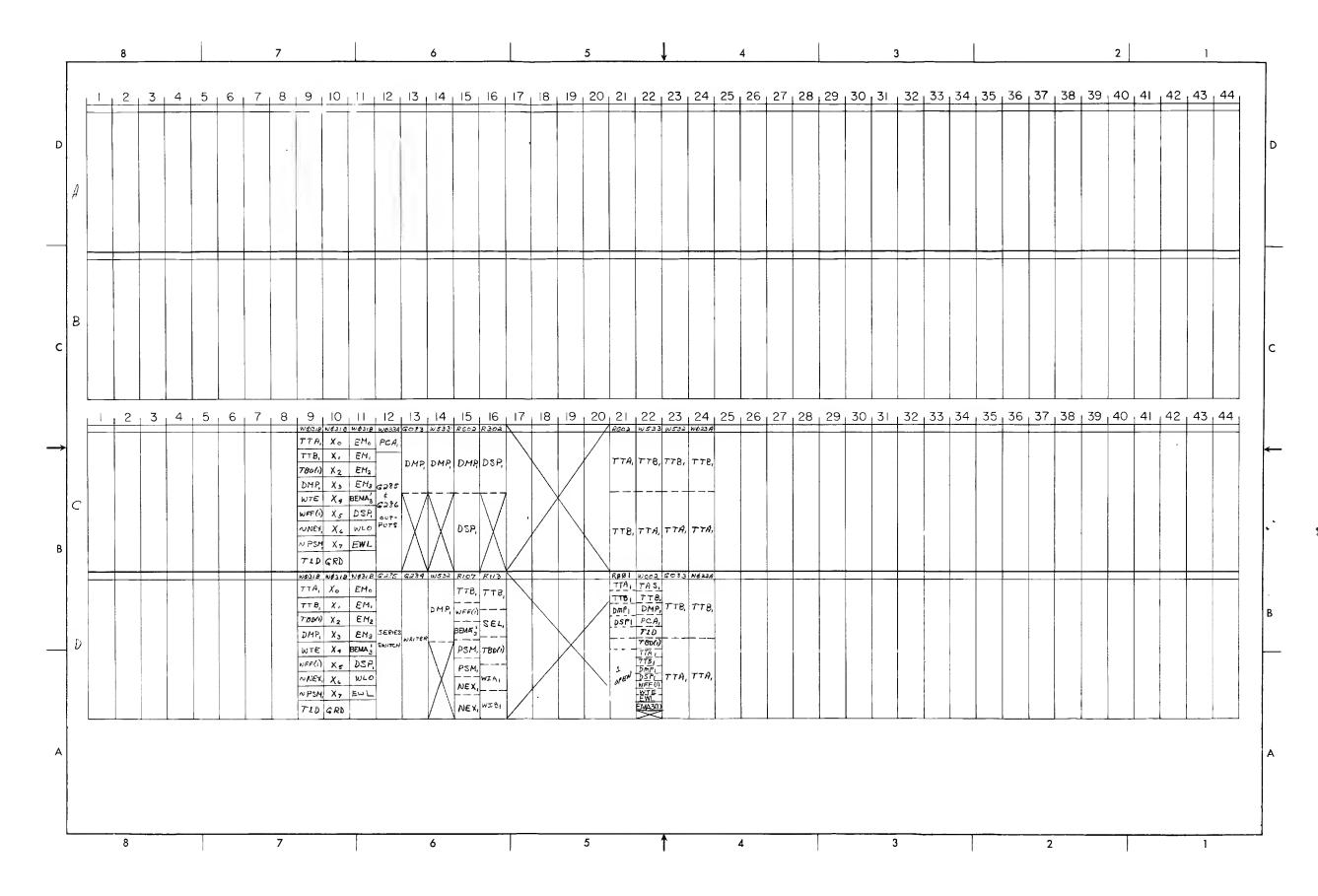

## 3.5.1 Address Searching

The read or write operation is initiated upon the occurrence of the DEAL and the DMAW for writing, or DMAR for reading. The DEAL IOT instruction is decoded by the device selector (Dwg No. DF32-0-1) to produce the IOT 611 and 614 pulses. The IOT 611 (ECL) pulse clears the EMA and EA registers (Dwg. No. DF32-0-3), and the IOT 614 pulse loads these registers from the PDP-8 AC. The EMA<sub>4</sub> and EMA<sub>5</sub> bits are decoded to provide the unit number selected by the program. If the UNIT SELECT SWITCH for the DF32 disk file is set to this number, signal SLT becomes 1. (Similarly, if any one of the DS32 disk expander selection switches are set to this number, it is energized.) Signal SEL then becomes 1 (except during the 200-µs gap period) to enable the disk timing cirucits.

Assuming that there is a read operation, the DMAR instruction is issued to start the operation. DMAR generates IOT 601 (SCL) and IOT 602 which perform the functions outlined in Table 2-4. As shown, DMAR loads the DMA with the disk track address and sets the MRS (memory request sync) flipflop to initiate the search operation.

Four TP1 timing pulses are necessary before the transition of flip-flop TCB (as it is set) sets the MWR (memory request) flip-flop. (A complete timing diagram is shown in Dwg. No. D-TD-DF32-0-10 in Chapter 6.)

With MWR set, the immediate sequence of events are as follows.

- a. TTB sets DRS (data request sync).

- b. The transition of DRS sets WCE (word count enable).

- c. WCE enables the next TTA pulse to set SAD (search address).

With SAD set, the circuits are ready to start shifting the DMA so that the address in the DMA can be compared to the disk track address. SAD enables the TTA pulses to generate the shift address pulses (SAP) that shift the DMA (Dwg. No. DF32-0-2). Note that there are 11 TTA pulses that produce 11 SAP pulses so that the 11 track address bits of the DMA can recirculate. Between each SAP interval the TTB pulses (which specify the track address) may or may not occur; i.e., for each bit position where the track address specifies a 1 there is a TTB pulse; for each track address bit position that is 0, there is no TTB pulse. The occurrence of a TTB pulse sets the ABD (address bit detector) flip-flop and TTA resets the flip-flop. Therefore, the ABD signal (if a 1 is specified) is present during the interval of a TTA pulse. As the low-order bits from the DMA are shifted out of DMA11 they are compared to the ABD signal; the exclusive-OR circuit (output BCE) performs this comparison. If during the interval of recirculating the DMA through the comparator there is 1 bit that does not compare to ABD, signal BCE goes to ground potential for that comparison and allows the SAP pulse to set the ABC flip-flop. Thus, if ABC (address bit compare) is set after the 11 shifts of the DMA, the DMA address does not compare to the track address. In this case, the circuits again will set up as previously described to repeat the comparison; i.e., TTB sets DRS, and so forth.

When the DMA and disk track address compare identically for the 11 shifts, the ABC flipflop will remain reset since there were no non-bit comparisons to allow a SAP to set ABC. Therefore, at the end of this interval, the TP1 pulse sets ADC (address confirmed). Signal ADC then enables the read or write operation as described in ensuing paragraphs. The data transfer either to or from the disk occurs on the next TP1 interval. During this interval, signal ADC prevents the DRS flip-flop from being set so that address comparison does not occur at the same time as the data transfer (refer to Figure 3-3).

After the comparison of the DMA to the track address and the data transfer, the DMA must be incremented to address the next sequential track address. To accomplish this, a 1 is added to the DMA by a serial adder on its next recirculation. The addition is described as follows. With ADC set, the next TP1 pulse generates the DEP (data end) pulse which sets ACH (address compare hold) assuming that there is no word count overflow. Note that the DEP pulse also sets the DBR (data break) flip-flop to initiate a data break cycle. The same TP1 pulse that generates DEP also resets ADC. With ADC reset, the next TTB pulse can set DRS to initiate the search address operation. With ACH set, the first bit shifted out of DMA11 is incremented by 1: ACH(1) and DMA11(1) are ANDed so that if DMA11(1) is 1, a 0 is shifted into DMA1 (since 1 + 1 = 0 with a 1 to carry). The carry is implemented by maintaining ACH in the 1 state until DMA11 shifts out a 0; at this time the SAP resets ACH and allows normal search address operation thereafter.

A special case arises when the DMA increments from 3777 to 0000. Throughout this shift interval the ACH remains set to propagate the carry and it remains set after this interval. On the next shift interval the 0000 is shifted and ACH being set would specify a 1 to be added to the low order. To prevent this, the MAD flip-flop (which is set by resetting of SAD when ACH was 1) inhibits a 1 from being shifted into DMA1 on the first shift. Since a 0 is shifted out of DMA11 on the first shift, ACH is reset to permit normal operation thereafter.

3-9

Figure 3-3 Timing Diagram

#### 3.5.2 Read

The DMAR instruction initiates address searching as previously described; it also clears the R/W (read/write) flip-flop to specify a read operation and clears the WCO (word-count overflow) flip-flop.

When the DMA and track address compare, the ADC flip-flop is set and signal SHE goes to 0V and enables the DSP (delayed TTA pulse) pulses to generate SDP (shift data pulses) pulses (Dwg. No. DF32-0-4). The DSP pulses shift the DMB as data is read from the disk track. According to NRZI recording methods, a 1 read from the track is represented by a pulse which is the result of a phase reversal on the magnetic surface, a 0 is the result of no phase reversal and therefore no pulse is generated. The output from the read head that senses the magnetic information on the disk track is sensed by the slice rectifier. The slice rectifier transforms the bipolar signal read from the track into a pulse output. The output of the slice rectifier is enabled by SEL and SHE to produce DOP (data ONEs pulses). The DOP pulse sets the MBI flip-flop. If a 1 is read from the track, MBI is set and the SDP pulse shifts a 1 into DMB<sub>0</sub>. If a 0 is read from the track, MBI remains reset and a 0 is shifted into DMB<sub>0</sub>. Thus, the 13 DSP pulses shift the words read from the disk track into the DMB. The thirteenth SDP shifts the last bit of data from MBI into DMB<sub>0</sub> and parity ends up in MBI.

After the complete word has been read, parity is checked (parity is checked only in the read mode). As the data bits are read from the track, each DOP pulse complements the PAR (parity) flip-flop. Since parity is even, the PAR flip-flop should be in the reset state after a complete word is read; if not, the DEP pulse sets the PER (parity error) flip-flop to signify a parity error.

The read operation continues in this manner until all words specified by the WC (word count) register have been written. When this occurs, the WCO (word count overflow) flip-flop is set and inhibits the DEP pulse from setting the DBR flip-flop. Thus no further data break occurs. The DEP pulse is enabled WCO(1) to set the TRC (transfer complete) flip-flop... The TRC signal then generates an interrupt to notify the program that the data transfer is complete.

## 3.5.3 Write

The DMAW instructions initiate the write mode by starting the address search operation as previously described; it also sets the R/W flip-flop to signify the write mode to the data break facility in the PDP-8 computer. The DMAW instruction also sets the DBR flip-flop to generate a break request to load the DMB with the first word to be written. The PDP-8 data break facility responds by generating (B)BREAK which is enabled by R/W to load the DMB. The address accepted pulse resets DBR.

When an address comparison is found, signal ADC(1) enabled by R/W(1) causes signal WTE to go to 0V, and TTA generates SDP pulses. Signal WTE is applied to the writer to enable writing on the selected disk track. The SDP pulses shift the DMB register. As the DMB11 bit is shifted out of the DMB register, it is applied to the WFF (write flip-flop). If DMA11 is a 1, and the level MBC (complemented) is present, the SDP pulse complements WFF which in turn causes the write head to reverse the flux direction on the magnetic surface on the disk. If DMB11 is a 0, the WFF does not change and no flux reversal occurs. Thus 12 bits are written on the selected disk track. After the 12 data bits are written, the parity bit must be written. This is accomplished as follows.

The LMB (load memory buffer) pulse that loads the DMB also generates the DOP pulse which sets the MBI flip-flop. Therefore, on the first shift of the DMB (when the first bit is recorded on the disk), a 1 is shifted into DMBO. Zeroes are shifted thereafter into the DMB as the data bits are recorded. After 12 shifts, the 1 that was inserted into DMBO by MBI is now in DMB11 with the rest of the DMB (DMB through DMB10) containing 0s. The DMBO through DMB10 condition is sensed for all 0s, and when 0, the signal MBC becomes true. This inhibits the DMB11 pulse from complementing WFF. Signal MBC enables the last shift pulse to reset WFF which writes the even parity bit.

The write operation continues in this manner until all words specified by the WC register have been written. When this occurs, the WCO (word count overflow) flip-flop is set and inhibits the DEP pulse from setting the DBR flip-flop. Thus no further data break cycles occur. The DEP pulse is enabled by WCO(1) to set the TRC flip-flop which generates a skip condition or interrupt to notify the program that the write operation is completed.

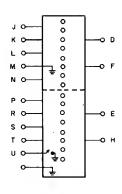

## 3.5.4 Track Head Selection

For both the read and write operations, the track head selection is accomplished by bits EMA3, EMA2, EMA1, and DMA0. The DMA0, EMA1, and EMA2 bits are applied to an octal decoder as shown in Dwg. No. DF32-0-5. Each octal decoder output is applied to a pair of heads. Bit EMA3 and its complement are also applied to the heads to complete the selection. For example, if the track selection bits contain 0000, then the low-order bits (EMA2, EMA1, and DMA0) are decoded to select heads 0 and 10; however, since EMA3 is 0, only head 0 is selected for the data transfer.

For the write mode, the write lock switches permit either the upper 16K addresses or the lower 16K addresses to be protected from being written upon. The WRITE LOCK SELECTOR switch permits any or all disk files to be selected for write lock protection. The EMO-EM3 signals (when selected by WRITE LOCK SELECTOR) are OR gated and ANDed with the R/W(1) signal to generate signal WLO (write lockout). WLO is then applied to the WRITE LOCK switches ANDed with EMA3 to provide the write lock protection on either the upper or lower 16K of the selected disk file.

#### 3.5.5 Continuous Data Transfers

When the data transfer address for a particular track reaches 3777, then the next data transfer will occur at address 0000 of the next sequential track. This is accomplished as follows. When the DMA reaches 3777, the recirculation of the DMA through the serial adder causes 0000 to be shifted into the DMA. During this recirculation interval, the ACH flip-flop is set and remains set after this interval and, as SAD is reset, its transition SAD(0) provides a pulse to DMA0. This pulse is enabled by ACH(1) to increment the DMA0 and EMA register so that the next sequential track is addressed. Similarly, when all tracks have been accessed for a particular disk file, the overflow of EMA3 will increment EMA4 (and possibly EMA5) so that the next sequential disk file will be addressed.

#### 3.5.6 Disk Expander Operation

The EMA4 and EMA5 bits select one of four disk files for data transfers – either the DF32 or one of three DS32 Disk Expanders. The EMA4 and EMA5 bits are decoded as shown on Dwg. No. DF32– 0-3 to produce EM0, EM1, EM2, and EM3. These bits (EM0–EM4) are applied to each of the disk files in the system. If the UNIT SELECT switch is set to the same decoded selection (i.e., EM0–EM4), then that unit is selected for data transfer. For example, if EM1 is selected by the program and a disk file (refer to Dwg. No. DS32–0–1) UNIT SELECT switch is set to EM1, then that disk file is selected for operation. The TTA and TTB pulses from that unit are sent to DF32 control (Dwg. No. DF32–0–1) to control operation. Data transfer operations are then similar to that previously described. The DSP (data shift pulse) is sent to DF32 control to shift the DMB. In a read operation, the DMP1 pulses from the disk expander are coupled back to DF32 control (via D15-K) to produce the DOP pulses that provide the read data for the DMB. In the write mode, the WFF output from the DF32 control is coupled to the disk expander writer to provide the same function as previously described.

When the EMA register overflows to address the next unit or disk expander, ACH(1) enables EMA3(0) to reset MWR (Dwg. No. DF32-0-1). ACH(1) also enables EMA3(0) to set MRS so that the control circuits have time to synchronize to a different set of TTA and TTB pulses.

## 3.5.7 Errors

There are three errors that may be sensed by the IOT 6621 instruction. They are parity error, data request late (DRL), or write lock switch flag. The parity error may occur during the read operation as previously described. The DRL error is the result of a data break request, whereby no word transfer occurred before the next DEP (data end pulse). This means that a data transfer occurred between DMB and the disk track before the previous transfer was handled by the data break facility or ADDRESS ACCEPTED pulse was never received from computer. In this case, the DRL flip-flop (Dwg. No. DF32-0-3) is set to signify the error. The write lock switch flags are WIA, WIB, and EWL. WIA signifies that a write is attempted on the lower 16K of the DF32 when the lower 16K address is locked out by the write lock selection switches. Similarly, WIB signifies the same for the lower 16K. The EWL flag is the combination of the WIA and WIB flags from all disk expanders.

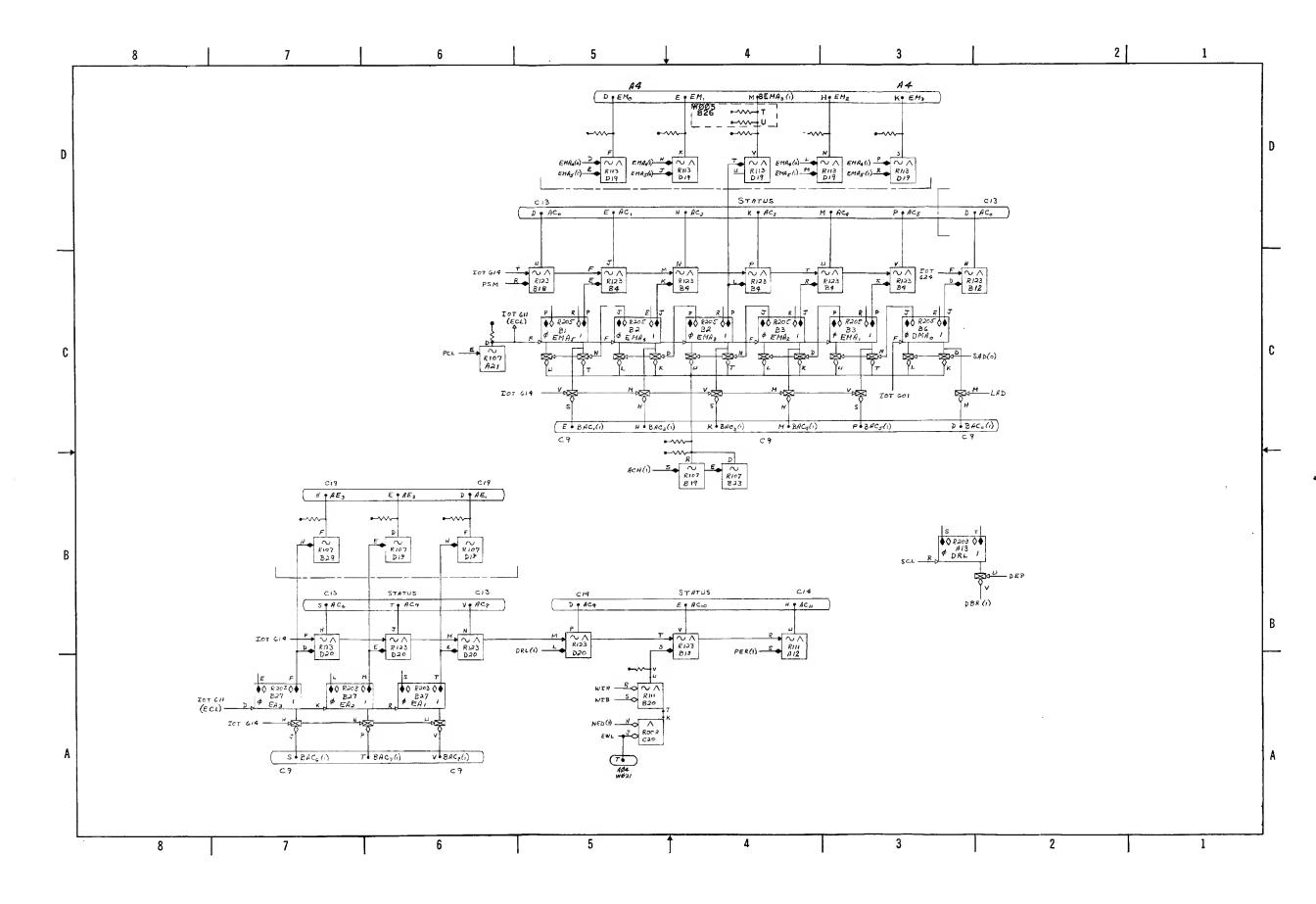

# 3.5.8 Timing Track Writer

The time track writer writes both the timing track and address track on the disk of the DF32 system. The recording is accomplished in NRZI format. That is, a recorded 1 changes the direction of magnetization and a 0 is the absence of the magnetization change. Table 3–2 provides a mnemonic list of the signals on the block schematics of the timing track writer.

Operation of the timing track writer starts when the PCA (photo cell amplifier) output goes negative to signify the end of photo sync pulse (Dwg. No. D-BS-TW32-0-1). This provides a PSB (photo sync beginning) and a PSE (photo sync end) pulse. The PSE pulse clears the track counter TCO-TC4. The PSB pulse triggers the WED (write enable delay) multivibrator which is adjusted to provide the guard band for photo sync mark. PSB also triggers the CED (clock enable delay) one-shot multivibrator (Dwg. No. D-BS-TW32-0-1 (Sheet 2)).

After WEB times out, it sets the WEB (write enable) flip-flop if the WRITE 2 switch is depressed. The WEB signal then enables the G284 writers to write the specified data on the timing and address tracks. WEB(1) also enables the CED signal (Dwg. No. D-BS-TW32-0-1 (Sheet 2)) to set the TCE (time clock enable) flip-flop which enables the R401 clock module to produce clock pulses (TCP).

# Table 3–2 Mnemonic Codes for DF32 DECdisk Timing Track Writer

| Mnemonic | Name and Description                                                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| ACH      | Address Compare Hold: when clear allows end around shift in MA register. When set allows increment of address.                             |

| AMA      | Add Memory Address: this level being negative allows 1s to<br>be written in the 11-bit absolute address, and 1s to be shifted<br>into MA1. |

| CED      | Clock Enable Delay: adjusted to establish guard band for photo sync mark .                                                                 |

| СТС      | Clear Time Counter: comes once per word to zero time count register and WAD flip-flop.                                                     |

| FBE      | First Bit Enable: positive to enable first TTB bit to be written.                                                                          |

| PCA      | Photo Cell Amplifier: negative level except at photo sync time.                                                                            |

| PSB      | Photo Sync Begin: pulse in response to leading edge of photo<br>sync mark .                                                                |

| PSE      | Photo Sync End: pulse in response to trailing edge of photo sync mark .                                                                    |

| SAP      | Shift Address Pulse: a burst of 11 pulses used to shift MA register.                                                                       |

| SBE      | Second Bit Enable: positive to enable second TTB bit to be written.                                                                        |

| TCE      | Time Clock Enable: set to enable clock.                                                                                                    |

| ТСР      | Time Count Pulse: clock output.                                                                                                            |

| TEP      | Time Enable Pulse: initializes the timing track writer.                                                                                    |

| WAD      | Write Address: This flip-flop is set during the time that the 11-bit absolute address is written.                                          |

| WAE      | Write Address Enable: this level is positive to allow WAD to be set.                                                                       |

| WAP      | Write Address Pulse: 14 per word to complement WFB.                                                                                        |

| WEB      | Write Enable: qualifies writers when true.                                                                                                 |

| WED      | Write Enable Delay: adjusted to establish guard band for photo<br>sync mark .                                                              |

| WEE      | Word End Enable: positive during last TTA and TTB bit times.                                                                               |

| WEP      | Word End Pulse: comes once per word at the end of the word.                                                                                |

| WFA      | Write Flip-Flop "A": is complemented to write TTA bits on disk (timing).                                                                   |

| WFB      | Write Flip-Flop "B": is complemented to write TTB bits on disk (address).                                                                  |

The TCP pulses now start to toggle the TCO-TC4 counter. This counter is used to establish time relations between the TTA and TTB pulses that are to be recorded. Since there is a pulse difference between the TTA and TTB pulses, alternate counts of the TCO-TC4 counter establish the basic TTA and TTB pulse rates.