# **IDENTIFICATION**

Product Code: MAINDEC 08-D1DA-D

Product Name: Extended Memory Checkerboard - Part 2

Date Created: September 8, 1965

Maintainer: Diagnostic Group

Previous Code: MAINDEC 820-2

### 1. ABSTRACT

MAINDEC 08-D1DA-D is a preliminary test for core memory failures on half-selected lines under worst-case conditions of reading and writing. It is used to test memory module X while running the program in memory module Y. This is applicable for test of Type 184 Memory Modules and MM08 Memory Modules.

MAINDEC 08-D1CA-D will also test the control portion of the Extended Memory Type 138 or Extended Memory Type 185.

## 2. REQUIREMENTS

#### Storage

The program occupies registers  $0000_8 - 0111_8$  and tests memory from  $0000_8 - 7776_8$ .

The RIM Loader must be in registers 77568 - 77768.

#### Subprograms and/or Subroutines

High RIM Loader, Binary Loader Digital-8-2-U-RIM

### Equipment

Standard PDP-8 and Extended Memory Module Type 183.

#### USAGE

## 3.1 Loading

If the Binary Loader is in memory, go to the Extended Memory Checkerboard Test. Otherwise, the RIM Loader and/or the Binary Loader must be loaded into memory.

The Extended Memory Checkerboard Test may now be loaded as follows:

Set 7777<sub>8</sub> in the SWITCH REGISTER Press LOAD ADDRESS key Place object tape in the ASR 33 Press START key on the operator console Engage reader

## 3.2 Switch Settings

Starting address:  $0000_8$  DF(X), IF(X).

Program Control Settings - One of four possible patterns that can be written is obtainable by each of the following SR settings.

| 0100  | this setting is used tor the standard PDP-8 unit.          |

|-------|------------------------------------------------------------|

| 00008 | These are used for special core units from other supplies. |

| 0001  | (Reference section 5.2.)                                   |

| 0101  | This setting is used for Type 185, 186 or MM08 Memories    |

|       | of the PDP-8.                                              |

# 3.3 Start up and/or Entry

With the program in the desired memory field set the following:

- a. Load address 0000<sub>8</sub>. Load the data field and instruction field of the memory containing the object program.

- b. Set the instruction CDF (62N1) to the field to be tested in the SWITCH REGISTER.

- c. Press DEPOSIT.

- d. Repeat step a.

- e. Reference Program Control Settings (section 3.2).

- f. Press START.

## 3.4 Errors in Usage

The contents of a given memory cell should be either 7777 or 0000. An error occurs if a 1 becomes a 0, or vice versa. The following pair of stops occurs for each error:

| C(MA) | Error | Cause of Error                                                                    |

|-------|-------|-----------------------------------------------------------------------------------|

| 0071  | ΕĪ    | Memory cell does not contain 7777 or 0000. AC displays contents of cell in error. |

| 0074  | EIA   | AC contains address of cell causing previous error stop.                          |

# 3.5 Recovery from Such Errors

| Error | Recovery Procedure                                       |

|-------|----------------------------------------------------------|

| El    | Record the C(AC). Press CONTINUE to reach the next halt. |

| E1A   | Record the C(AC). Press CONTINUE to resume testing.      |

#### 4. <u>RESTRICTIONS</u>

This program is only a preliminary test and should only be used to simplify memory adjustments and maintenance procedures.

Maindec 802\* should be loaded into the memory module under test for a final test. (Reference Maindec 802\* for usage)

### 5. DESCRIPTION

### 5.1 Discussion

<sup>\*</sup> See Appendix

In a standard core plane, a given core is selected when the combined voltages of the x-and y-selection lines exceed the threshold voltage for reversing the polarity of the core. This occurs at the intersection of the activated selection lines. However, all other cores which are threaded onto the activated lines will be slightly disturbed. Under marginal voltage conditions, such half-selected cores may also reverse polarity if their states are properly established by the pattern which the Checkerboard Test writes into memory.

When a selected core is in the 1 state, the read current causes it to reverse polarity and become 0. When the core is in the 0 state, the write current causes it to become 1. Thus, the possibility of a reading error is greatest when all the half-selected cores are in the 1 state; a writing error is most probable when all the half-selected cores are in 0 state.

If a half-selected core changes polarity, the error is detected when the memory register containing that core is tested by the program. For a reading error, the contents of that core will appear as a 0 in a field of 1's, and vice versa for a writing error.

Every Checkerboard Test pattern consists of alternating pairs of memory cells, one pair containing 7777's, the other containing 0000's. Since many manufacturers wire their core stacks in different ways, the same pattern of alternations cannot be used for every type of core and still allow a worst-case condition; that is, one in which all half-selected cores undergo the greatest possible disturbance which can occur when testing memory. The following pattern is used for the Ferroxcube memories with which most PDP-8's are provided.

x-axis

$$0 0 1 1$$

$(MA_{0-5})$   $1 1 0 0$

$1 1 0 0$

$0 0 1 1$

$y$ -axis  $(MA_{6-11})$

Since the y-axis selection lines are conditioned by the low-order six bits of the memory address register (MA<sub>6-11</sub>), and the x-axis lines by the high-order bits (MA<sub>0-5</sub>), the above array is interpreted as follows: (x- and y-axes should be interpreted as shown above).

Positions on the x-axis represent consecutive locations in memory from 00-77.

Positions on the y-axis represent consecutive 1008's. Thus, the lower left corner represents location 0000. This position contains a 0, which means that the contents of the entire memory cell at address 0000 are 0's. Likewise, the contents of memory cell 0201 are 1's or 7777; this is determined by reading the third row up on the x-axis, and across one position on the y-axis.

The pattern in memory appears as follows:

| Address | Contents |

|---------|----------|

| 0000    | 0000     |

| 0001    | 0000     |

| 0002    | 7777     |

| 0003    | 7777     |

| 0004    | 0000     |

| 0005    | 0000     |

| 0006    | 7777     |

| 0007    | 0000     |

| • • • • |          |

thus:

It can be seen from the pattern matrix, that after 77<sub>8</sub> registers, the pattern reverses itself,

| Address | Contents |

|---------|----------|

| 0076    | 7777     |

| 0077    | 7777     |

| 0100    | 7777     |

| 0101    | 7777     |

| 0102    | 0000     |

| 0103    | 0000     |

| 0104    | 7777     |

| 0105    | 7777     |

| 0106    | 0000     |

| 0107    | 0000     |

|         |          |

And so on through memory. The pattern reverses every  $100_8$  registers.

# 5.2 Pattern Generation

The patterns generated by the other three switch register settings are defined by the following pattern matrices.

| SR Se |        | Patte      | ern Mat | rix |    |

|-------|--------|------------|---------|-----|----|

| 0000  | x-axis | <b>A</b> 1 | 1       | 0   | 0  |

|       |        | 1          | 1       | 0   | 0  |

|       |        | 0          | 0       | 1   | 1  |

|       |        | 0          | 0       | 1   | _1 |

|       |        | y-a        | ×is     |     |    |

| 0001  | x-axis | <b>♣</b> Ī | 0       | 0   | 1  |

|       |        | 1          | 0       | 0   | 1  |

|       |        | 0          | 1       | 1   | 0  |

|       |        | 0          | 1       | 1   | 0  |

|       |        | у-а        | xis     |     |    |

| 0021  | x-axis | <b>•</b> 0 | 1       | 1   | 0  |

|       |        | 1          | 0       | 0   | 1  |

|       |        | 1          | 0       | 0   | 1  |

|       |        | 0          | 1       | 1   | 0  |

|       |        | у-а        | xis     |     |    |

| SR Se | tting  |            | Patter | n Matr | ix  |

|-------|--------|------------|--------|--------|-----|

|       | x-axis | <b>†</b> 1 | 0      | 0      | 1   |

| 0101  |        | 0          | ī      | 1      | , 0 |

|       |        | 0          | 1      | 1      | 0   |

|       |        | 1          | 0      | 0      | 1   |

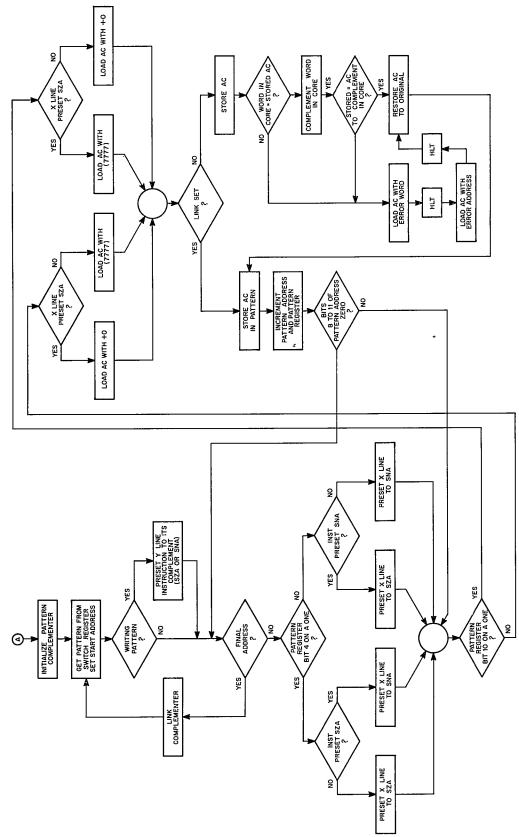

## 6. METHODS

## 6.1 <u>Discussion</u>

The program writes the pattern into the area of memory to be tested. It then tests each word as follows:

The contents of the word are checked for incorrect bits.

The contents are complemented, deposited in the same register, and retested for incorrect bits.

The original contents are returned to the register, and the next one is checked.

After all memory is tested, the program writes the complement of the pattern and proceeds to check as before. In this way, every core is tested for errors that might occur when it is read and when information is written into it.

# 7. <u>EXECUTION TIME</u>

2 seconds

## 8. PROGRAM LISTING

/MAINDEC 08-D1DA-D

/EXTENDED MEMORY CHECKERBOARD-PART 2

|        |      | *Ø   |     |      |      |             |     |         |

|--------|------|------|-----|------|------|-------------|-----|---------|

| ØØØØ   | ØØØØ |      | Ø   |      |      |             |     |         |

| ØØØ1   | 7121 |      | CLL | CML  | IAC  |             |     |         |

| ØØØ2   | 3107 |      |     | COM  | _,,, |             |     |         |

| ØØØ3   | 7604 | STX. | LAS |      |      |             |     |         |

| 0004   | 1111 |      | TAD | MUD  |      |             |     |         |

| 0005   | 3105 |      | DCA | PAT  |      |             |     |         |

| 0006   | 1111 |      | TAD | MUD  |      |             |     |         |

| ØØØ7   | 3106 |      | DCA | SA   |      |             |     |         |

|        |      |      |     |      |      |             |     |         |

| ØØ 1 Ø | 2107 | STB, | ISZ |      |      |             |     |         |

| ØØ 1 1 | 1107 |      | TAD | COM  |      |             |     |         |

| 0012   | Ø1Ø3 |      | AND | DO T |      | /2          |     |         |

| ØØ 1 3 | 764Ø |      |     | CLA  |      |             |     |         |

| 0014   | 1102 |      | TAD | NOT  |      | /1Ø         |     |         |

| 0015   | 1077 |      | TAD | HOT  |      |             |     |         |

| ØØ 1 6 | 3025 |      | DCA | Y    |      | /COMPLEMENT | THE | PATTERN |

| ØØ17<br>ØØ2Ø<br>ØØ21<br>ØØ22<br>ØØ23<br>ØØ24                                  | 1101<br>1106<br>7650<br>5003<br>1105<br>0100                                 | STC,        | TAD POT TAD SA SNA CLA JMP STX TAD PAT AND ROT                                 | /100<br>/TEST FOR FINAL ADDRESS<br>/200                       |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|

| 0025<br>0026<br>0027<br>0030<br>0031<br>0032                                  | 0000<br>1102<br>1077<br>3033<br>1105<br>0103                                 | Υ,          | Ø TAD NOT TAD HOT DCA X TAD PAT AND DOT                                        | /Y LINE PRESETS X LINE<br>/TO SNA OR SZA<br>/2                |

| ØØ33<br>ØØ34<br>ØØ35<br>ØØ36<br>ØØ37                                          | 0000<br>7040<br>7420<br>5047<br>3506                                         | Х,          | Ø<br>CMA<br>SNL<br>JMP CCK<br>DCA I SA                                         | STORE PATTERN AND RECOMPLEMENT                                |

| 00 40<br>00 41<br>00 42<br>00 43<br>00 4 4<br>00 45<br>00 46                  | 2106<br>2105<br>1106<br>0104<br>7650<br>5017<br>5031                         | STD,        | ISZ SA ISZ PAT TAD SA AND BOT SNA CLA JMP STC JMP X-2                          | /WORD WHEN CHECKING                                           |

| 00 47<br>00 50<br>00 51<br>00 52<br>00 53<br>00 54<br>00 55<br>00 56<br>00 57 | 3177<br>1506<br>7041<br>1177<br>7640<br>5070<br>1177<br>7040<br>3506<br>1506 | CCK,        | DCA WRD TAD I SA CMA IAC TAD WRD SZA CLA JMP CC3 TAD WRD CMA DCA I SA TAD I SA | /CHECK PATTERN  /ERROR IN CORE  /COMPLEMENT THE WORD /IN CORE |

| 0061<br>0062<br>0063<br>0064                                                  | 7001<br>1177<br>7640<br>5070                                                 |             | IAC IAC TAD WRD SZA CLA JMP CC3                                                | /TEST COMPLEMENT WORD /ERROR                                  |

| 0065<br>0066<br>0067                                                          | 1177<br>7100<br>5037                                                         | ccz,        | TAD WRD<br>CLL<br>JMP STD-1                                                    |                                                               |

| 0070<br>0071<br>0072                                                          | 1506<br>7402<br>7200                                                         | CC3,<br>El, | TAD I SA<br>HLT<br>CLA                                                         | /ERROR: AC CONTAINS INCORRECT WORD                            |

| 0073<br>0074<br>0075                                                          | 1106<br>7402<br>7300                                                         | ElA,        | TAD SA<br>HLT<br>CLA CLL                                                       | /AC CONTAINS ADDRESS OF /REGISTER IN ERROR                    |

| ØØ76                                                                          | 5Ø65                                                                         | CC4,        | JMP CC2                                                                        |                                                               |

| 0077<br>0100<br>0101<br>0102<br>0103<br>0104                                                                              | 7640<br>0200<br>0001<br>0010<br>0002<br>0000                                              | HOT,<br>ROT,<br>POT,<br>NOT,<br>DCT.<br>B°T,                                                                   | 7640<br>200<br>0001<br>10<br>2<br>0000 |   | /CONSTANTS |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------|---|------------|

| Ø1 Ø5<br>Ø1 Ø6<br>Ø1 Ø7<br>Ø1 1 Ø<br>Ø1 1 1                                                                               | 9999<br>9999<br>9999<br>9999                                                              | PAT.<br>SA,<br>COM,<br>RD,<br>MUD,                                                                             | Ø<br>Ø<br>Ø<br>Ø Ø Ø Ø                 | • | /VARIABLES |

| BOT<br>CCK<br>CC2<br>CC3<br>CC4<br>COM<br>DOT<br>E1 A<br>HOT<br>NOT<br>PAT<br>RD<br>ROT<br>SA<br>STD<br>STD<br>STX<br>WRD | 010<br>0004<br>0007<br>0007<br>010<br>010<br>011<br>010<br>011<br>010<br>011<br>001<br>00 | 17<br>15<br>16<br>16<br>17<br>17<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 |                                        |   |            |

# **APPENDIX**

MAINDEC 802 - Memory Checkerboard Test