## M707 Teletype Transmitter

The M707 Teletype Transmitter is a parallel-to-serial Teletype code converter self-contained on a double-height module. This module includes all of the parallel-to-serial conversion, buffering, gating, and timing (excluding only an external clock) necessary to transfer information in an asynchronous manner between a parallel binary device and a serial data line or Teletype device. Either a 5-bit or an 8-bit parallel character can be assembled into a 7.0, 7.5, or 8.0 unit serial character (or a 10.0, 10.5, or 11.0 unit serial character) by the M707 through the use of different pin connections on the module. When conversion is complete, the necessary start bit and selected stop bits (1.0, 1.5, or 2.0 units) have been added to the original parallel character and transmitted over the serial line. In the PDP-15, the Teletype transmitter is connected to assemble 8-bit characters consisting of 11 units.

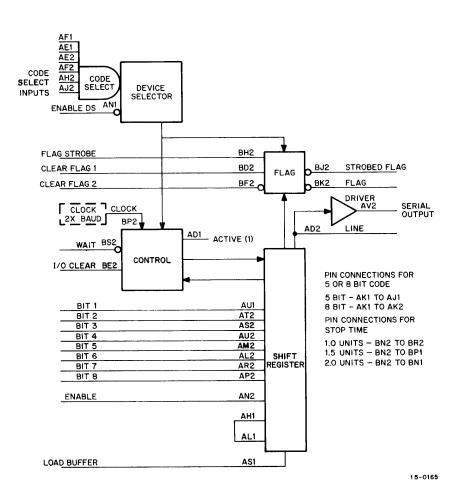

M707 Simplified Diagram

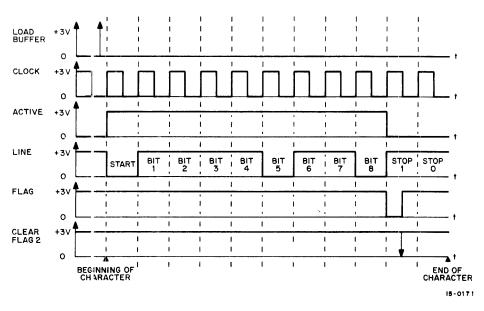

M707 Timing Diagram

The serial character is transmitted with the start bit first, followed by bits 1 through 8 in order, and completed by the stop bits. Coincident with the stop bit being put on the serial line, the FLAG output goes LOW indicating that the previous character has been transmitted and a new parallel character can be loaded into the M707. Transmission of this new character does not occur until the stop bits from the previous character are completed. See the timing diagram for additional information.

In addition to the above listed features, the M707 includes the necessary gating so that it can be used in a half-duplex system with the M706 Device selector gating is also provided to allow this module to be used on the positive bus of a digital system.

The following are the input, output, and power characteristics of the M707 Teletype Transmitter.

INPUTS:

All inputs present one TTL unit load with the exception of the CLOCK input, which presents ten unit loads. Where the use of input pulses is required, the pulse width must be 50 ns or greater.

CLOCK:

The clock frequency must be twice the serial output bit rate. The

CLOCK input can be either pulses or a square wave.

BITS 1 through 8:

A HIGH level at the BITS 1 through 8 inputs is reflected as a logic 1 or mark in the serial output. When a 5-bit code is used, BIT inputs 1 through 5 should contain the parallel data; BIT 6 should be considered as an enable; and BITS 7, 8, and ENABLE should be

grounded.

ENABLE:

The ENABLE input provides the control flexibility necessary for transmitter multiplexing. When grounded during a LOAD BUFFER pulse, the ENABLE input prevents transmission of a character. The ENABLE input can be driven from the output of an M161 for scanning purposes or, in the case of a single transmitter, tied to +3V.

WAIT:

If the WAIT input is grounded prior to the stop bits of a transmitted character, the input then holds transmission of a succeeding character until the input is brought to a HIGH level. A ground on this line does not prevent a new character from being loaded into the shift register. This line is normally connected to ACTIVE (0) on a M706 in half-duplex two wire systems. When not used, the line should be tied to +3V.

**CODE SELECT Inputs:**

When a positive AND condition occurs at the CODES SELECT inputs, the following signals assume their normal control functions: FLAG STROBE; LOAD BUFFER; and CLEAR FLAG 1. These inputs are frequently used to multiplex transmitter modules when signals such as LOAD BUFFER are common to numerous modules. The CODE SELECT inputs can also be used for device selector inputs when the M707 is used on the positive bus of a digital system. The CODE SELECT inputs must be present at least 50 ns prior to any of the three signals that they enable. If it is desired to bypass the CODE SELECT inputs, they can be left open and the ENABLE D.S. line tied to ground.

**CLEAR FLAG 1:**

A HIGH level or positive pulse at the CLEAR FLAG 1 input while the CODE SELECT inputs are all HIGH clears the flag. When not used, this line should be grounded. Propagation delay from input rise until the flag is cleared at the FLAG output is a maximum of 100 ns. The flag cannot be set if the CLEAR FLAG 1 input is held at logic 1.

**CLEAR FLAG 2:**

A LOW level or negative pulse at the CLEAR FLAG 2 input clears the flag. When not used, the CLEAR FLAG 2 input should be tied to +3V. The flag remains cleared if this input is grounded. Propagation from input fall to flag output rise is a maximum of 80 ns. If it is desired to clear the flag on a LOAD BUFFER pulse, CLEAR FLAG 2 can be tied to pin AR1 of the module.

FLAG STROBE:

If the flag is set and the CODE SELECT inputs are all HIGH, a positive pulse at the FLAG STROBE generates a negative-going pulse at the STROBED FLAG output. Propagation delay from the strobe to output is a maximum of 30 ns.

I/O CLEAR:

A HIGH level or positive pulse at the I/O CLEAR input clears the flag, clears the shift register, and initializes the state of the control. This signal is not necessary if the first serial character transmitted after power turn-on is not required to be correct. When not used, or during transmission, the I/O CLEAR input should be at ground.

LOAD BUFFER:

A HIGH level or positive pulse at the LOAD BUFFER input while the CODE SELECT inputs are all HIGH loads the shift register buffer with the character to be transmitted. If the ENABLE input is HIGH when the LOAD BUFFER input occurs, transmission begins as soon as the stop bits from the previous character are counted out. If a level is used, it must be returned to ground within one bit time (twice the period of the clock).

**OUTPUTS:**

All outputs present normal TTL logic levels except the serial output driver, which is an open collector PNP transistor with emitter returned to +5V.

**SERIAL Output:**

This open collector PNP transistor output can drive 20 mA into any load returned to a voltage between +4V and -15V. A logical output or mark is +5V, and a logical 0 or space is an open circuit. If inductive loads are driven by this output, diode protection must be provided by connecting the cathode of a high-speed silicon diode to the output and the diode anode to the coil supply voltage.

LINE:

The LINE output can drive ten TTL unit loads and presents the SERIAL output signal with a logical 1 as +3V and a logical 0 as

ground.

FLAG:

The FLAG output falls from +3V to ground at the beginning of the stop bits driving a character transmission. The M707 can then be reloaded and the flag cleared (set to +3V). The FLAG output can

drive ten TTL unit loads.

STROBED FLAG:

The STROBED FLAG output is the NAND realization of the INVERTED FLAG output and FLAG STROBE. Output drive

is ten TTL unit loads.

+3V:

Pin BJ1 can drive ten TTL unit loads at a +3V level.

POWER:

The power dissipation of the M707 is +5V at 375 mA (maximum).