# M253 16-WORD X 12-BIT RAM

FLIP-FLOPS

M SERIES

Length: Standard Height: Single Width: Single Price \$73

\*FAN-OUT DEPENDS ON PULL-UP RESISTOR (SEE TEXT)

Volts — MA (max.) Pins +5 390 A2 GND C2, J2, T1, V2

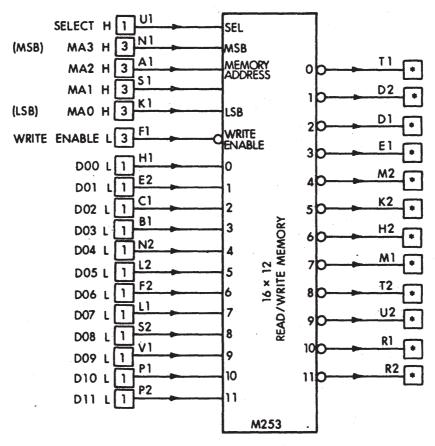

The M253 module is a 192-bit read/write random access bipolar semiconductor memory, organized in a 16-word by 12-bit array.

Each of the 16 memory words is accessible through the 12 data outputs (00-11). Word addressing is in straight binary format on input pins K1, S1, A1, and N1. An overriding memory SELECT input is provided which will protect the information stored in memory when it is Low. The memory is volatile, and information will be lost if the supply voltage is removed.

#### **APPLICATIONS**

This module may be used as a scratchpad memory of 16 words by 12 bits with other modules of the same type, or may be used to construct larger memory arrays where fast reading and writing are required.

#### **FUNCTIONS**

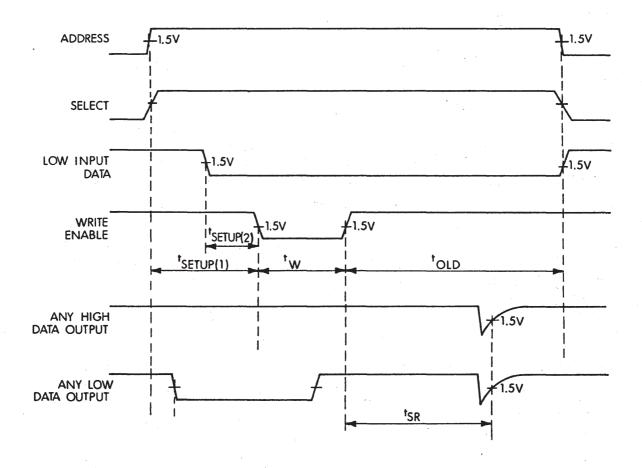

Data on input pins D0-D11 will be written into the memory when the SELECT is HIGH and the WRITE ENABLE is LOW. The location in which it is desired to write the data must be addressed in binary format at the address inputs. The data outputs will assume the opposite state of the information at the data inputs within 100 nanoseconds after the LOW- to HIGH-going edge of the WRITE ENABLE pulse.

To guarantee that writing will occur, the input data, SELECT, and the address lines must all attain a stable level at least five nanoseconds before the WRITE ENABLE input goes LOW. These inputs must maintain this stable level until at least five nanoseconds after the WRITE ENABLE returns HIGH. The WRITE ENABLE input should go LOW for a minimum of 40 nanoseconds.

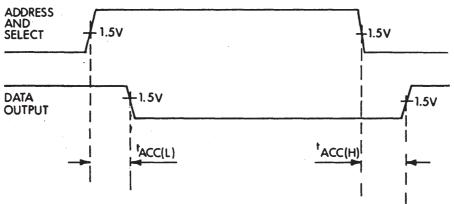

When the WRITE ENABLE and the SELECT are both HIGH, writing cannot take place and the memory is in the read mode. Data stored in the memory will appear at the data outputs when a binary address is present at the address inputs. The access time for retrieving data from memory is 100 nanoseconds. Readout is nondestructive, and the data outputs are inverted from the data originally stored.

| SELECT | WRITE<br>ENABLE | Memory Operation | Output Conditions           |

|--------|-----------------|------------------|-----------------------------|

| Н      | Н               | Read             | Complement of Selected Word |

| Н      | L               | Write            | Undefined                   |

| L      | Н               | Do Nothing       | Н                           |

| L L    | L               | Do Nothing       | Complement of Data Inputs   |

The data outputs (00-11) are open-collector stages that require either a resistor to +5 volts or the M165 module, to act as a pull-up load. Outputs may be connected together. The value of the pull-up resistor to be used on the data outputs should be calculated from the following equation:

$$\frac{5.25}{10 - M}$$

R  $\frac{2.35}{N(0.3) + M}$  H

where: M = number of TTL loads driven by output,

N = number of outputs wire-ORed.

L = TTL unit load input current at low in mA,

H = TTL unit load input current at high in mA,

R = pull-up resistor in Kilohms.

## **TIMING**

|                         | Parameter                                                                            | Min   | Max    |

|-------------------------|--------------------------------------------------------------------------------------|-------|--------|

| t <sub>W</sub>          | Write Pulse Width                                                                    | 40 ns |        |

| tset-up (1)             | Write set-up time. Write enable to follow address enable by (high or low level data) | 5 ns  |        |

| <sup>t</sup> set-up (2) | Write set-up time. Write enable to follow data by                                    | 5 ns  |        |

| tHOLD                   | Address, Enable or Data to follow Write Enable by                                    | 5 ns  |        |

| tsr                     | Sense recovery time after Write                                                      | 5 ns  | 100 ns |

### **SPECIFICATIONS**

ACCESS TIME

<sup>†</sup>ACC(L)= <sup>†</sup>ACC(H)=100 NANOSECONDS MAXIMUM

Maximum Capacitive Load: 30 pF for access time to be within its specified maximum value.