# CHAPTER 9 THE OMNIBUS INTERFACE

#### INTRODUCTION

Interfacing to the PDP-8/E OMNIBUS is accomplished with both hardware and software. For standard interfaces, DEC supplies necessary option modules and the equivalent programs (subroutines and MAIN-DECs) necessary to perform those DEC defined functions. This software is quite adequate to satisfy the operational requirements of each standard option as defined in Chapter 7. However, in the event that the user desires program functions different from those given in the software packages, he must change the software using the standard input/output devices such as a teleprinter, a card reader, or the console switches. Before undertaking this, however, the user should acquaint himself with the software routines (good documentation of the software is provided with each program tape) and read INTRODUCTION TO PROGRAMMING, a volume in the DIGITAL small computer handbook series.

This chapter provides the necessary information for users desiring to build a special interface. It deals primarily with the hardware consideration and it is understood that the user must create his own program for his own defined functions. If the user lacks sufficient experience to design his interface, he can contact his local DEC Sales Office for special assistance.

The means of transferring commands and signals from module to module is accomplished on what is called the "OMNIBUS." All PDP-8/E modules, including options, plug into the OMNIBUS in a significantly accessible manner.

The OMNIBUS is an etched board with rows of connectors soldered to the board. The pin assignment is the same on all connectors. Thus, the OMNIBUS accommodates 96 signals, which feed to 96 pins on the connectors. The user is generally only concerned with those signals that control data transfers, address memory, or contain the data to be transferred. However, the additional signals, such as timing, are readily available on the OMNIBUS to accommodate any tailor-made requirement in the event that the user should design and build his own interface module.

Many advantages are derived from the OMNIBUS approach. Because all connectors on the OMNIBUS contain the same signals, a module can be placed anywhere on the bus at the convenience of the user. All random wiring is eliminated with this type of arrangement. This feature provides greater performance, and reliability. Considerable space is conserved; thus providing a unique packaging capability that allows a high density of electronic circuitry in a small area.

The information in chapter 9 is presented in two sections. The first section describes the many aspects of the OMNIBUS in terms of its physical qualities, the types of interfaces placed on the bus, and the input/output transfer schemes. This information is intended to provide the reader with sufficient background to begin designing an interface control module.

When interfacing to the PDP-8/E, the designer may consider the OMNI-BUS as his interface. If he follows the rules specified in section 1 of this chapter, he is more than half way toward designing his own interface. The nature of the OMNIBUS and all 96 signals are defined in a manner that makes interfacing relatively easy to accomplish.

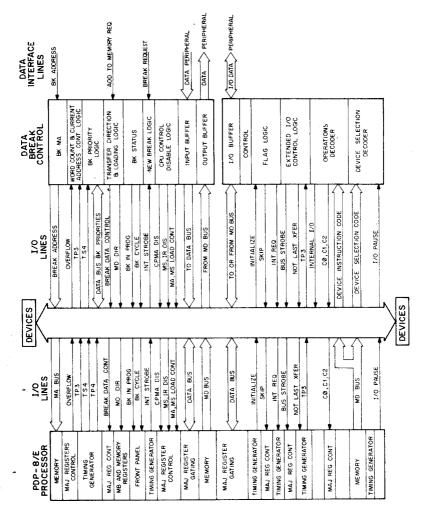

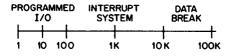

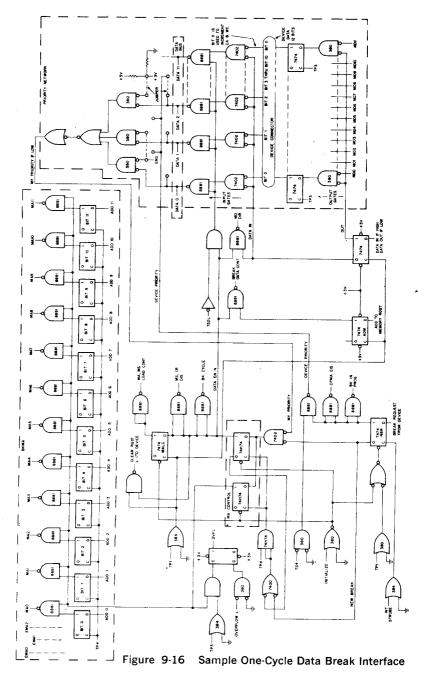

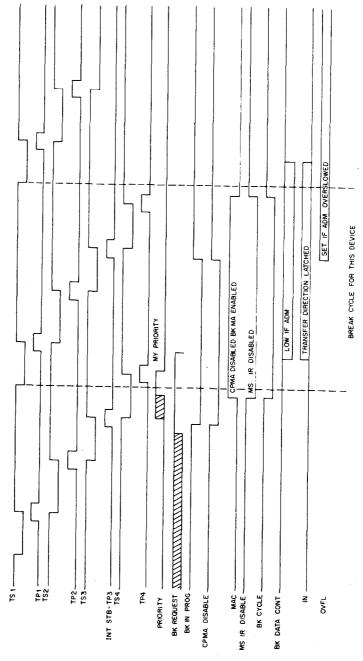

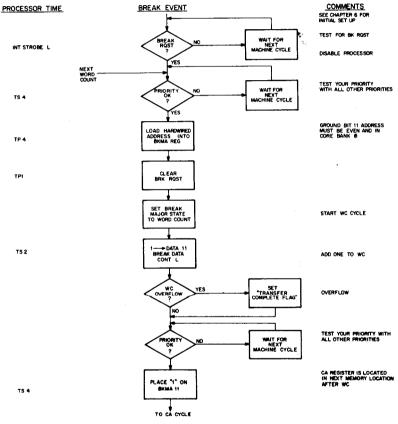

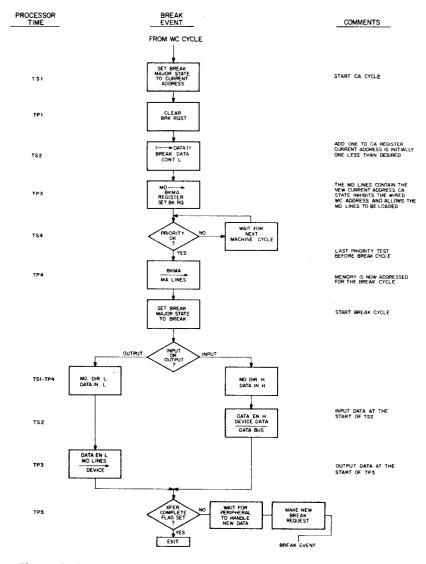

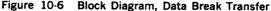

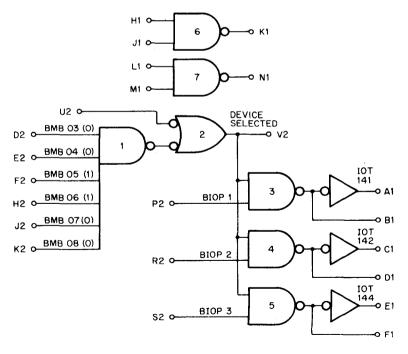

Section 2 identifies the Data Transfer types and some guidelines to help the designer choose the transfer techniques for his needs; section 3 provides a general guideline for the designer building a Programmed I/O Interface Control Module; section 4 provides a general guideline for the designer building either a single-cycle or a three-cycle Data Break Interface; section 5 provides general design and construction guidelines. Section 6 includes some PDP-8/E interface hardware.

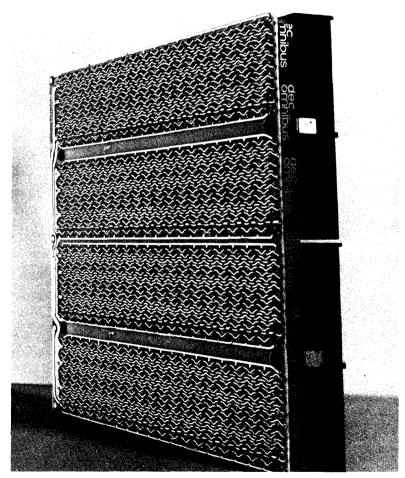

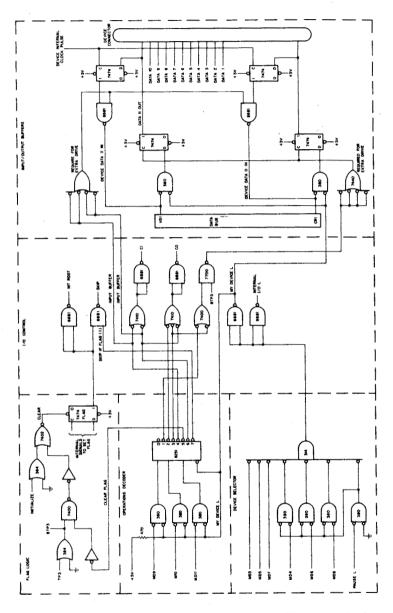

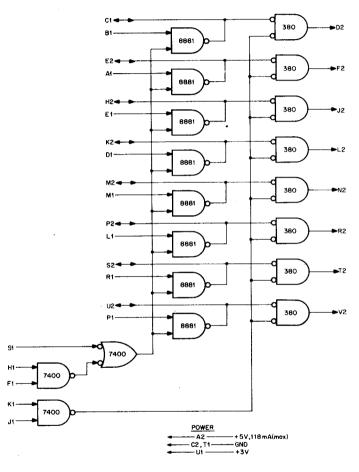

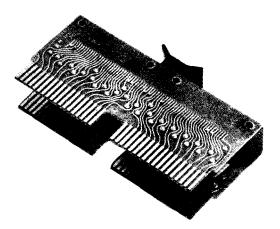

Figure 9-1 PDP-8/E OMNIBUS

## SECTION 1 OMNIBUS DESCRIPTION

#### BUS STRUCTURE

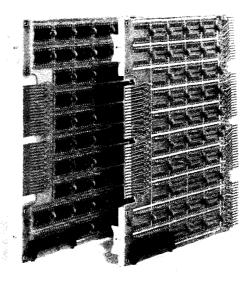

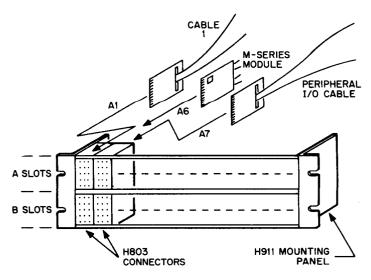

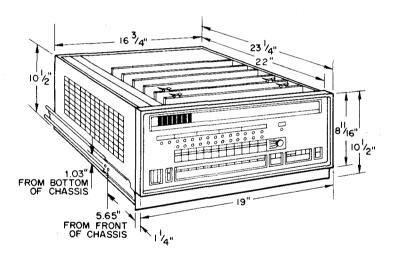

The OMNIBUS (H919 OMNIBUS Assembly) is a back plane etched circuit board with ten H803 connectors mounted onto the board and wave soldered. The OMNIBUS is  $10\frac{1}{2}$  inches by  $10\frac{1}{2}$  inches with a  $1\frac{5}{8}$  inch thickness. The OMNIBUS is attached to the bottom of the PDP-8/E mounting box and is the means by which all modules are connected. Figure 9-1 shows the OMNIBUS with all connectors mounted. A single assembly accommodates 20 PDP-8/E modules.

The OMNIBUS is designed so that all back plane wiring is eliminated and so that every pin in a given connector slot is defined. All modules plugging into the bus are PDP-8/E modules. If a functional unit on the bus requires more than one module, Type H851 edge type connectors on the top of the board connect multiple boards together. For cables to the "outside world," connectors on the side of the module connect to a shielded coaxial or flat ribbon cable. In this arrangement, up to 2 connectors for each module may be used.

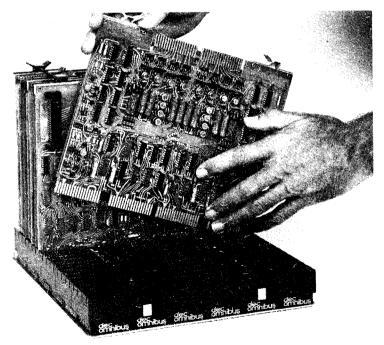

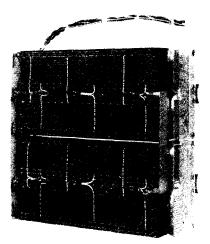

Figure 9-2 shows the OMNIBUS with modules plugged into it. Each module functional unit can be placed anywhere on the bus or removed from the bus without affecting the operation or performance of the rest of the system not requiring that module.

Figure 9-2 PDP-8/E Modules mounted on the OMNIBUS

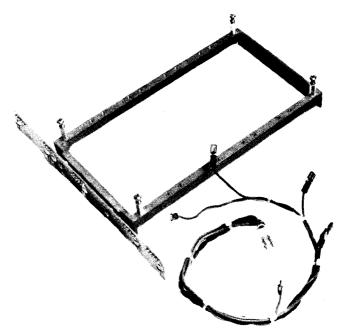

Each OMNIBUS contains 20 slots; two assemblies with a M935 bus connector provides 40 slots, two of which are used to interconnect the assemblies. Thus, 38 slots are available when the OMNIBUS Expansion unit is used. However, the OMNIBUS can be expanded to accommodate an additional 37 modules. This is illustrated in Figure 9-3, which shows the basic OMNIBUS connected to the OMNIBUS expansion unit.

Figure 9-3 The System Expansion Capability.

#### BUS SPECIFICATIONS

Logic Levels

Logic 1—Max Voltage: 0.4V Min Voltage: -0.5V Logic 0—Max Voltage: 5.0V

Min Voltage: 3.0V

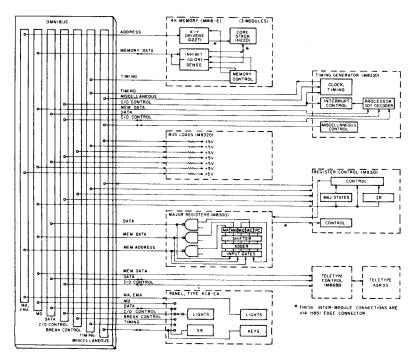

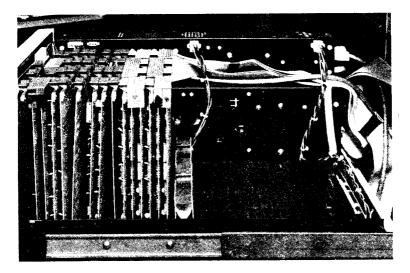

### SYSTEMS CONFIGURATION

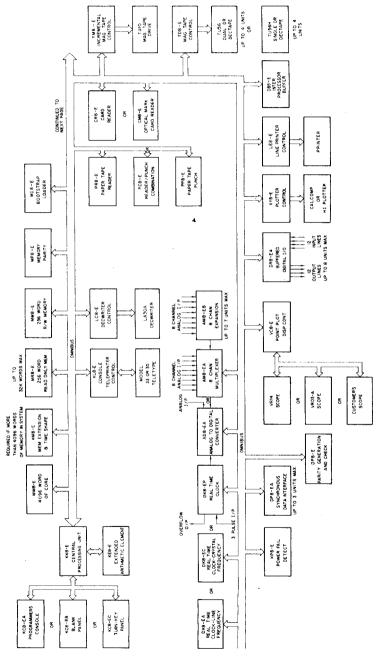

The PDP-8/E with all primary options is identified in Figure 9-4. The basic system contains the central processor (4 modules) the programmer's console (1 module), 4K memory (3 modules), a shield (1 module) and a console Teletype control (1 module).

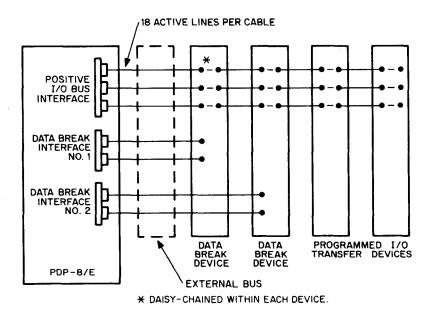

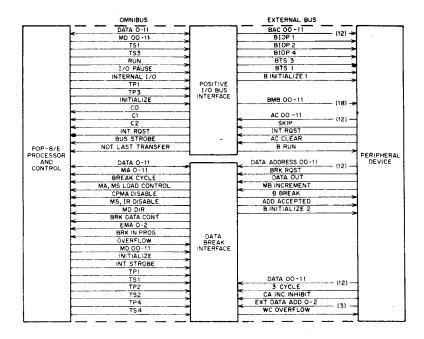

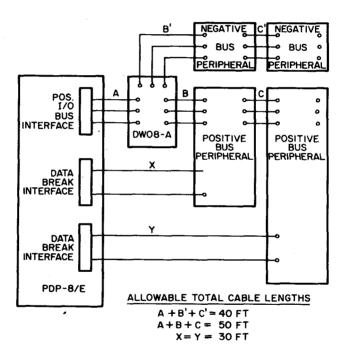

System expansion is easily accomplished simply by adding "off-theshelf" control units necessary to accommodate the corresponding peripheral equipment, if additional machine capability is desired. For example, if it were desired to add additional memory capability to a basic PDP-8/E, a Memory Extension Control and Time Share Option, type KM8-E, could be added. Then 4K memory units could be added, up to a maximum 32K capability. For those customers who wish to use PDP-8/I or PDP-8/L compatible peripherals, an external bus option such as the Positive 1/O Bus Interface Module, type KA8-E, and the Data Break Interface Module, type KD8-E, connects to the OMNIBUS to provide interfacing capabilities.

Figure 9-4 PDP-8/E-OMNIBUS Configurator

Almost all types of peripherals are included as an option to allow the user to expand his system to his own requirements. However, in the event that the user has a unique requirement such as a special control system, he may build his own control module by following the rules specified in this chapter. Refer to Chapter 11 for planning and installation.

#### RELATIONSHIP OF THE EXTERNAL BUS TO THE OMNIBUS

The External Bus, which is mechanically and electrically organized the same as the I/O bus on the PDP-8/L or the PDP-8/I with KA8-I, plugs into the OMNIBUS by way of the Positive I/O Bus interface and the Data Break interface. Each of these modules receives the same signal on the same pins as any other module plugged into the OMNIBUS. The interfacing details to the External Bus are given in Chapter 10 of this handbook.

#### OMNIBUS SIGNALS

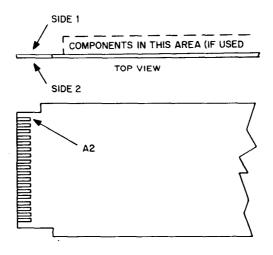

The signals and pin assignments of the OMNIBUS are given in Figure 9-5. The L and H after the signal name identifies the most common assertion level. Bus Loads are provided in Figure 9-6. Each load corresponds to a description of each signal that is provided in Tables 9-1 through 9-4. The tables also identify the specific circuit by type 1 through 10 under the column heading "TYPE LOAD", "TYPE DRIVER". The corresponding circuit type is illustrated in Figure 9-6. The loading rules presented later in this chapter provide information on the electrical properties of these lines.

| l       | P:N  | 6         | D2                                                                                                                 | 5                                            | C2                              | 19        | 82                 | A1       | A2            |

|---------|------|-----------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------|-----------|--------------------|----------|---------------|

| Ψ₹      | 4    | TP        | +15V                                                                                                               | ТР                                           | +5V                             | ТР        | +5V                | ТР       | +5V           |

| L       | æ    | TP        | - 15V                                                                                                              | TΡ                                           | - 15                            | TP        | - 15V              | тР       | - 15V         |

| 1       | U    | GND       | GND                                                                                                                | GND                                          | GND                             | GND       | GND                | SP GND * | GND           |

| I       | 0    | MABL      | IRØL                                                                                                               | I/0 PAUSE L                                  | TP1 H                           | MA4L      | INT STROBE H       | MAOL     | EMAØ L        |

| L.,     | ω    | MAGL      | IR1L                                                                                                               | CØL                                          | TP2 H                           | MAS L     | BRK IN PROG L      | MAIL     | EMA 1L        |

| i       | u    | GND       | GND                                                                                                                | GND                                          | GND                             | GND       | GND                | GND      | GND           |

| <b></b> | т    | MATOL     | IR2 L                                                                                                              | C1L                                          | трзн                            | MAGL      | MA, MS LOAD CONT L | MAZL     | EMA2 L        |

| L       | 5    | MATTL     | FL                                                                                                                 | C2 L                                         | тран                            | MA7L      | OVERFLOW L         | MA3 L    | MEM START L   |

| L       | ×    | MD8L      | DL                                                                                                                 | BUS STROBE L                                 | T SI L                          | MD4L      | BREAK DATA CONT L  | MD@ L    | MD DIR L      |

| 1       | -    | MD9 L     | E L                                                                                                                | INTERNAL I/O L                               | TS2 L                           | MD5 L     | BREAK CYCLE L      | MD1 L    | SOURCE H      |

| 1       | Σ    | MD10 L    | USER MODE H                                                                                                        | NOT LAST XFER L                              | TS3 L                           | MD6L      | LA ENABLE L        | MD2 L    | STROBE H      |

| Ι.,     | z    | GND       | GND                                                                                                                | GND                                          | GND                             | GND       | GND                | GND      | GND           |

| ι       | a    | MDIIL     | F SET L                                                                                                            | INT ROST L                                   | TS:4 L                          | MD7 L     | INT IN PROG H      | MD3 L    | INHIBIT H     |

| L       | æ    | DATA 8 L  | PULSE LA H                                                                                                         | INITIALIZE H                                 | LINK DATA L                     | DATA 4 L  | RES 1 H            | DATA Ø L | RETURN H      |

| L.,     | S    | DATA 9 L  | STOP L                                                                                                             | SKIP L                                       | LINK LOAD L                     | DATA 5 L  | RES 2 H            | DATA 1 L | WRITE H       |

| 1       | F    | GND       | GND                                                                                                                | GND                                          | GND                             | GND       | GND                | GND      | GND           |

| 1       | 5    | DATA 10 L | KEY CONTROL L                                                                                                      | CPMA DISABLE L                               | INDIL                           | DATA 6 L  | RUN L              | DATA 2 L | ROM ADDRESS L |

| Ļ       | >    | DATA 11 L | SW                                                                                                                 | MS, IR DISABLE L                             | IND2 L                          | DATA 7L   | POWER OK H         | DATA 3 L | LINK L        |

| 1 / /   | 1 // |           | * THIS FIN IS CONNECTED TO GROUND ON THE BUS, BUT SERVES AS A LOGIC<br>SIGNAL WITHIN MODULES TO FACILITATE TESTING | TED TO GROUND ON THI<br>ULES TO FACILITATE 7 | E BUS, BUT SERVES AS<br>TESTING | S A LOGIC |                    |          |               |

| L       |      |           | (                                                                                                                  |                                              | QUAD MODULE<br>(COMPONENT SIDE) |           |                    |          |               |

| -       | Į    |           |                                                                                                                    |                                              |                                 |           |                    |          |               |

Figure 9-5 OMNIBUS Pin Assignment

ABCDEFIJKLNPRSTUV

5 5

A B C O M F T J K L M Z P R S F D V

CONNECTOR D SIDE 2

05 |

CONNECTOR D SIDE 1

81 82-

A1 42

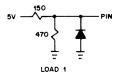

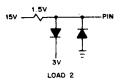

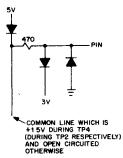

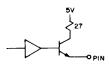

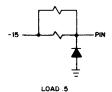

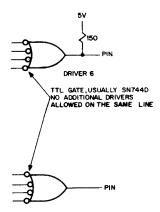

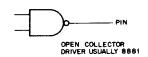

LOAD 3

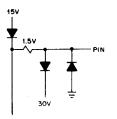

COMMON LINE WHICH IS +30V DURING "INT STROBE" AND OPEN CIRCUITED OTHERWISE

LOAD 4

Figure 9-6 OMNIBUS Loads

DRIVER

DRIVER 8

9-8

| SIGNAL            | ORIGIN                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                             | .TYPE<br>LOAD | TYPE<br>DRIVER |

|-------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|

| MD0-11            | Memory                     | Provides IOT instruction as fol-<br>lows:<br>6 <sub>8</sub> (used by processor)                                                                                                                                                                                                                                                                                                                      | 2             | 8              |

|                   |                            | Device of                                                                                                                                                                                                                                                                                                                                                                                            | •             |                |

|                   |                            | 0 1 2 3 4 5 6 7 8<br>Device Select                                                                                                                                                                                                                                                                                                                                                                   | 91            | .0 11          |

|                   |                            | LOGIC STATES: Ground = $1$<br>+3V = $0$                                                                                                                                                                                                                                                                                                                                                              |               |                |

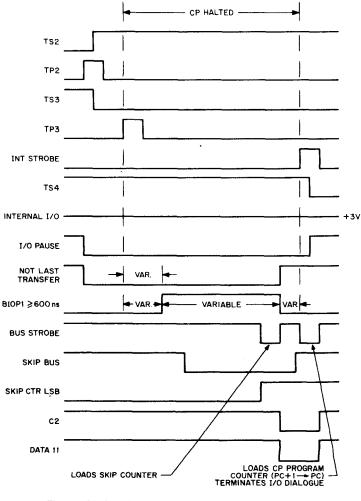

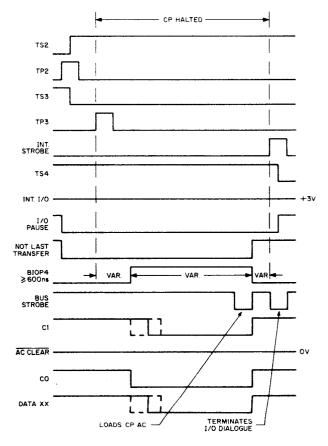

| I/O PAUSE         | L Processor                | Used to gate the device select<br>and device operation codes into<br>the programmed I/O interface<br>decoders and generate BUS<br>STROBE at TP3 and NOT LAST<br>XFER H. I/O PAUSE is grounded<br>when MDO-2 equals 6 (octal)<br>during FETCH and not USER<br>MODE. PAUSE begins 150 ns<br>after the start of TP1 and con-<br>tinues until 150 ns after the<br>start of TP3 if INT STROBE is<br>high. | 1             | 6              |

| TP 3 H            | Processor                  | TP3H is used to clear the flag<br>and clock the output buffer of a<br>Programmed I/O interface. It is<br>generated in the timing gener-<br>ator as a positive-going 100 ns<br>pulse. (See timing pulses in<br>Table 9-1c)                                                                                                                                                                            | 1             | 6              |

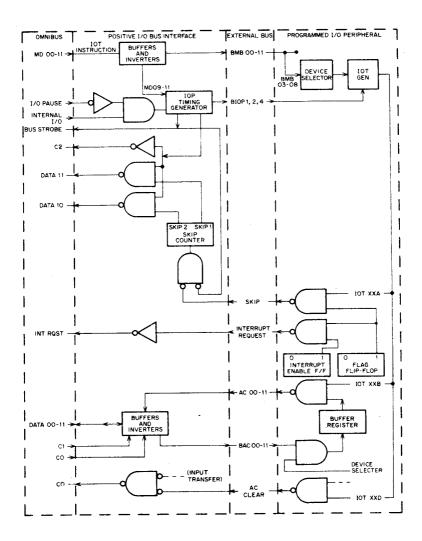

| INTERNAL<br>I/O L | Interface                  | Signal INTERNAL I/O is<br>grounded by the device selector<br>decoder. The Positive I/O Bus<br>Interface cannot generate IOP's<br>when this line is grounded. This<br>inhibits decoding any Internal<br>OMNIBUS IOT instructions. Fail-<br>ure to ground this line will re-<br>sult in long IOT timing.                                                                                               | 2             | 8              |

| DATAO-11          | Processor and<br>Interface | The 12 DATA lines called DATA<br>BUS serves as a bidirectional<br>bus for both input and output<br>data, between the AC register<br>in the processor and the inter-<br>face buffer register. The proces-                                                                                                                                                                                             | 4             | 8              |

## Table 9-1 Programmed I/O OMNIBUS Signals

.

| SIGNAL                | ORIGIN    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TYPE<br>LOAD | TYPE<br>Driver |

|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

|                       |           | sor internal gating and loading<br>is controlled by CO, C1, and C2<br>signals. During TS3 of an IOT<br>instruction, the contents of the<br>DATA BUS is applied to the<br>processor's major register gat-<br>ing in accordance with the C<br>lines. For output transfers, in-<br>formation must be taken from<br>the DATA BUS by edge trigger-<br>ing only, using the leading edge<br>of TP3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                |

| C lines<br>C0, C1, C2 | Interface | Signals CO, C1, C2 determine<br>the type of transfer between a<br>device and the processor. These<br>lines, control the data path<br>within the processor and deter-<br>mine if data is to be placed<br>onto the DATA BUS or received<br>from the DATA BUS. They are<br>also used to develop the nec-<br>essary load control signals re-<br>quired to load either the AC<br>register or the PC register.<br>When it is time for a device to<br>make either an input or output<br>transfer, the device will ground<br>the appropriate combination of<br>C control lines so that Major<br>Register gating and Register<br>loading is made possible.<br>Refer to the Table below for<br>Control line combinations and<br>type of transfer. When the C<br>Control lines are grounded at<br>the Interface, the time required<br>for the bus lines to settle must<br>be considered. | 2            | 8              |

|                       |           | If, for example, data is to be<br>transferred from a device to the<br>PC "Register, data must be<br>transferred from the DATA BUS<br>(see Table 9-1a) to the adders.<br>From the adders, data is loaded<br>into the PC with a PC load sig-<br>nal. PC load is developed from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                |

|                       |           | 9-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                |

## Table 9-1 Programmed I/O OMNIBUS Signals (Continued)

| SIGNAL     | ORIGIN    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                              | TYPE<br>LOAD | TYPE<br>DRIVER |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

|            |           | C2L•BUS STROBE. Since BUS<br>STROBE is generated by the<br>processor during a normal IOT,<br>C2L should be grounded not<br>less than 280 ns before BUS<br>STROBE. If the PC register is<br>to be modified (both the PC<br>and DATA applied to the<br>adders), C2 L should be<br>grounded not less than 400 ns<br>before Bus STROBE L is<br>generated.                                                                 |              |                |

| SKIP L     | Interface | An IOT checks the flag for a ONE state and causes the device logic to ground the SKIP line if the flag is set. The result (PC $+$ 1) is loaded into the CPMA. The SKIP line is sampled by the processor at TP3, and must be grounded 50 ns before TP3 in order for the skip to occur.                                                                                                                                 | 2            | 8              |

| INT RQST L | Interface | Signal INT RQST is part of the<br>Interrupt System. It is the<br>method by which the device<br>signals the processor that it has<br>data to be serviced. When the<br>device flag is set, signal INT<br>RQST is immediately grounded.<br>The processor samples the INT<br>RQST line at INT STROBE time.<br>If all the conditions for an in-<br>terrupt are met, the processor<br>then asserts signal INT IN<br>PROG H. | 2            | 8              |

## Table 9-1 Programmed I/O OMNIBUS Signals (Continued)

1

|                                                            |              | •           |                   | lable 9-1a                                     | able of                  | lable of Iranster Control Signals                            | olgitats                                                                                                |                                                                                                                |

|------------------------------------------------------------|--------------|-------------|-------------------|------------------------------------------------|--------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                            | F            | Transfer    | fer               |                                                | Bus Set-up               |                                                              |                                                                                                         | Contents of                                                                                                    |

|                                                            | 0            | Control     | ō                 | Information                                    | Time with                | Action Required                                              |                                                                                                         | Data Bus                                                                                                       |

| Type of<br>Transfer                                        | 5            | Lines<br>C1 | Lines<br>C0 C1 C2 | Gated onto                                     | respect to<br>BUS STROBE | by Peripheral<br>at Interface                                | Action by<br>Processor**                                                                                | During<br>Transfer                                                                                             |

| Output<br>AC→ Data<br>BUS<br>AC un <sup>-</sup><br>changed | ; I          | ; r         | I                 | AC Reg.                                        | 280 ns                   | Load data bus<br>into buffer.                                | Transfers AC to<br>Data Bus. AC<br>remains un-<br>changed.                                              | AC register only.<br>User modifica-<br>tion of this type<br>of transfer may<br>bring undesir-<br>able results. |

| Output<br>AC-→ DATA<br>Bus                                 |              | I           | т                 | AC Reg.                                        | 280 ns                   | Ground CO.                                                   | Transfers AC to<br>Data Bus and<br>clears AC.                                                           | AC Register.                                                                                                   |

| AC Cleared                                                 |              |             |                   |                                                |                          | Load data bus<br>into buffer.                                |                                                                                                         |                                                                                                                |

| Input<br>AC V<br>Peripheral<br>Data                        | I            | -           | т                 | Peripheral<br>Data &<br>Contents of<br>AC reg. | 280 ns                   | Gate peripheral<br>data to data bus.<br>Ground C1.           | Transfers con-<br>tents of AC to<br>the data bus.<br>The ORed result<br>loaded into the<br>AC.          | AC ORed with<br>Peripheral Data.                                                                               |

| Input Jam-<br>Data Bus<br>→ AC                             | <u>ب</u>     | <u> </u>    | I                 | Peripheral<br>data                             | 280 ns                   | Gate peripheral<br>data to data bus.<br>Ground CO & C1.      | Transfer data<br>bus to AC reg-<br>ister.                                                               | Peripheral Data                                                                                                |

| Relative<br>Jump<br>Data Plus<br>PC→ PC                    | *            | I           | <u>ب</u>          | Peripheral<br>data                             | 400 ns                   | Gate peripheral<br>data to data bus.<br>Ground C2.           | Transfer con-<br>tents of PC and<br>Data Bus to ad-<br>ders. Load the<br>added result in-<br>to the PC. | Peripheral Data                                                                                                |

| Absolute<br>Jump<br>Data Bus<br>→ PC                       | 4            |             | -                 | Peripheral<br>data                             | 280 ns                   | Gate peripheral<br>data to data bus.<br>Ground C1<br>and C2. | Transfer con-<br>tents of data<br>bus to PC.                                                            | Peripheral Data                                                                                                |

| * Don't Care<br>** Bus Strobe loads AC or PC.              | re<br>be loa | ds A        | VC or I           | IJ,                                            |                          |                                                              |                                                                                                         |                                                                                                                |

Table 9-1a Table of Transfer Control Signals

# Table 9-2 Additional Programmed I/O OMNIBUS Signals for the Sophisticated User

| SIGNAL          | ORIGIN                                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TYPE<br>LOAD | TYPE<br>Driver |

|-----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| BUS<br>STROBE L | Interface<br>during an<br>extended<br>I/O | Signal BUS STROBE is used to<br>load the AC and PC registers.<br>It is normally grounded by the<br>processor during an I/O PAUSE<br>and NOT LAST XFER H at TP3<br>time. Consequently, unless spe-<br>cial I/O operations are being<br>performed, the designer of an<br>interface need not concern him-<br>self with BUS STROBE. BUS<br>STROBE is a 100 ns negative-<br>going pulse.                                                                                                                                                                                                                                                                                                                                     |              |                |

|                 | ·                                         | For input transfers to the AC,<br>or Absolute Jumps, data must<br>be placed on the DATA BUS a<br>minimum of 280 ns prior to<br>BUS STROBE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                |

|                 |                                           | For Relative Jumps, data must<br>be placed on the DATA BUS a<br>minimum of 400 ns prior to<br>BUS STROBE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                |

|                 |                                           | Input transfers to the AC and<br>Absolute Jumps can take place<br>within a normal IOT. However,<br>Relative Jumps, which require<br>400 ns, present a timing prob-<br>lem. As with any operation<br>requiring more than 280 ns,<br>the problem is dealt with by<br>stopping machine timing and<br>grounding BUS STROBE at the<br>interface. Allow 400 ns after<br>data is applied to the DATA<br>BUS before grounding BUS<br>STROBE for 100 ns. Ground<br>NOT LAST XFER at least 50 ns<br>before TP3. This stops the pro-<br>cessor timing at TP3 until NOT<br>LAST XFER is again high thereby<br>extending the length of TS3.<br>Timing will continue only if NOT<br>LAST XFER is high and BUS<br>STROBE is generated. |              |                |

| SIGNAL             | ORIGIN             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TYPE<br>LOAD | TYPE<br>DRIVER |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| NOT LAST<br>XFER L | I/O Inter-<br>face | A ground level on this line in-<br>dicates to the processor that<br>the next BUS STROBE does not<br>terminate the I/O transaction.<br>Since most internal I/O devices<br>use only one transaction per<br>IOT, this signal is normally not<br>grounded by the internal I/O<br>devices. Thus, the internal de-<br>vices usually only asserts its<br>"C" lines and INTERNAL I/O.<br>However, if the transfer is such<br>that more than 280 ns are re-<br>quired between the time the<br>device data is applied to the<br>DATA BUS and signal BUS<br>STROBE is grounded, or if mul-<br>tiple transfers are being made<br>in a single IOT, the processor<br>timing may be stalled long<br>enough to complete the trans-<br>fer. If for example the contents<br>of the PC is to be added to the<br>contents of the device data, ad-<br>ditional time beyond the 280 ns<br>is required to allow the ripple<br>action of the adders to be com-<br>pleted. In this case, 120 ns<br>more are needed. The device<br>must ground NOT LAST XFER<br>at least 50 ns before TP3. At<br>TP3, the processor timing stalls.<br>When device data is applied to<br>the DATA BUS, the device must<br>wait 400 ns and then ground<br>BUS STROBE for 100 ns. Signal<br>NOT LAST XFER should be<br>brought high before the time<br>when BUS STROBE is generated.<br>This will restart timing with TS4<br>and negate signal I/O PAUSE L. | 2            | 8              |

|                    |                    | As indicated in the following<br>flow diagram (Figure 9-7), NOT<br>LAST XFER accomplishes three<br>basic tasks:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                |

Table 9-2

Additional Programmed I/O OMNIBUS Signals for the Sophisticated User (Continued)

Table 9-2

Additional Programmed I/O OMNIBUS Signals for the Sophisticated User (Continued)

Figure 9-7 NLT Flow Diagram

| SIGNAL             | ORIGIN                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                          | TYPE<br>LOAD | TYPE<br>DRIVER |

|--------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

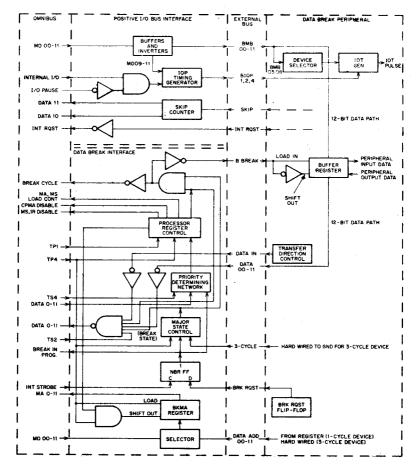

| MD0-11             | Memory<br>and<br>Processor | In addition to its function under I/O, MD provides a one-way, 12-<br>line data path between memory<br>and the Data Break Interface.<br>LOGIC STATES: high = 0<br>ground = 1                                                                                                                                                                                                                                                       | 2            | 8              |

| DATAO-11           | Data<br>Break<br>Interface | The 12 DATA lines called DATA<br>BUS are used to determine Break<br>Priority, and to carry input data<br>during a Data Break Cycle.<br>LOGIC STATES: high $= 0$<br>ground $= 1$                                                                                                                                                                                                                                                   |              |                |

| INT<br>STROBE H    | Processor                  | This 100 ns positive-going pulse<br>occurs at TP3 (except for ex-<br>tended I/O and long EAE cycles)<br>and is a necessary input to the<br>timing chain to continue timing<br>into TS4. For extended I/O and<br>long EAE cycles, INT STROBE<br>H is generated by BUS STROBE<br>with NOT LAST XFER H. The<br>leading edge of INT STROBE is<br>the latest time in the machine<br>cycle at which a break request<br>can be accepted. | 1            | 6              |

| BREAK IN<br>PROG L | Data<br>Break<br>Interface | This line is grounded at INT<br>STROBE time if a break request<br>is being made. This signal<br>causes the BRK PROG lamp on<br>the front panel to be lit during<br>the next TS1 to indicate that a<br>data break device has an active<br>break request.                                                                                                                                                                           | 2            | 8              |

| CPMA<br>DISABLE L  | Data<br>Break<br>Interface | This line is grounded by the<br>Data Break Device at INT<br>STROBE time if a break request<br>is detected. CPMA BUS L causes<br>the CP's Memory Address regis-<br>ter to be disconnected from the<br>MA lines at the next TP4. At the<br>same time, the BKMA register<br>of the highest priority device<br>must be gated onto the MA<br>BUS within 50 ns of the leading<br>edge of TP4.                                           | 2            | 8              |

## Table 9-3 Data Break OMNIBUS Signals

## Table 9-3 Data Break OMNIBUS Signals (Continued)

| SIGNAL                  | ORIGIN                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TYPE<br>LOAD | TYPE<br>DRIVER |

|-------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| OVER-<br>FLOW L         | Processor                  | This line is driven by a flip-flop<br>that senses the carry from the<br>adders at TP2. The flip-flop is<br>set each time there is a carry<br>or borrow out of the MB and is<br>"ANDed" with TS3 before going<br>to the OMNIBUS. This line is<br>used, for example, during 3-cycle<br>Breaks to indicate that the word<br>count overflow has occurred.                                                                                                                                                                                                                                                                                 | 2            | 8              |

| BREAK<br>DATA<br>CONT L | Data<br>Break<br>Interface | BREAK DATA CONT is grounded<br>when the contents of the MD<br>are to be placed into the adders<br>during a break cycle. This sig-<br>nal is used when a ONE is to<br>be added to memory via the<br>DATA BUS to increment either<br>the Word Count or Current Ad-<br>dress memory location. It is<br>also used to perform an Add to<br>Memory (ADM) type of Break.<br>This line must not be changed<br>during TS2 and is usually<br>changed at TP4. Because MD<br>DIR controls the transfer di-<br>rection of memory data, the fol-<br>lowing truth table relates MD<br>DIR and BREAK DATA CONT to<br>the type of data break transfer. | 2            | 8              |

BREAK DATA CONT USAGE

| Type of Transfer                 | MD DIR       | BREAK DATA CONT | INFO ON DATA BUS |

|----------------------------------|--------------|-----------------|------------------|

| Device→ Memory<br>Memory→ Device | H<br>L*<br>H | H<br>X          | DEVICE INFO<br>X |

| Memory PLUS<br>Device→ Memory    | H            | L               | DEVICE INFO      |

| * Dustanual Mathead              |              |                 |                  |

\* Preferred Method

## Table 9-3 Data Break OMNIBUS Signals (Continued)

| SIGNAL                  | ORIGIN                                        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TYPE<br>LOAD | TYPE<br>DRIVER |

|-------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| MS, IR<br>DIS L         | Data<br>Break<br>Interface                    | This line is grounded at TP4 by<br>the Break Device having the<br>highest priority. This signal is<br>used to disconnect the outputs<br>of the MAJOR STATE and IR<br>register outputs from the OMNI-<br>BUS and from all circuitry with-<br>in the CP. The processing is<br>terminated at the end of the<br>current instruction cycle and<br>resumes when MS, IR DIS is<br>again high. The start of MS, IR<br>DIS L is the start of the DMA<br>state. In addition, MS, IR DIS L<br>also enables a data path from<br>the DATA BUS to the adders to<br>provide DATA to the MB. | 2            | 8              |

| BREAK<br>CYCLE L        | Data<br>Break<br>Interface                    | BREAK CYCLE is grounded at<br>TP4 by the break device hav-<br>ing the highest priority. This<br>signal causes the BRK lamp on<br>the front panel to be lit during<br>the next TS1 to indicate that<br>the Break Cycle has started.                                                                                                                                                                                                                                                                                                                                           | 2            | 8              |

| MA,MS<br>LOAD<br>CONT L | Data<br>Break<br>Interface                    | This line is grounded at TP1<br>by the device having the highest<br>priority and remains grounded<br>during Break until the TP4 fol-<br>lowing the last Break Cycle.<br>MA,MS LOAD CONT L prevents<br>the CPMA and MS registers<br>from being loaded at TP4.                                                                                                                                                                                                                                                                                                                 | 2            | 8              |

| MD DIR                  | Processor<br>or<br>Data<br>Break<br>Interface | Refer to table 9-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3            | 8              |

Table 9-4 Basic System OMNIBUS Data and Control Signals

| SIGNAL | ORIGIN                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYPE<br>Load | TYPE<br>DRIVER |

|--------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| MD0-11 | Processor<br>and<br>memory | The 12 Memory Data lines<br>carry information to and from<br>memory of the currently ad-<br>dressed location. The contents<br>of the addressed memory loca-<br>tion are applied to the Memory<br>Data lines beginning in the last<br>half of TS1. If the major state<br>is FETCH or DEFER (non-auto<br>index), the contents of the MD<br>lines will not change for the<br>remainder of the cycle. The MD<br>lines serve as the input into<br>memory during every write oper-<br>ation (which occurs during TS3<br>and TS4). If the Major State is<br>DEFER (auto index) or EXE-<br>CUTE, the contents of the MD<br>can change at TP2. This change<br>is controlled by signal MD DIR<br>which allows data to be ap-<br>plied to the MD lines from the<br>memory register when MD DIR<br>is grounded and inhibits the<br>transfer of MB data to mem-<br>ory. The MB register provides<br>the only external means of in-<br>putting into memory and can<br>do so only when MD DIR is<br>high. | 2            | 8              |

|        |                            | For normal machine operation,<br>the MD lines provide instruc-<br>tions, addresses, operands and<br>data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                |

|        |                            | For I/O devices, the MD lines provide the device select and operation codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                |

|        |                            | For data break devices, the MD<br>lines carry data into the device.<br>LOGIC STATES: high $= 0$<br>grounded $= 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                |

Table 9-4 Basic System OMNIBUS Data and Control Signals (Cont.)

| SIGNAL | ORIGIN                                                                        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TYPE<br>LOAD | TYPE<br>DRIVER |

|--------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

| MD DIR | Processor<br>or<br>Program-<br>mer's<br>Console<br>or Data<br>Break<br>Device | The control of external data to<br>memory and data received from<br>memory is provided by signal<br>MD DIR. When high, MD DIR<br>gates the contents of the MB<br>register onto the MD lines and<br>is thereby applied to memory<br>during memory WRITE time.<br>When grounded, MD DIR gates<br>the contents of the memory<br>Sense Amps out to the MD<br>lines during the memory READ<br>time. Thus, MD DIR can con-<br>trol only the place at which data<br>is applied to the MD lines.<br>When data is applied to the MD<br>lines from the MB Register,<br>data cannot be applied to the<br>MD lines from the Sense Amps.                              | 3            | 8              |

|        |                                                                               | During FETCH and DEFER (non-<br>autoindex), the contents of the<br>MD lines cannot change. The<br>instruction or address read<br>from memory is written back<br>into the same memory ad-<br>dressed location. MD DIR L as-<br>sures that these lines will not<br>change. During EXECUTE and<br>DEFER (autoindex), the con-<br>tents of the addressed memory<br>location are applied to the MD<br>lines until TP2. At this time,<br>MD DIR is brough high so that<br>the contents of the MB Register<br>can be applied to the MD lines<br>and subsequently written into<br>the same memory location dur-<br>ing the WRITE portion of the<br>memory cycle. |              |                |

|        |                                                                               | During the manual operation of<br>the processor from the Program-<br>mer's Console, MD DIR can be<br>changed without considering<br>the time states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                |

| SIGNAL  | ORIGIN                                        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYPE<br>Load | TYPE<br>DRIVER |

|---------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

|         | -                                             | During a Data Break Operation,<br>MD DIR is controlled by the<br>Data Break device depending<br>upon the type of transfer (in-<br>put or output). MD DIR should<br>be changed at TP1 time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                |

| MA 0-11 | Processor<br>or<br>Data<br>Break<br>Interface | Used to address memory to any<br>one of 4096 possible locations.<br>This address is changed only<br>at TP4 time. The address is<br>normally developed in the pro-<br>cessor. However, during a data<br>break, the MA lines can be<br>used for break addresses, which<br>originate in the data break mod-<br>ule. When the processor is exe-<br>cuting an instruction, the ad-<br>dress always originates in the<br>processor.<br>LOGICAL STATES: $1 = low$<br>0 = high                                                                                                                                                                                                     | 3            | 8              |

| EMA 0-2 | Processor<br>or<br>Data<br>Break<br>Interface | Used only when the extended<br>memory is provided. These 3<br>bits are combined with the 12<br>bit Memory address to form a<br>15-bit memory address. This is<br>necessary to specify one loca-<br>tion out of 32,768 possible lo-<br>cations. The extended address<br>bits specify the memory field in<br>use. MA11 is the least signif-<br>icant bit and EMA0 is the most<br>significant bit. All 12 or 15<br>lines are high for a zero and<br>low for a one. Thus, if the ma-<br>chine does not contain a<br>Memory Extension Control, the<br>EMA bits are automatically zero<br>(high), selecting the lowest 4K<br>of memory.<br>LOGICAL STATES: $1 = low$<br>0 = high | 3            | 8              |

| Table 9-4 | Basic System | OMNIBUS Data | and Control | Signals (Cont.) |

|-----------|--------------|--------------|-------------|-----------------|

|-----------|--------------|--------------|-------------|-----------------|

Table 9-4 Basic System OMNIBUS Data and Control Signals (Cont.)

| SIGNAL                    | ORIGIN                                                          |                                                                                                                       | FUNCTION                                                                                                                                                            |                                                                                                                        | TYPE<br>Load  | TYPE<br>DRIVER |

|---------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------|----------------|

| DATAO-11                  | Nearly all<br>portions<br>of the<br>machine<br>except<br>memory | BUS service<br>bidirection<br>DATA BU<br>between f<br>AC registe<br>BUS is a<br>Register/I<br>processor<br>capable of | ATA lines ca<br>e as a mu<br>nal bus. Gen<br>IS is the in<br>the periphera<br>er. However,<br>also betwee<br>MQ Register<br>adders; and<br>of applying<br>AC/MQ dat | Itipurpose<br>erally, the<br>/out path<br>al and the<br>the DATA<br>n the AC<br>r and the<br>I therefore<br>peripheral | 4             | 8              |

|                           |                                                                 | spect to                                                                                                              | A BUS usag<br>processor<br>I in the follow                                                                                                                          | timing is                                                                                                              |               |                |

|                           |                                                                 | DATA B                                                                                                                | US USAGE                                                                                                                                                            |                                                                                                                        |               |                |

| Machine<br>Timing         |                                                                 | Majo                                                                                                                  | r States                                                                                                                                                            |                                                                                                                        |               |                |

| Within<br>Major<br>States | F                                                               |                                                                                                                       | D                                                                                                                                                                   | E                                                                                                                      | DMA           |                |

| TS1                       |                                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                 | Indicators                                                                                                                                                          | S                                                                                                                      |               |                |

| т <u>82</u><br>ТS3        | CPU<br>I/O DIAL<br>(Only if a<br>Otherwis                       | in IOT                                                                                                                | NOT<br>USED                                                                                                                                                         | CPU<br>CPU                                                                                                             | DATA<br>NOT L | → MB<br>JSED   |

| TS4                       |                                                                 |                                                                                                                       | Priority [                                                                                                                                                          | Determinati                                                                                                            | on            |                |

| MEM<br>START   | Program-<br>mer's<br>Console<br>or Power<br>Fail Option | This line is grounded for a mini-<br>mum of 100 ns to initiate a<br>memory cycle. It must not be<br>grounded after TP2. Memory<br>cycles continue automatically<br>until STOP is grounded.                                                | 2 |   |

|----------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|

| ROM<br>ADDRESS | Rom                                                     | When this line is high, the Read/<br>Write memory runs normally.<br>When this line is low, the Read/<br>Write memory does not func-<br>tion, despite memory timing sig-<br>nals on the bus. This line is<br>used when a small ROM is used | 3 | 8 |

| SIGNAL                                                       | ORIGIN                   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYPE<br>Load | TYPE<br>DRIVER |

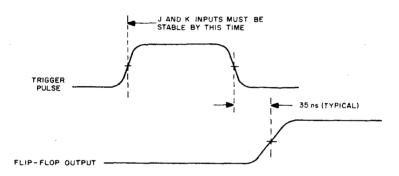

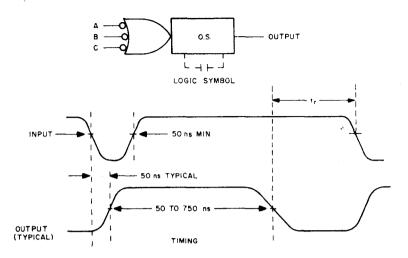

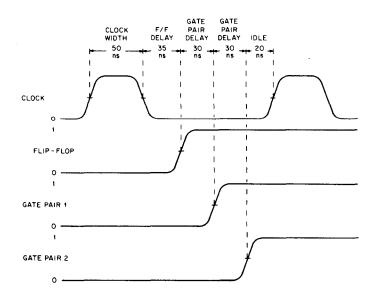

|--------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|