Figure 3-72 EXAM Key Logic

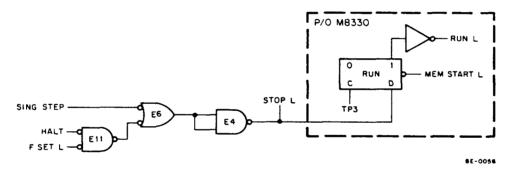

Figure 3-75 SING STEP and HALT Switch Logic

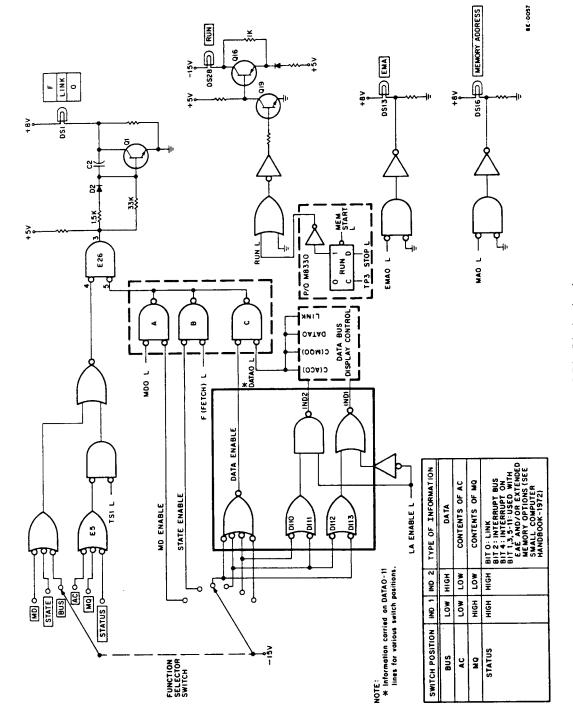

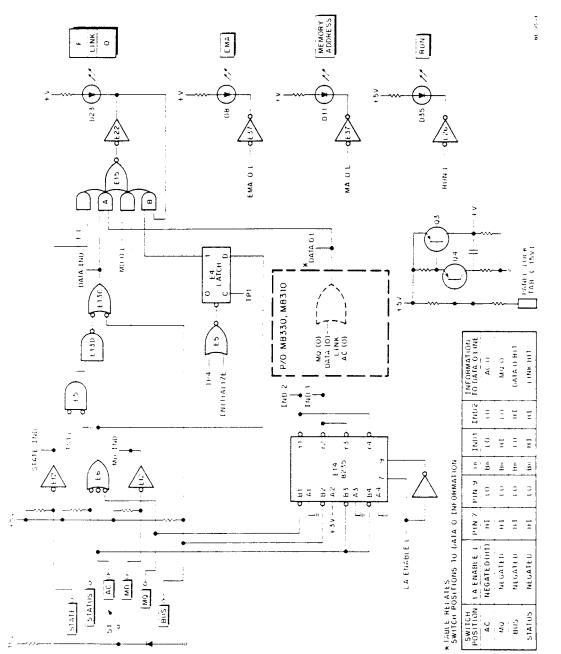

**3.33.1.2** Display – The display logic and circuits are shown in Figure 3-76. There are three groups of indicator lamps and a single lamp (RUN) which, when lit, indicates that timing cycles are being generated. Each of the three groups is represented by its 0 bit, e.g., EMAO L, MAO L, LINK. The circuits used to display EMA and MEMORY ADDRESS are relatively simple; for example, if MAO L is a logic 1, the NAND gate is enabled. The output of the inverter drops to a ground level. The full 8V supply voltage appears across the lamp and causes it to light. The lamp has a small voltage across it when MAO L is a logic 0 (this condition extends the life of the lamp by eliminating the full-on/full-off cycle that often burns out lamp filaments). Consequently, it is lit at this time; however, the lamp is so dim that it is not visible from the front panel.

The circuit used to display RUN is shown above the EMA display circuit. When timing cycles are not being generated, the RUN flip-flop in the Timing Generator is cleared. Q19 and Q16 are in the nonconducting state. The conducting path for the lamp voltage includes the 1000 $\Omega$  resistor; thus, a small voltage appears across DS28, causing it to be dimly lit. When RUN L is asserted by MEM START L, Q19 and Q16, in turn, are turned on. The conducting path from +5V to -15V takes the low impedance route through Q16 (from emitter to collector), rather than through the 1000 $\Omega$  resistor. Thus, the RUN lamp is brightly lit, indicating that timing cycles are being generated.

The RUN indicator uses - 15V and +5V, rather than +8V, to operate the lamp. The +8V supply is removed from the display panel, thus extending the lamp life, when the panel is locked. The - 15V supply is not removed; thus, there is an indication of whether or not the computer is running.

The last group of indicators uses the greatest amount of the display logic and circuitry. This group reflects the data appearing on the MD 00-11 lines, the data appearing on the DATA 00-11 lines, and the state of selected registers and OMNIBUS control lines.

The type of information displayed by this group of indicators is selected at the front panel by a six-position rotary switch, labeled "Function Selector Switch" on Figure 3-76. Note that this switch produces one of three enable signals, depending on its position. If MD ENABLE is asserted, data on the MD 00–11 lines is displayed on the front panel; if STATE ENABLE is asserted, data on selected OMNIBUS signal lines is displayed; if DATA ENABLE is asserted, data on the DATA 00–11 lines is displayed.

If the operator wants to monitor the information on the MD lines, he selects the MD position of the rotary switch. This action asserts MD ENABLE, which is ANDed with MD0 L (the actual circuits within this dashed line are presented in a following paragraph of this section). If MD0 L is a logic 1, the AND gate brings pin 5 of NAND gate E26 to a virtual ground. Because pin 4 is also at ground, E26 is enabled, and pin 3 goes to +5V. Transistor Q1 turns on rapidly because its base drive is supplied through the low-impedance diode path. The switching action of Q1 places a ground on its collector; thus, approximately 8V appear across DS1, causing it to be brightly lit. When E26 is again disabled, pin 3 goes to ground, and diode D2 is reversed-biased. Capacitor C2 begins to discharge through the 33 k $\Omega$  resistor. This long RC time constant ensures that Q1 turns off slowly, increasing the visibility of DS1.

If the operator wants to monitor the content of the AC Register, he selects the AC position; the DATA ENABLE signal is then asserted. In addition, NOR gates D110/D111 and D112/D113 are enabled (the actual circuit within this solid line is presented in a following paragraph). When these gates are enabled, both IND1 and IND2 are asserted, provided that LA ENABLE L is not asserted. These control lines cause the content of the AC Register to be placed on the DATA 00–11 lines. If DATA 0 is a logic 1, E26, pin 5 is grounded; pin 4 is also grounded, but only during TS1, and the content of DATA 0 is displayed on DS1.

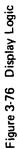

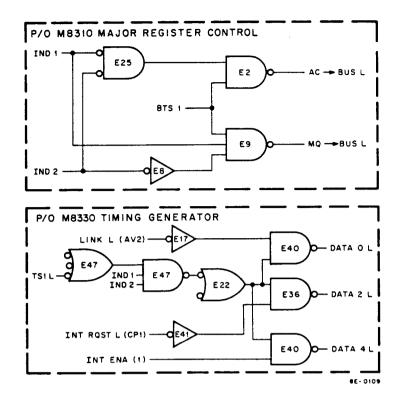

Similarly, the content of the MQ Register, STATUS information, and BUS data can be displayed. The relationship between IND1/IND2 and the type of information displayed is indicated on Figure 3-76. Figure 3-77 shows the logic used to generate control signals in response to IND1 and IND2. This logic is contained within the block designated DATA BUS DISPLAY CONTROL in Figure 3-76.

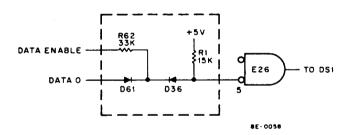

Figure 3-78 shows the circuit represented by AND gate C, enclosed within the dashed line in Figure 3-76 (gate C was arbitrarily selected for discussion; the following can apply to gates A and B, if the signal names and component designations are changed accordingly). Both the DATA ENABLE line and the DATA 0 line must be asserted if pin 5 of E26 is to be true (logic 1, or 0V). If the DATA ENABLE line is not asserted, it is at +5V. The junction of diodes D61 and D36 is +5V; neither diode conducts current; thus, pin 5 is +5V. When the DATA ENABLE line is asserted, both diodes can conduct current. If the DATA 0 line is negated (at 3V), the diode junction goes to approximately 2.3V. Pin 5 then goes to 3V, and E26 remains disabled. When DATA 0 becomes true (0V), the junction goes to -0.7V, pin 5 goes to ground, and E26 is enabled.

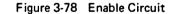

Figure 3-79 shows the circuit represented by the logic gates and enclosed within the solid line in Figure 3-76. Each of the four switch positions asserts DATA ENABLE by switching the DATA ENABLE line to -15V through a diode. Thus, the line, when asserted, is at approximately - 14V.

Figure 3-77 Data Bus Display Control Signals

Figure 3-79 DATA ENABLE/IND SELECT

8E- 0059

Only STATUS asserts DATA ENABLE without affecting either the IND1 or IND2 control lines. Each of the remaining three positions causes one or both of these control lines to be asserted. For example, if BUS is selected, the junction of diodes D113 and D112 goes to approximately – 14V. D115 has a conduction path and, thus, clamps the input of E9 at –0.7V. The resulting positive voltage at the output of E9 enables the following NAND gate to assert IND1. If neither D112 nor D113 conducts, D115 remains in the nonconducting state. The input to E9 remains at +5V, and IND1 is negated.

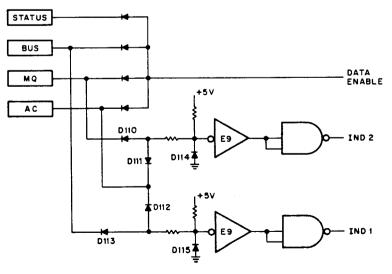

The pulse processor and delay network is shown in Figure 3-80. The input to the network, from inverter E10, is a positive-going level that results from closure of a front panel key. The output from the network is a noise-free, 400 ns gate that is used to assert either MEM START L, PULSE LA, or INITIALIZE.

When a front panel key, EXAM, is depressed, the resulting negative-going edge at the input to inverter E10 may appear as shown in Figure 3-80; i.e., noise spikes appear because of contact bounce. The integrator at the output of E10 is designed to remove the noise spikes. The large capacitance is unresponsive to noise, and, therefore, smooths the edge, while also greatly increasing its rise time. The integrating action, along with the shaping and filtering accomplished by the three transistors, which comprise a Schmitt trigger, produces a positive transition at the collector of Q15. This transition is delayed approximately 20 ms from the negative transition at the input of E10.

The differentiator converts the transition to a positive spike, which triggers a one-shot. This spike is inverted by NOR gate E2; the leading edge of the negative spike is coupled through the 330 pF capacitor and enables NAND gate E2. Simultaneously, the leading edge enables a charging path for the capacitor. This path is sustained by bringing the NAND gate output back to keep the NOR gate enabled. The capacitor charges toward +5V on a long time constant, keeping the NAND gate enabled for approximately 400 ns. When the capacitor has charged to a voltage sufficiently high to disable NAND gate E2, the charging path is removed. Thus, the output of E2 is a 400 ns positive gate and, in this instance, asserts MEM START L for that length of time.

## 3.33.2 KC8-FL Programmer's Console

## 3.33.2.1 Manual Operation

Switch Register – The switch register comprises 12 switches that allow the operator to load the CPMA Register with a 12-bit memory address; to load the extended address bits, if more than 4K of memory is used; to deposit a 12-bit data word in a selected memory location; and to change the content of the AC Register. To carry out these functions, the switch register is operated in conjunction with the DEP, ADDR LOAD, and EXTD ADDR LOAD keys (Figure 3-67).

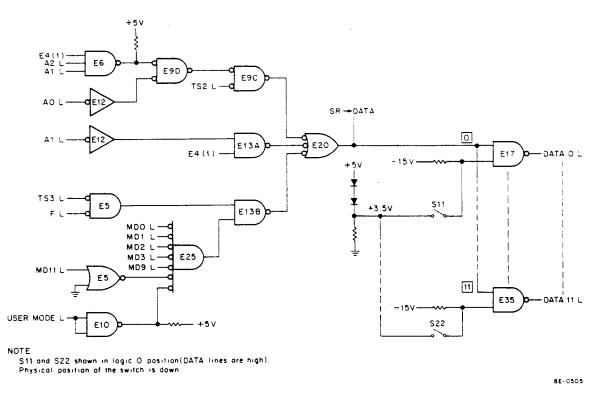

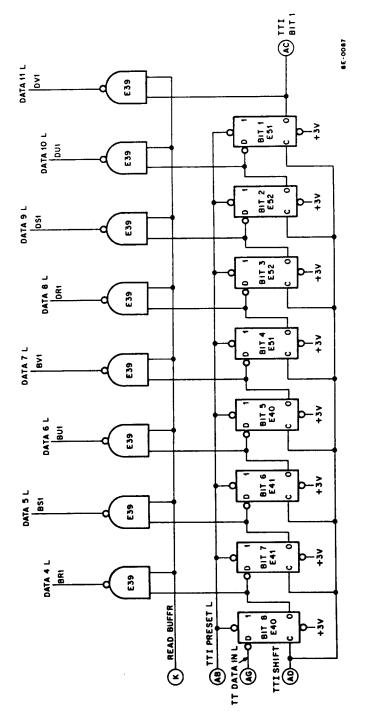

Figure 3-81 illustrates the logic used to set data into the switch register and to place it on the DATA 0-11 lines. The operator selectively closes switches S11 through S22 (designated "0" through "11", respectively, on the front panel). He then causes NOR gate E20 to assert SR  $\rightarrow$  DATA; this signal gates the information represented by the switch register keys onto the DATA lines.

There are three ways for the operator to assert SR  $\rightarrow$  DATA. If he wants to load the CPMA Register, he depresses ADDR LOAD, causing NAND gate E13A to be enabled. (The signals designated A0 L, A1 L, A2 L, and E4 (1) are enable signals that are selectively generated when the operating keys are activated; these signals are described in the *Operating Keys* section.) If he wants to load the extended address bits, he depresses EXTD ADDR LOAD, again causing E13A to be enabled. If he wants to deposit data in a memory location, he raises the DEP key, causing NAND gate E9C to be enabled during TS2 (a variety of information must be carried by the DATA lines;

Figure 3-80 Pulse Processor and Delay Network, Schematic

Figure 3-81 Switch Register Control Logic

time sharing of the lines must be employed to maintain the identity of each type of information). Finally, if the operator wants to change the content of the AC Register under program control, he can program either the OSR instruction (inclusive OR, switch register with AC) or the LAS instruction (load AC with switch register). Either instruction causes gate E25 to be enabled, provided USER MODE L is not asserted by the KM8-E option. When NAND gate E5 is enabled during TS3, E13B is enabled, in turn, and the SR  $\rightarrow$  DATA signal is asserted. NANDing the F L signal in gate E5 ensures that E13B is not enabled during the DEFER or EXECUTE cycle of a multicycle instruction.

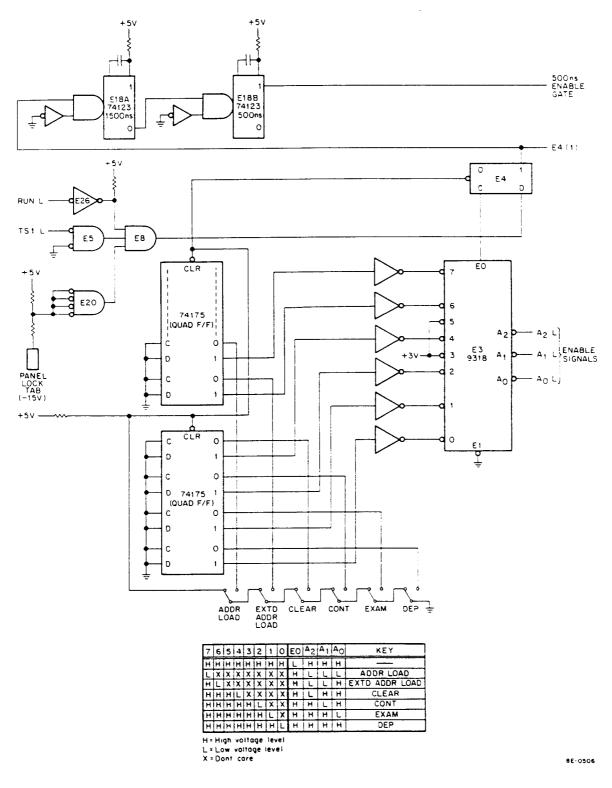

Operating Keys – The operating keys selectively generate enable signals when they are activated. The enable signals, in turn, selectively assert control signals that cause the processor to carry out the intended key function (all but one of the control signals, SR  $\rightarrow$  DATA, are on the OMNIBUS). The logic used to generate the enable signals is shown in Figure 3-82.

Each key controls one of the D-type flip-flops of a DEC 74175 quad flip-flop IC. The normally open contact of each key is connected to the 0 output of a flip-flop. When a key is activated, the ground placed on the 0 output of the associated flip-flop forces the flip-flop to the set state. The 1 output is applied through an inverter to a DEC 9318 8-input priority encoder. Each input of the encoder is assigned a value from 0 to 7. When an input line is activated, the 9318 encoder provides a binary representation on the active low outputs A0, A1, and A2 (A0 is the LSB). At the same time, the 9318 active high output, EO, goes high, clocking flip-flop E4. If the computer is stopped (power is on but timing has not been initiated), the RUN L signal is high and the D input of E4 is high. Thus, E4 is set and the E4 (1) signal is asserted (if the front panel OFF/POWER/PANEL LOCK switch is in the PANEL LOCK position, the – 15V supply voltage is removed from the panel lock tab, and NAND gate E8 cannot be enabled; this effectively disables the operating keys and switches and prevents manual operation of the switch register). The E4 (1) signal triggers 1-shot E18A; 1500 ns later the 500 ns enable gate is generated when E18B is triggered.

Figure 3-82 Operating Keys, Enable Signal Logic

The table in Figure 3-82 relates the keys and the 9318 inputs and outputs. The table reflects the dominant feature of the 9318 priority encoder, viz., if two or more inputs are simultaneously active, the input with the highest priority is represented by the binary output. Input 7 is assigned highest priority; thus, the ADDR LOAD key takes precedence over all other keys. If the operator depresses the ADDR LOAD key, for example, the 9318 IC asserts the A0 L, A1 L, A2 L, and EO signals. Until this key is released, no other key can affect the enable signals. When the key is released, the 74175 CLR input is returned to ground, clearing the flip-flop that was set by the ADDR LOAD key. Now, the flip-flop associated with a key of lower priority causes the 9318 output to change. Note that flip-flop E4 is also cleared when a key is released. Thus, the enable signals and, as a result, the control signals are asserted only as long as the operator depresses a key. Manual operation with the KC8-FL is, therefore, as fast as the operator can make it.

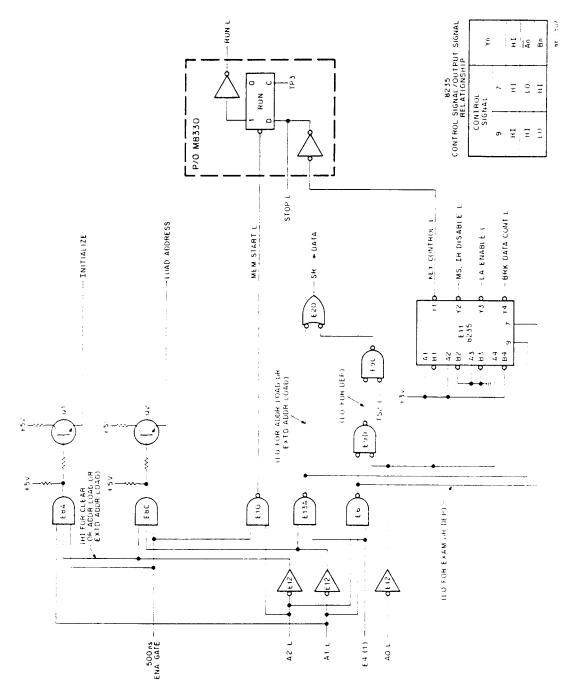

The logic used to generate the control signals is shown in Figure 3-83. The gating of the logic in response to the enable signals is not discussed; this task is left to the reader. Table 3-4, which will facilitate this task, relates the control signals, the enable signals, and the keys. The state of each of the control inputs of the 8235 IC is also tabulated. A functional description of each of the keys follows. Refer to the flow diagram, the logic diagrams, and the tables while reading the functional descriptions.

ADDR LOAD Key and EXTD ADDR LOAD Key – The ADDR LOAD key is used to load the CPMA Register with the memory address specified by the switch register. When the operator depresses this key, switch register information is placed on the DATA 0–11 lines. At the same time, LA ENABLE L and MS, IR DISABLE L are asserted. These two control signals enable a path for the DATA lines through the adder network to the MAJOR REGISTERS BUS. The LOAD ADDRESS signal is then asserted. This signal produces the CPMA LOAD L pulse, which loads the CPMA Register with the information on the DATA 0–11 lines. The memory location specified by the CPMA Register can now be operated on by the DEP key or the EXAM key.

Note that the ADDR LOAD key does not initiate a timing cycle. The purpose of this key is to establish a memory location at which some operation will take place. If a timing cycle were to be initiated, the CPMA address would be incremented, and the operation would take place at the desired address, plus 1. Therefore, to avoid confusion, ADDR LOAD does not initiate a timing cycle.

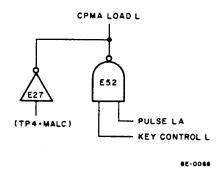

The EXTD ADDR LOAD key, likewise, does not initiate a timing cycle. This key is used to load switch register bits 6–11 into the Instruction Field (IF) and Data Field (DF) Registers of the KM8-E Memory Extension and Time Share option (bits 0–5 of the switch register are used for IOT designation and device selection code). When the operator depresses the EXTD ADDR LOAD key, the switch register information is placed on the DATA 0–11 lines. The LA ENABLE L and KEY CONTROL L signals are asserted, providing a path to the KM8-E option for the DATA 6–11 lines. The LOAD ADDRESS signal is then asserted and the DF and IF Registers are loaded with the extended address information. The address specified by the CPMA Register and the DF and IF Registers can now be operated on by other keys.

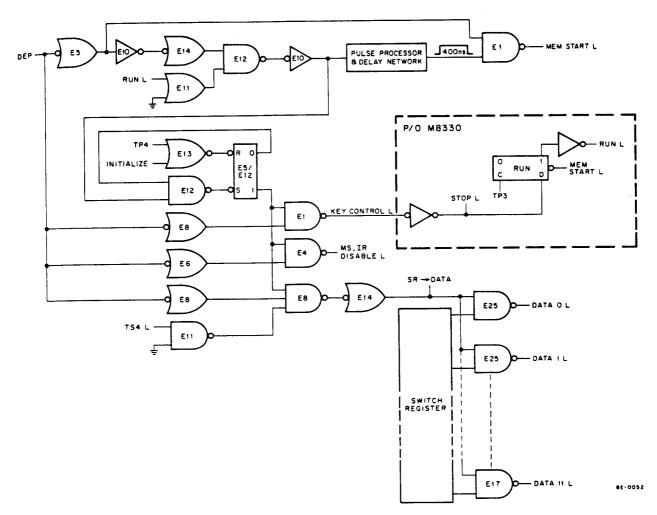

DEP Key – The DEP key is used to deposit the data represented by the switch register in a specified memory location. When the DEP key is lifted, two control signals, MS, IR DISABLE L and KEY CONTROL L, are asserted. KEY CONTROL L selects the MA lines for gating into one leg of the adder network, while MS, IR DISABLE L provides an arithmetic 0 at the other adder input. KEY CONTROL L also asserts a processor signal that increments the CPMA Register. 1500 ns later, the MEM START L signal is asserted, the RUN flip-flop is set, and a timing cycle begins. At TP1 time the PC Register is loaded with the next consecutive memory address (note that the nonincremented address remains in the CPMA Register until TP4 time of the cycle).

the state of the

|                   | ENABLE Signals |     |      |        |                    | E11 |    |                                                                             |  |

|-------------------|----------------|-----|------|--------|--------------------|-----|----|-----------------------------------------------------------------------------|--|

| Key               | A0 L           | A1L | A2 L | E4 (1) | 500 ns<br>ENA Gate | 9   | 7  | CONTROL Signals                                                             |  |

| ADDR LOAD         | LO             | LO  | LO   | ні     | н                  | LO  | н  | LOAD ADDRESS, SR → DATA,<br>MS, IR DISABLE L, LA ENABLE L                   |  |

| EXTD ADDR<br>LOAD | ні             | LO  | LO   | HI     | HI                 | LO  | н  | LOAD ADDRESS, SR → DATA,<br>MS, IR DISABLE L, LA ENABLE<br>L, KEY CONTROL L |  |

| CLEAR             | н              | н   | LO   | ні     | ні                 | ні  | н  | INITIALIZE                                                                  |  |

| CONT              | ні             | LO  | ні   | ні     | ні                 | н   | н  | MEM START L                                                                 |  |

| EXAM              | LO             | ні  | ні   | ні     | н                  | н   | LO | MEM START L, KEY CONTROL L,<br>MS, IR DISABLE L, BRK DATA<br>CONT L         |  |

| DEP               | н              | н   | н    | ні     | ні                 | н   | LO | MEM START L, KEY CONTROL L,<br>MS, IR DISABLE L, SR → DATA                  |  |

Table 3-4 KC8-FL CONTROL/ENABLE Signals

During TS2 of the timing cycle, the switch register data is gated onto the DATA 0-11 lines and the adder control signals enable a path through the adder network, adding an arithmetic 0 to each DATA bit. The switch register information is placed on the MAJOR REGISTERS BUS and loaded into the MB Register at TP2 time. At the same time, the MD DIR L signal is negated causing the content of the MB Register to be placed on the MD 0-11 lines. The data is then read into the memory location specified by the content of the CPMA Register.

At TP3 time the RUN flip-flop is reset (the STOP L signal is asserted when KEY CONTROL L is generated). The timing continues through TS4 and TP4 to halt in TS1 of some as yet unspecified cycle. Before the cycle is completed, one other operation is performed. The next consecutive address must be transferred from the PC Register to the CPMA Register. Therefore, the information in the PC Register is gated to one leg of the adder, and a 0 is added to each bit; the new address is placed on the MAJOR REGISTERS BUS and loaded into the CPMA Register at TP4 time. The cycle then ends.

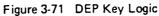

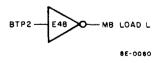

EXAM Key – The EXAM key also initiates a timing cycle. By depressing this key the operator causes the content of a selected memory location to be brought from memory and loaded into the MB Register. Except for the absence of the SR  $\rightarrow$  DATA signal, the TS1 operations are the same for the EXAM key as for the DEP key. The MS, IR DISABLE L, KEY CONTROL L, and MEM START L signals are asserted and function as described. However, the EXAM key also causes the BRK DATA CONT L signal to be asserted; this signal causes the TS2 operations to differ from those of the DEP key.

The BRK DATA CONT L signal gates the MD lines to the adder network, where a 0 is added to the data being brought from the memory location. The MD bits are placed on the MAJOR REGISTERS BUS and loaded into the MB Register at TP2 time (at the same time, the MD DIR L signal is negated, causing the register content to be again placed on the MD lines; thus, the content of the memory location can be re-written during the write half of the timing cycle). The operator can view the content of the MB Register by selecting the MD position on the front panel function selector switch. The operator can modify the data in the examined location by using the switch register and the DEP key. However, the EXAM cycle increments the PC Register to set up the next sequential memory address; therefore, to modify the data in the examined location, the switch register and ADDR LOAD key must be used to get back to the correct address.

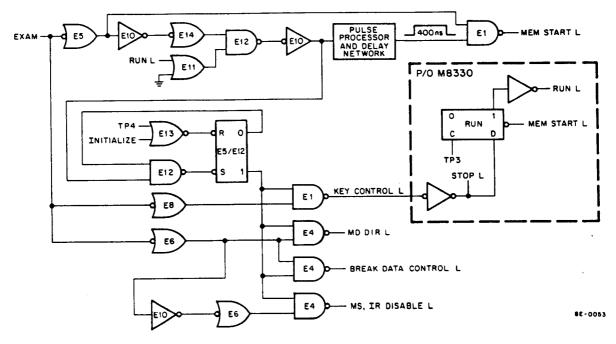

CONT Key – The CONT key initiates a timing cycle by causing the MEM START L signal to be asserted. This is an important function because this is the *only* key that initiates repetitive timing cycles. Thus, the operator can begin automatic operation only by depressing the CONT key.

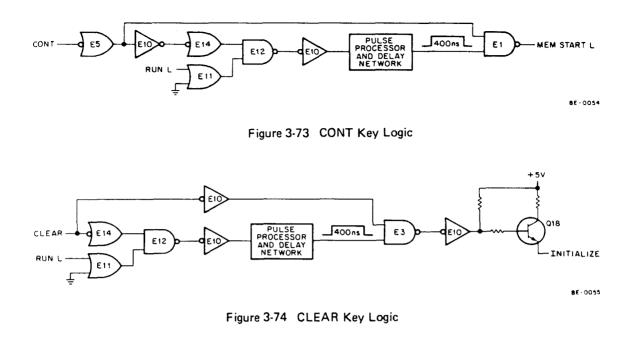

*CLEAR Key* – The CLEAR key generates the INITIALIZE signal. This signal clears the AC Register, the LINK, the Interrupt system, all peripheral flags, and various flip-flops within the basic system.

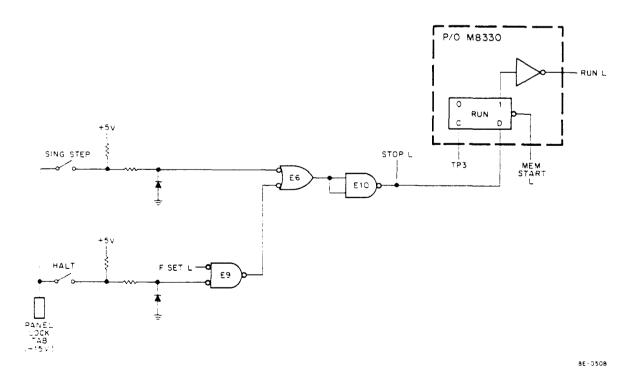

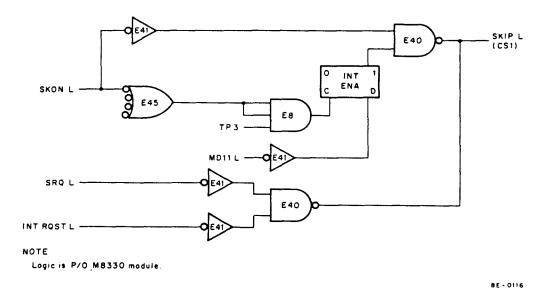

SING STEP Switch and HALT Switch – The operator can stop the PDP-8/E by closing either the SING STEP or the HALT switch. The logic is shown in Figure 3-84. If the SING STEP switch is used, the STOP L signal is generated and the first TP3 pulse clears the RUN flip-flop. The RUN L signal is negated, and the machine stops at the beginning of the next TS1 period. If the HALT switch is used, the STOP L signal is generated only when the F SET L signal is asserted. Because F SET L is asserted only when the next timing cycle is to be a FETCH cycle, the processor completes an entire instruction before halting in TS1. The operator can use these two switches and the CONT key to step a program one cycle or one instruction at a time.

Figure 3-84 SING STEP and HALT Switches

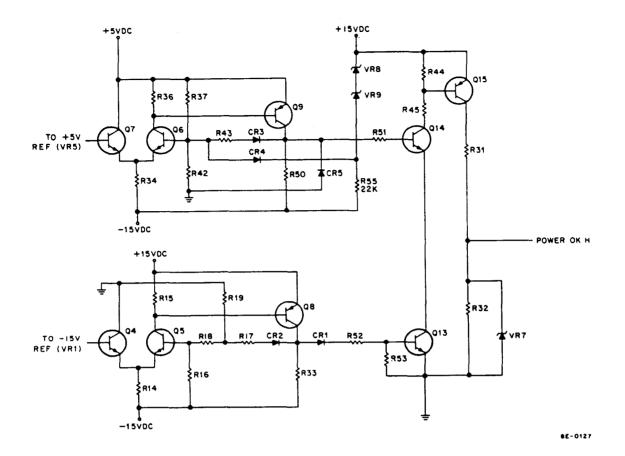

3.33.2.2 Display – The KC8-FL Programmer's Console uses solid-state devices rather than filament-type lamps to indicate the state of various PDP-8/F (PDP-8/M) major registers and OMNIBUS signals. These indicators, light-emitting diodes (LEDs), are more durable than lamps and help to promote maintenance-free operation. LEDs differ from incandescent lamps in another important way. As the name implies, LEDs are diodes. Consequently, they exhibit the usual nearly constant forward voltage when conducting. A series resistor to define the forward current through the diode is necessary. In the KC8-FL, the resistor value of  $330\Omega$  establishes the LED on-current at about 10 mA. At currents of less than  $500 \mu$ A, the diode does not emit detectable amounts of light.

A single indicator, designated RUN, emits light when timing cycles are being generated. The light from this and all other indicators, is visible on the front panel (Figure 1-1). The other indicators are divided into two groups. One group, comprising 15 LEDs, displays the current memory address. This group is represented by the designations MEMORY ADDRESS and EMA. The other group, comprising 12 LEDs, displays the contents of selected registers and important OMNIBUS signals. A front panel switch enables the operator to select the register or type of OMNIBUS signal that he wishes displayed.

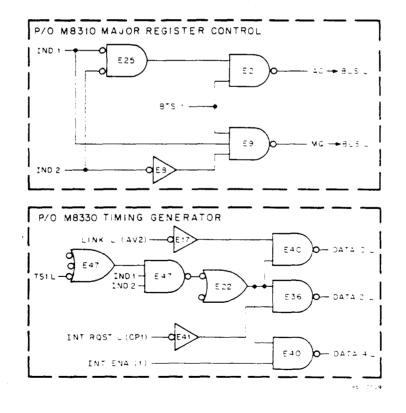

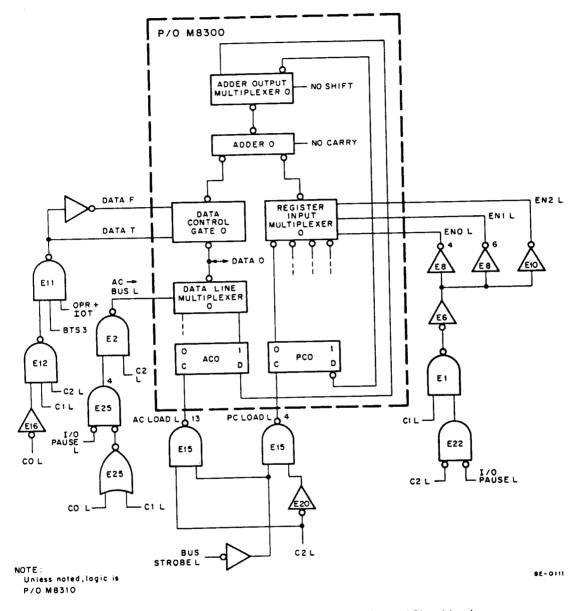

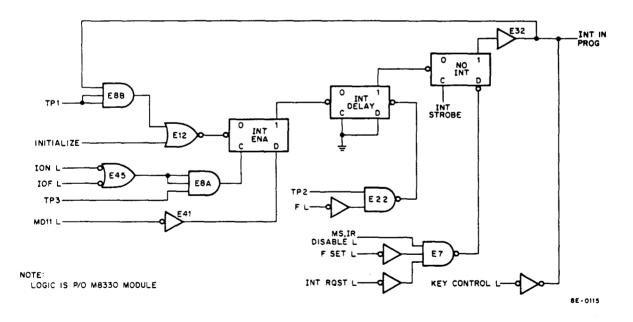

The display logic is represented in Figure 3-85. The RUN indicator is shown in the lower right of the figure. When the timing generator logic (M8330) asserts the RUN L signal, LED D35 emits light, indicating that the computer is running (power is on and timing cycles are being generated).

The two groups of indicators are represented by the 0 bit logic. For example, a complete 15-bit memory address has two 0 bits, EMA0 and MA0. Both bits are shown in the logic. When either the EMA0 L signal or the MA0 L signal is asserted, the +V voltage appears across the corresponding LED and its current determining resistor, causing it to light. The +V voltage, approximately +4.5V, is taken from the circuit that includes Q3 and Q4. When the front panel OFF/POWER/PANEL LOCK switch is in the PANEL LOCK position, the -15V supply is removed from the panel lock tab, thereby removing the +V voltage. Consequently, only the RUN indicator is lit with the switch in this position.

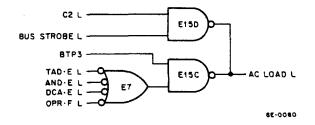

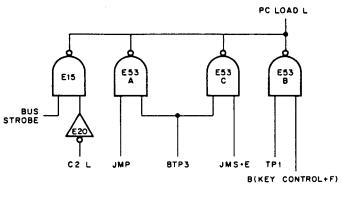

The majority of the logic in Figure 3-85 is used with the group of indicators that displays OMNIBUS signals and major register contents. Again, only the 0 bit logic is represented. The type of information displayed is selected on the front panel by a 6-position rotary switch, labeled S1 in Figure 3-85. This switch causes one of three signals to be asserted, depending on its position: in the MD position, MD IND is asserted; in the STATE position, STATE IND is asserted; in all other positions, DATA IND is asserted.

If the operator wants to monitor the MD lines, he switches to the MD position, causing the MD IND signal to be asserted. This signal is ANDed with the MD0 L signal in AND/NOR gate E15. The three other AND gates of E15 are disabled when S1 is in the MD position. If the MD0 L signal is asserted, E15 is disabled. Therefore, the output of inverter E22 is low. The +V voltage appears across LED D23, causing it to emit light that is visible on the front panel. The same analysis can be repeated for the F L signal when S1 is in the STATE position. However, the logic gating is more complicated when any of the other four switch positions is selected. The reason for this is that the four different types of signals must be carried on only the DATA lines; furthermore, remember that the DATA lines are time-shared and display information has access to these lines only during TS1.

Figure 3:85 Display Logic

Assume that the operator positions S1 at AC. The DATA IND signal is asserted during TS1. The AC0 bit must be gated to the DATA 0 line so that its state can be displayed. The table in Figure 3-85 shows that when the AC position is selected, the 8235 IC takes both IND1 and IND2 low. This combination of IND1 and IND2 causes the logic within the broken line (the actual logic is shown in Figure 3-86) to assert the AC  $\rightarrow$  BUS L signal. Thus, the AC0 bit is gated to the DATA 0 line. If the AC0 bit is logic 1, AND gate A of E15 is disabled, the output of E15 stays high, and D23 emits light.

If the AC0 bit is logic 0, the LATCH flip-flop performs an important function. To illustrate, assume that the operator, while stepping the computer through a series of timing cycles (with the SINGLE STEP switch closed), causes a TAD instruction to be executed. The computer stops in TS1 of the cycle following the TAD instruction. The operator wants to check the result and switches to the AC position. D23 indicates logic 0. When the CONT key is depressed, AND gate A of E15 is disabled as soon as TS2 of the new timing cycle is entered. Therefore, if AND gate B and the LATCH flip-flop were not present, D23 would emit light for most of the timing cycle following the TAD execute cycle. Instead, the LATCH flip-flop is set at TP1 time (the D-input is high when the AC position is selected). The 1 output of the flip-flop and the high at the output of E22 keep E15 enabled; D23 remains dark throughout the timing cycle. At TP1 time the LATCH flip-flop is cleared.

Similarly, the content of the MQ Register, STATUS information, and BUS data can be displayed. The relationship between IND1/IND2 and the type of information displayed is indicated on Figure 3-85. Figure 3-86 shows the logic used to generate control signals in response to IND1 and IND2.

Figure 3-86 Data Bus Display Control Signals

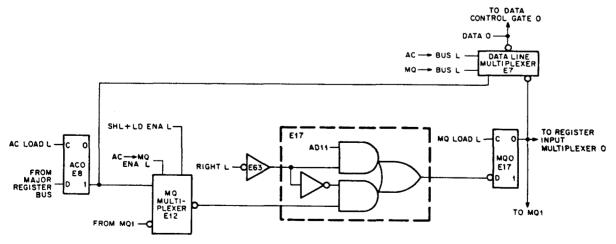

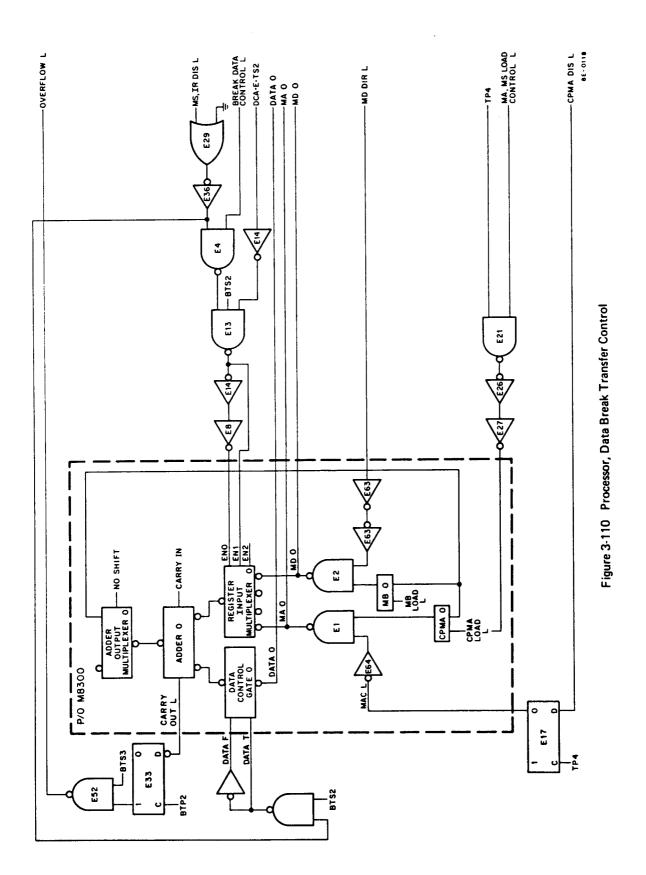

## 3.34 MAJOR REGISTER GATING, BLOCK DIAGRAM DESCRIPTION

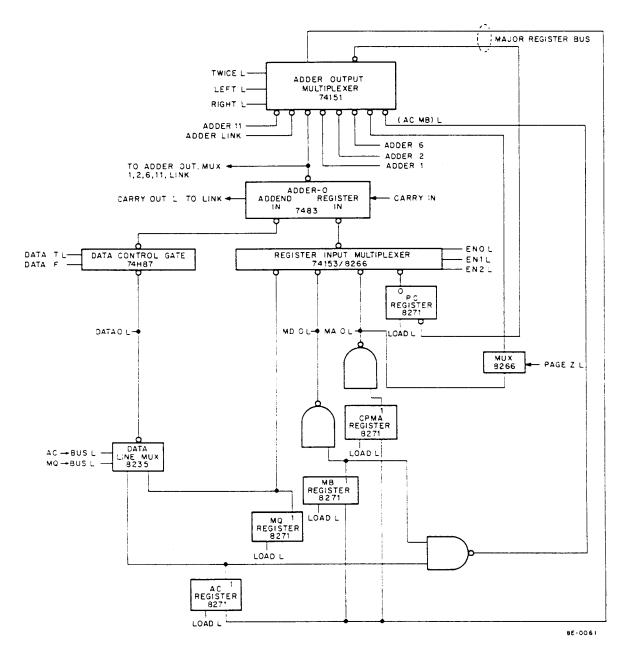

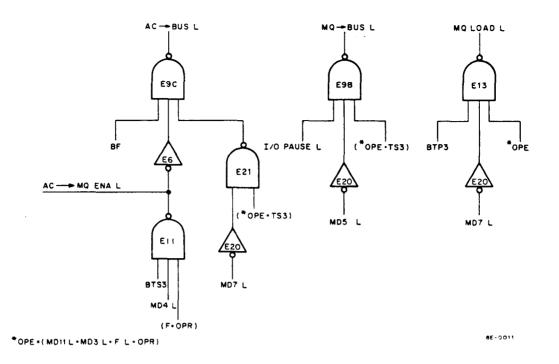

The major registers of the PDP-8/E perform all the operations required to implement program instructions. In retrospect, the PC Register keeps track of the program steps, the CPMA Register selects the memory location provided by the PC, and the AC Register uses the data in the selected memory location to carry out arithmetic operations. Information of one type or another (data, addresses, etc.) is continuously exchanged by the major registers. To effect these exchanges, the major register gating network is required. The major registers and the gating network are illustrated in the block diagram of Figure 3-87. This diagram presents the register flip-flops and the gating for one bit, bit 0, of the PDP-8/E 12-bit data word. All 12 data bits have similar gating networks; when differences exist, they will be noted in the discussion.

Figure 3-87 Major Registers and Gating, Block Diagram

Each major register is loaded with data that is transferred to the 0 bit flip-flop by the MAJOR REGISTERS BUS. The source of the data on this bus is the adder network. This network consists of the adder itself, a Register Input Multiplexer, an Adder Output Multiplexer, and a Data Control Gate which supplies an addend to the adder. The Register Input Multiplexer gates the output from a selected register flip-flop to the "register in" line of the adder. The data to be added to the 0 bit of this register is supplied by the Data Control Gate. The sum for the adder is transferred to the MAJOR REGISTERS BUS by the Output Multiplexer. A timing pulse then provides a load signal, which clocks the data into the desired register.

Note that the Adder Output Multiplexer can select any one of eight inputs for transfer to the register bus. Consider only the adder 0 input. Bit 0 of any register can be transferred to bit 0 of any other register. This is the case when the memory address in the PC Register is transferred to the CPMA Register at the completion of an instruction (PC  $\rightarrow$  CPMA). Bit 0 of the PC is gated by the Register Input Multiplexer to the adder "register in" line. Because the bit must be transferred unaltered, an arithmetic 0 is supplied at the "addend in" line by the DATA T/DATA F control signals. The Adder Output Multiplexer places the unaltered bit on the MAJOR REGISTERS BUS; a load signal clocks the data into the 0 bit of the CPMA Register.

A similar operation takes place when the 0 bit is modified before transfer. For example, during an IOT instruction a peripheral can effect a relative jump of the program count (DATA + PC  $\rightarrow$  PC). In this case, the "addend in" line must represent the state of the DATA 0 line and can be either a 0 or a 1. The sum of DATA 0 and PC0 is transferred to the MAJOR REGISTERS BUS; a load signal clocks the data into the 0 bit flip-flop of the PC.

If the Adder Output Multiplexer control signals (TWICE L, LEFT L, RIGHT L) select the "adder 1" input for transfer to the 0 bit MAJOR REGISTERS BUS, the RAL microinstruction (rotate AC and LINK left one place) is being implemented. Bit 1 of the AC Register is transferred to bit 0 of the AC Register (at the same time, AC bit 0 is transferred to the LINK). AC transfers are accomplished differently from the transfers of the other major registers. AC bit 0 is gated onto the DATA 0 L line by an AC  $\rightarrow$  BUS signal, and through the data control gate to the adder. In this case, the Register Input Multiplexer provides an arithmetic 0 at the "register in" line. Bit 0 is then gated through the Adder Output Multiplexer that is associated with the LINK. Simultaneously, the output from adder 1 is gated onto the 0 bit MAJOR REGISTERS BUS. The AC LOAD L signal then clocks the data into the 0 bit of the AC Register.

Similarly, AC bits 11, 2, and 6, and the LINK bit can be transferred into bit 0 of the AC. The microinstructions implemented by those transfers are RTR, RTL, BSW, and RAR, respectively.

In addition to adder outputs, the Adder Output Multiplexer can gate two other signals onto the MAJOR REGISTERS BUS. One of these signals is (AC·MB) L, which is active when both MDO L and ACO L are at a positive voltage level (logic 1). When the basic AND instruction is implemented, the signal is gated through the Adder Output Multiplexer by the control signals. The logic 1 or 0 represented by the signal is then clocked into ACO.

The other signal that can be gated by the multiplexer is encountered during implementation of a Memory Reference Instruction (MRI). As the block diagram shows, this input is taken from a multiplexer that is controlled by the PAGE Z L signal. If the page address of the operand of the MRI is the same as that of the MRI, itself, the multiplexer output reflects the state of the MAO line; however, if the operand is located on the O page, the multiplexer output is an arithmetic O. In either case, the page data is placed on the MAJOR REGISTERS

BUS and loaded into CPMAO. This gating procedure only applies to register bits 0 through 4. If register bits 5 through 11 are considered, only a relative address must be considered. Therefore, the input to the Adder Output Multiplexer is taken directly from the appropriate MD line, rather than from the MA line via the PAGE Z multiplexer. A further discussion is presented when the logic diagrams are considered in detail.

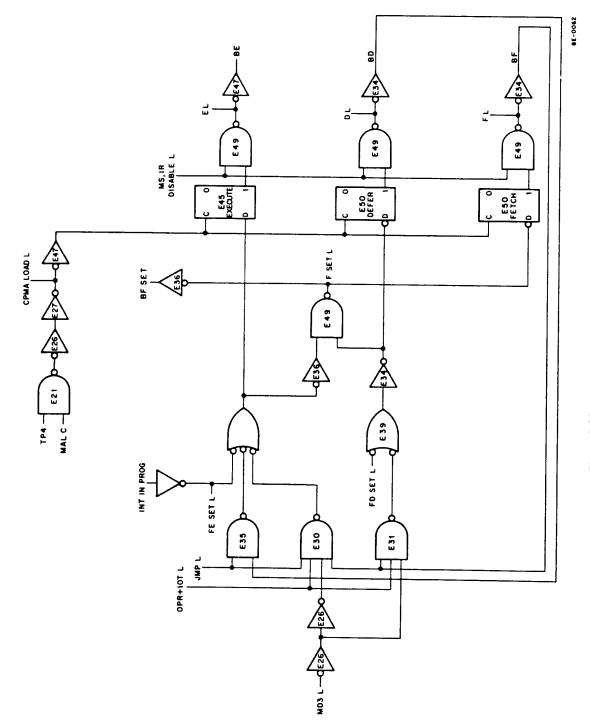

## 3.34.1 Major State Register

PDP-8/E operations are grouped functionally into the four major states already introduced. FETCH (F), DEFER (D), and EXECUTE (E) are entered actively by setting flip-flop in the Major State Register. The fourth state, Direct Memory Access (DMA), results when none of the other three has been entered.

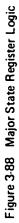

The Major State Register logic is shown in Figure 3-88. Flip-flops E45 and E50 are used to generate the F, D, and E states. The outputs of E45 and E50 are NANDed with a control signal called MS, IR DISABLE L. When this signal is negated (at +3V), one of the NAND gates (only one major state flip-flop may be active at any given time) is enabled; either F, D, or E is asserted. On the other hand, if MS, IR DISABLE L is asserted, none of these three states is entered. Thus, the computer is in the Direct Memory Access (DMA) state. This state is entered when data is to be transferred between memory and a data break peripheral, or between memory and the front panel. In either case, this state bypasses the processor logic that is normally used to access memory.

The major state flip-flops, E45 and E50, are clocked by the inverted CPMA LOAD L signal. This signal is produced when the front panel LOAD key is depressed during manual operation. In addition, the signal is generated by each TP4 pulse during automatic operation. Some type of manual operation always precedes automatic operation; for example, to initiate automatic operation of a stored program, the operator must load the CPMA with the starting address of the program. This address is loaded by depressing the LOAD key, an action that produces the CPMA LOAD pulse. However, this action also produces MS, IR DISABLE L. In fact, MS, IR DISABLE L is produced some 20 ms before CPMA LOAD. MS, IR DISABLE L causes the logic to generate a control signal, F SET L, which is applied to the data (D) input of the FETCH state flip-flop. Thus, when CPMA LOAD is produced, it clocks the flip-flop to its reset state, and the next cycle of operation will be a FETCH state. If the operator now depresses the CONT key, the computer begins the FETCH operation specified by the instruction just addressed.

The F SET L signal is asserted when computer operation requires that the FETCH state be entered. As previously indicated, FETCH is always entered on completion of manual operation. FETCH can also be entered on completion of a data break operation. Both manual and data break operations take place in the DMA state. Entry to and exit from this state is discussed fully in a following paragraph; a third method of entering the FETCH state is discussed in the following paragraph.

All instructions start in the FETCH state; consequently, this state can be entered from any state that completes an instruction. FETCH is entered from the EXECUTE state at the completion of a two- or three-cycle instruction; FETCH is entered from the DEFER state at the completion of a two-cycle instruction; finally, FETCH is entered from FETCH, itself, at the completion of a one-cycle instruction.

Figure 3-88 shows that F SET L is asserted when both inputs to NAND gate E49 are logic 0 (positive voltage level). Note that this condition arises only if NAND gates E30, E31, and E35 are disabled (ignore FE SET L and FD SET L for this discussion). If the computer is entering the EXECUTE state of a two- or three-cycle instruction, E is asserted at pin 4 of NAND gate E49, while both BD and BF are negated. E30, E31 and E35 are disabled, and CPMA LOAD L (produced by TP4) sets the FETCH flip-flop. If the computer is in the DEFER state of a two-cycle instruction, BF is negated, and E30 and E31 are disabled. E35 is likewise disabled in this

:ase, because a two-cycle instruction involving the DEFER state can only be a JMP instruction. Therefore, the IMP line is asserted low and, again, all three NAND gates are disabled. Finally, if the computer is performing a pne-cycle instruction (a FETCH state), BD is negated, thereby disabling E35. A one-cycle instruction can be an PPR microinstruction, an IOT instruction, or a directly addressed JMP instruction. If the instruction is either of the first two, the OPR + IOT line is grounded to disable gates E30 and E31. However, if the instruction is a directly addressed JMP, the JMP line is grounded to disable E30, while the negated MD3 L signal disables E31.

When the FETCH state of a multicycle instruction has been completed, either a DEFER or EXECUTE state follows, unless the operator depresses the SING STEP key or a data break device causes suspension of program control. Either circumstance can cause a halt or interruption when the FETCH state is completed; then the DMA state is entered. When the operations in this state have been carried out, control is returned to the program, and the multicycle instruction can be completed.

Consider, at this time, normal operation under program control, and assume that the instruction being processed s either a two-cycle instruction involving the DEFER state, or a three-cycle instruction. Operations are being carried out in the FETCH state. The DEFER state is the next state to be entered. The data line of the DEFER flip-flop must be asserted low, if the flip-flop is to be set at TP4 of FETCH; thus, NAND gate E35 must be enabled (again, disregard FD SET L). Because the FETCH state of a multicycle instruction is being performed, 3F is high and OPR + IOT L is high. The DEFER state is entered when indirect addressing is required by the memory location of the operand. Such addressing is indicated when MD3 L is asserted, thereby providing the third high level for NAND gate E31. TP4 sets the DEFER flip-flop, and operations are then carried out in the DEFER state.

If the instruction is complete at the end of the DEFER state, the FETCH state is entered; however, a three-cycle instruction requires that EXECUTE be entered after DEFER. This requirement is met if NAND gate E35 is enabled. With BD asserted high and JMP negated (some instruction other than JMP is being performed and FE SET L is disregarded), E35 is enabled and TP4 sets the EXECUTE flip-flop. When EXECUTE is complete, the FETCH state is again entered. If the multicycle instruction being carried out does not require indirect addressing, the computer goes directly from FETCH to EXECUTE; in this event, NAND gate E30 is enabled, because MD3 L is negated high.

The preceding discussion disregarded the signals FD SET L and FE SET L. These signals are asserted by the EAE option; their functions are discussed in Volume 2 of this manual. However, note that the INT IN PROG L signal also can assert the FE SET line. The INT IN PROG L signal is asserted high when an interrupt request is honored by the interrupt logic of the timing generator module. The data line of the EXECUTE state flip-flop is then high, and TP4 forces the EXECUTE state to be entered next. FE SET can be asserted in this manner during either a FETCH, DEFER, or EXECUTE state, provided that the particular state is the final state of an instruction.

FETCH can be entered from the DMA state. The DMA state is used during manual operation and for data breaks. This state is entered when the MS, IR DISABLE L line is asserted. If this line is asserted because manual operations are being performed, the FETCH state always follows the DMA state. MS, IR DISABLE L disables NAND gates E49, thereby asserting F SET L (Figure 3-88). If the EXAM or DEP key has been depressed, TP4 and MA, MS LOAD CONT L (the latter is negated during manual operations) produce CPMA LOAD L. If the LOAD key has been depressed, PULSE LA H produces CPMA LOAD L. In either case, the FETCH flip-flop is reset and automatic operation begins in the FETCH state.

If MS, IR DISABLE L has been asserted by a data break peripheral, the FETCH state may or may not follow the DMA state. A data break operation can begin at the end of any major state. Program control is halted for one timing cycle (control may be halted for three cycles, as well; for convenience, a halt of one cycle is considered). When the data transfer has been completed, program control is re-established and the previously interrupted operation continues. An example of the interrupting processor is given in the following paragraph.

If operations are being carried out in the FETCH state of a two-cycle DCA instruction, the data line of the EXECUTE flip-flop is at a positive voltage level. If a peripheral initiates a data break during this FETCH state, MS, IR DISABLE L is asserted at TP4. At the same time, CPMA LOAD L is produced by TP4 and MA, MS LOAD CONT L and the EXECUTE flip-flop is set, but E, at the output of E49, remains negated. The DMA state is entered, instead of the EXECUTE state, and data transfer begins. Because the E49 NAND gates are disabled, F SET L is asserted. It could be assumed that the next TP4 pulse (of the DMA state) would reset the FETCH flip-flop; however, at TP1 of the DMA state the peripheral asserts MA, MS LOAD CONT L, thereby preventing the TP4 pulse in question from resetting the FETCH flip-flop. Instead, this TP4 negates MS, IR DISABLE L. The EXECUTE flip-flop is still set and, thus, E is asserted. Operations begin in the EXECUTE state of the interrupted instruction. At TP1 of this state, MA, MS LOAD CONT L is negated, completing the return to uninterrupted operation.

Consequently, because a data break can occur at the end of any major state, either FETCH, DEFER, or EXECUTE can be entered directly from the DMA state. The following section describes how the DMA state is used to suspend operation of the Instruction Register and decoder network during a data break operation.

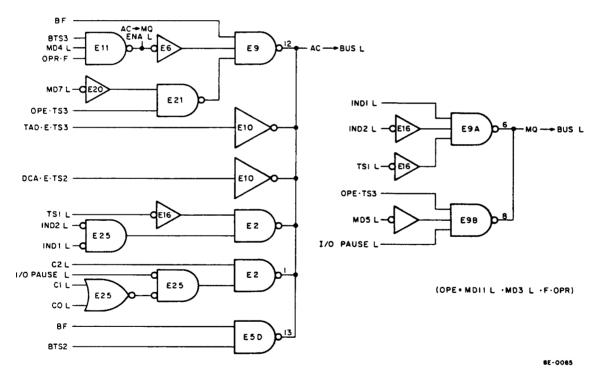

# 3.34.2 Instruction Register

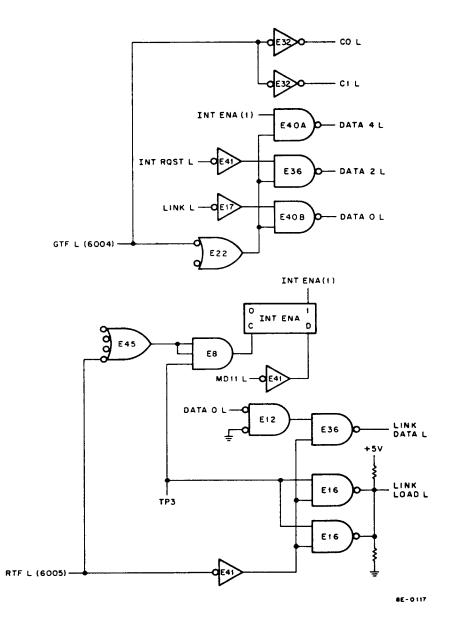

Operations within each major state are determined by the type of instruction that is contained in the addressed memory location. This instruction is placed on the MD lines, near the beginning of a FETCH cycle. MD bits 0, 1, and 2 are decoded by a network consisting, primarily, of an Instruction Register (IR) and a decoder IC. The decoder IC provides an output in response to the octal number represented by IR0 L, IR1 L, and IR2 L (MD0 L, MD1 L, and MD2 L, respectively). For example, the TAD instruction is represented as 1000 octal. Therefore, MD bits 0, 1, and 2 are 0, 0, and 1, respectively. The decimal 1 line is asserted by the decoder, causing TAD operations to begin. Other basic operations are initiated in the same manner. For a detailed presentation of the decoder integrated circuit, see Appendix A.

The decoding network, referred to as the IR decoder, is shown in Figure 3-89. Each of the IR decoder flip-flops, E40 and E45, is clocked by TP2 of the FETCH state. When the data (D) input of a flip-flop is grounded, indicating a logic 1 on the MD line in question, TP2 resets the flip-flop. When a flip-flop is reset, its corresponding IR line (0, 1, or 2) is asserted (grounded), provided that the MS, IR DISABLE L signal is negated. The eight possible combinations of the IR lines are decoded by the decoder module to produce one of the eight basic instructions shown.

If MS, IR DISABLE L is asserted (grounded), it removes the IR flip-flop outputs from the IRO L, IR1 L, and IR2 L lines (it also causes the decoder to assert the AND L line; however, MS, IR DISABLE L forces the processor into the DMA state, and the basic instructions are not implemented during this major state). When MS, IR DISABLE L is negated, the IR lines return to their former state, and the interrupted instruction is again asserted.

Figure 3-89 IR Decoder Logic

Note that flip-flop E40B can be dc-set and flip-flops E40A and E45 can be dc-cleared by a negative transition at the output of NAND gate E35. This transition occurs at TP4 time, if the INT IN PROG H signal has been asserted. This action forces the IR to 4 (JMS) and causes the decoder to assert the JMS line. Remember that INT IN PROG H also enables the data input of the EXECUTE flip-flop; thus, TP4 also sets the EXECUTE flip-flop. The processor enters the EXECUTE state and performs the JMS instruction, storing the program count in memory location 0, and entering the interrupt servicing routine. When the subroutine has been completed, the main program is resumed at the program count specified by memory location 0.

A data break device can request a break by asserting MS, IR DISABLE L at the same time (TP4) the IR flip-flops are dc-clocked to the JMS state. In this case, the data break device assumes control, and the processor enters the DMA state. On completion of the data break, the processor enters the EXECUTE state, performs the JMS instruction, and services the interrupting device, as outlined.

## 3.35 SOURCE CONTROL SIGNALS

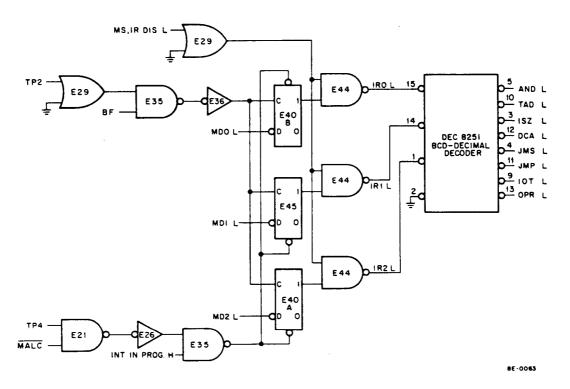

## 3.35.1 Register In Enable Signals

The ENO L, EN1 L, and EN2 L control signals are used to gate the 12 bits of the desired major register to the adder "register in" lines. Table 3-5 lists the usable combinations of these signals (in terms of voltage levels) and the register selected by each combination. The last entry of Table 3-5, which has ENO L as a positive voltage level, gates an arithmetic 0 to the register in line. This condition occurs during TS3, when an OPR microinstruction or an IOT instruction is being carried out by the processor; in addition, a data break peripheral can cause such a condition to occur during TS2 of the DMA state.

| ENOL | EN1 L | EN2 L | Input to Adder Register In Line                     |  |

|------|-------|-------|-----------------------------------------------------|--|

| Low  | Low   | Low   | PC Register                                         |  |

| Low  | Low   | High  | MD Lines                                            |  |

| Low  | High  | Low   | MQ Register<br>(can be effected only by EAE option) |  |

| Low  | High  | High  | CPMA Register                                       |  |

| High | x     | x     | Arithmetic Zero                                     |  |

# Table 3-5 Register In Enable Signals

The logic gates used to generate the EN control signals are shown in Figure 3-90. To better understand processor operation, consider the logic diagrams as a means for understanding why a particular register is brought into the adder. For example, when all three signals are at a 0V level, the PC Register is gated to the adder. The processor flow diagram shows that the PC is transferred to the CPMA during TS4 of every major state. Thus, signals involved with TS4 should be examined.

The TS4 signal is the signal most likely to be used in gating the PC. This signal is applied to three separate NAND gates, E1A, E1B, and E3B. However, only E1B or E3B can, alone, cause all three EN signals to go to a ground level. E3B uses KEY CONTROL L as an enabling signal; KEY CONTROL L is asserted by the EXAM and DEP keys, both of which initiate a timing cycle. Thus, E3B produces the signals that gate the PC to the adder, thereby establishing a path from the PC to the CPMA during manual operation. E1B performs a NAND operation with two signals. One signal is a composite consisting of TS4, F SET L, and MS, IR DISABLE L. The F SET L signal indicates that the instruction is c<sup>o</sup>mplete; MS, IR DISABLE L ensures that the current cycle is not a DMA state caused by a data break (if this is the case, the interrupted instruction may not have been completed prior to the data break; consequently, the PC must not be transferred to the CPMA). The other signal NANDed in E1B is (FE+FD) L. This signal is asserted either by the KE8-E option (operation in this circumstance is discussed in Volume 2), or by the INT IN PROG L signal. In the event that (FE+FD) L is negated, E1B produces the signals that establish a path from the PC to the CPMA during automatic operation.

If (FE+FD) L is asserted by INT IN PROG L, the PC is not transferred to the CPMA. Rather, the 0 location is loaded into the CPMA, and the processor goes into the EXECUTE state to carry out the JMS operation. During TS4 of this EXECUTE state, the PC is transferred to the CPMA.

In the process of carrying out the above JMS instruction, the processor must deposit the program count in location 0 (the PC must be transferred to the MB). Thus, the PC is gated to the adder. Inverter E8D causes the EN signals to be asserted during TS2 of the EXECUTE state of a JMS instruction. TS2 ensures that the PC data is on the MAJOR REGISTERS BUS before MB LOAD L is generated at TP2 time.

Figure 3-90 Register In Enable Logic

One remaining operation calls for the PC to be gated to the adder. A peripheral, through an IOT instruction, can change the program count in the PC Register by causing DATA+PC to the PC. NAND gates E22 and E1D assert the EN signals for this purpose. Further discussion of the C0 L, C1 L, C2 L, and I/O PAUSE L signal is presented in Section 6, I/O Transfer Logic.

If only EN0 is asserted, the CPMA Register is gated to the adder network (Table 3-5). As the logic indicates (Figure 3-90), the only way the processor can assert EN0, alone, is by enabling the wired-NOR consisting of NAND gate E3D and inverter E27. The signals used by this wired-NOR for gating the CPMA to the adder are described in the following paragraphs.

E3D is enabled during TS1 of the FETCH cycle or during TS1 when KEY CONTROL L is asserted (remember that the EXAM and DEP keys assert KEY CONTROL L). Thus, the CPMA is gated to the adder, making possible CPMA+1 to the PC during automatic and manual operation.

E27 asserts ENO during TS3 of the EXECUTE state of a JMS instruction. The program count is stored in memory location 0000 when a JMS is forced by the INT IN PROG L signal. This sequence occurs during TS2 of the EXECUTE cycle. During TS3, the address in the CPMA, 0000, is incremented and sent to the PC. The new count, 0001, represents the address of the next instruction to be performed, and this instruction directs the processor to the starting address of the subroutine. Thus, when E27 asserts ENO, it allows CPMA+1 to be transferred to the PC during TS3 of the JMS instruction.

Table 3-5 indicates that the MQ Register can be gated to the "register in" line of the adder if EN0 and EN2 are brought to ground together. Note on the logic diagram (Figure 3-90) that this cannot be accomplished by any of the processor signals. MQ can be gated onto this line only by the KE8-E option (this feature is used by the SMA instruction). Thus, the remaining gates on the logic diagram are used to gate the MD lines to the adder, which is done by asserting both EN0 and EN1, while negating EN2. The MD lines are usually gated to the adder during TS2. The data from a memory location is transferred, either with or without modification, to the MAJOR REGISTERS BUS and loaded into the MB by TP2. NAND gate E13B causes EN1 and EN0 to be asserted during TS2 of all major states, with two exceptions. One of these exceptions occurs when the DCA instruction is being executed. To execute DCA, the processor must load the MB with the contents of the AC; thus, only the AC contents must be on the MAJOR REGISGERS BUS during TS2. The MB is loaded by TP2, the MD DIR L signal is negated, and the AC contents are written into the memory location. The other exception occurs during the DMA state (MS, IR DISABLE L is asserted), when the BRK DATA CONT L signal has not been asserted by a data break peripheral. Under these conditions, data is transferred by a peripheral to the DATAO L–DATA11 L lines during TS2 and gated unchanged through the adder to the MAJOR REGISTERS BUS. At TP2 time, the data is loaded into the MB and then placed on the MD lines.

The processor flow diagram (Section 2) illustrates the operations that require the MD lines to be gated to the adder. MD to the MB is carried out during the FETCH state and during the non-autoindexed DEFER state, though the operation is meaningless. Because MD to the MB does not disrupt processor operations, it is more convenient to allow, rather than inhibit, its occurrence.

The MD lines are gated to the adder in three other instances: (a) During TS3, when a TAD instruction is being executed, both the MD lines and the contents of the AC are gated to the adder. The resulting sum is then placed on the MAJOR REGISTERS BUS and loaded into the AC by TP3. Inverter E8E allows EN0 and EN1 to be asserted in response to the (TAD·E·TS3) L signal. (b) When the processor is in the DEFER state of an indirectly addressed JMP instruction, the contents of the PC Register are changed to address the location of the next instruction to be performed. This address, the effective address of the JMP instruction, is placed on the MD lines.

The MD lines are gated through the adder to the MAJOR REGISTERS BUS during TS3, and then loaded into the PC by TP3. NAND gate E13A allows EN0 and EN1 to be asserted by the BTS3, BD, and JMP L signals. (c)  $MD \rightarrow ADDER$  occurs also during the DEFER state; however, this instance specifically excludes the JMP instruction. If an AND, TAD, ISZ, DCA, or a JMS instruction has been indirectly addressed, the effective address is loaded in the CPMA, rather than the PC. The processor then goes to the EXECUTE state to operate on the data in the effective address. Thus, NAND gate E3B is enabled during TS4, thereby placing the effective address, contained on the MD lines, on the MAJOR REGISTERS BUS. TP4 then loads the address into the CPMA.

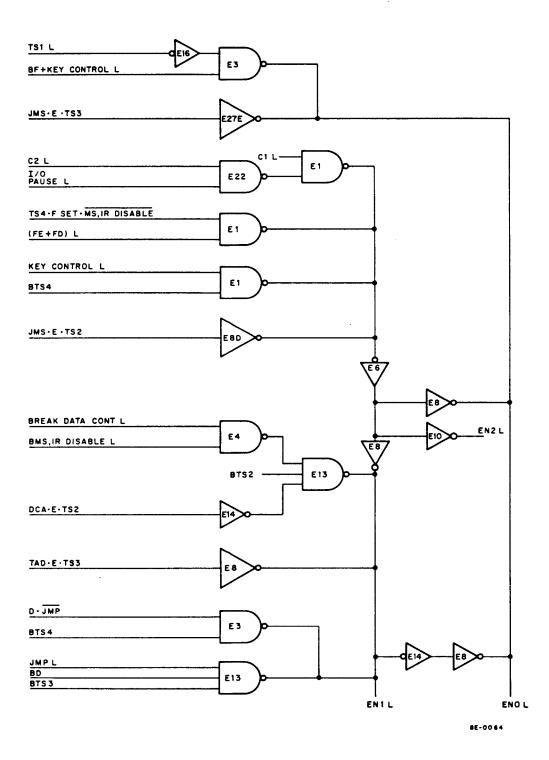

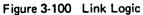

## 3.35.2 Data Line Enable Signals

The AC  $\rightarrow$  BUS and MQ  $\rightarrow$  BUS control signals are used to gate the 12 bits of the AC or MQ Registers to the DATA lines. The selected register can then be gated through the Data Control Gate to the "addend in" line of the adder.

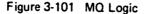

The logic elements that produce  $MQ \rightarrow BUS$  are shown in Figure 3-91. NAND gate E9A is used when the function select switch on the Programmer's Console is set to the MQ position. The console logic takes the IND2 line to ground and the IND1 line to a positive voltage. During TS1, the contents of the MQ are placed on the DATA 0 – DATA 11 lines and displayed on the Programmer's Console.

Figure 3-91 Data Line Enable Logic

NAND gate E9B is used to gate the MQ to the DATA lines for certain MQ microinstructions. Thus, this gate is enabled, provided the MQ BUS INH L signal is negated, for the following instructions: MQA, SWP, ACL, and CLA, SWP. The MQA instruction asserts both MQ  $\rightarrow$  BUS and AC  $\rightarrow$  BUS, a condition which causes an inclusive-OR to be performed by the Data Line Multiplexer. Each of the other MQ microinstructions asserts only MQ  $\rightarrow$  BUS. The MQ contents are then gated through the data control gate to the adder, placed on the MAJOR REGISTERS BUS, and loaded into the AC by TP3.

The logic that produces  $AC \rightarrow BUS$  is also shown in Figure 3-91. NAND gate E9C is used to gate the AC to the DATA lines during operate microinstructions. The AC contents are then gated to the adder, and the result of the arithmetic operation is loaded into the AC by TP3.

Inverters E10A and E10F assert AC  $\rightarrow$  BUS during the EXECUTE state. E10A allows the AC to be gated to the adder during TS3 of a TAD instruction; also during TS3, the contents of the MD lines are gated to the adder by the Register In Enable logic. Thus, the 2's complement adding operation is effected, and the result is stored in the AC. E10F is used during TS2 of a DCA instruction. The contents of the AC are to be deposited in a memory location. To accomplish this, the contents of the AC must be placed on the MAJOR REGISTERS BUS before TP2. At TP2 time, the MB is loaded and the MD DIR L signal is negated, placing the AC contents on the MD lines in preparation for the WRITE operation.

NAND gate E5 asserts AC  $\rightarrow$  BUS during TS2 of each FETCH cycle. This condition is not required by an instruction; however, it establishes the state of the AC lines at the positive I/O interface early in the FETCH cycle in order to maintain timing compatability with some older peripherals.

NAND gate E2C is used when the operator wishes to monitor the contents of the AC Register. During TS1, this information is placed on the DATA lines and used by the Programmer's Console logic.

E2B asserts AC  $\rightarrow$  BUS when an IOT instruction directs a data transfer to a peripheral. In this case, I/O PAUSE L is asserted by the processor, the correct C lines are asserted by the peripheral, and the information on the DATA lines is strobed into a peripheral Buffer Register.

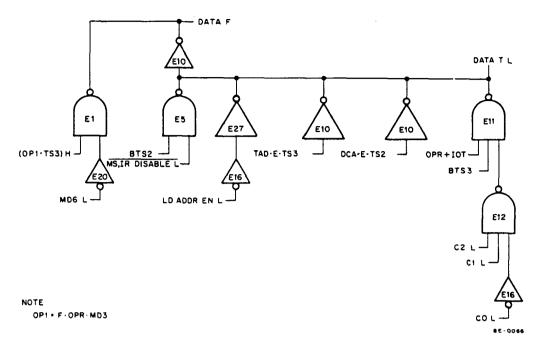

# 3.35.3 Data Enable Signals

The data enable signals, DATA T and DATA F, are used to determine the input for the addend in line of the adder. As indicated in the discussion of the data line enable signals, this input can be AC information, MQ information, or a combination of the two. The input can also be information that is being transferred from a peripheral to either the AC, PC, or MB. One other possibility exists: some operations require that the addend in line be an arithmetic 0. Therefore, the DATA T/DATA F signals are used to gate, to the adder, either the information carried on the DATA lines or an arithmetic 0. Table 3-6 is a truth table of these two signals (in terms of voltage levels); Figure 3-92 shows the logic that implements the truth table.

| Sig           | nal    | Explanation                                                                 |  |  |

|---------------|--------|-----------------------------------------------------------------------------|--|--|

| <b>DATA T</b> | DATA F | Input to Adder "addend in" line                                             |  |  |

| Low           | Low    | DATA LINES (complement of contents of AC or<br>MQ Registers, I/O XFER DATA) |  |  |

| Low           | High   | DATA LINES (contents of AC or MQ Registers, I/O TRANSFER DATA)              |  |  |

| High          | High   | 7777 (not used)                                                             |  |  |

| High          | Low    | Arithmetic 0                                                                |  |  |

|      | Table 3 | -6      |

|------|---------|---------|

| Data | Enable  | Signals |

Figure 3-92 Data Enable Logic

Information on the DATA lines is often a result of implementation of an OPR or an IOT instruction. NAND gate E11 is used to assert DATA T in either case. If an IOT instruction has been decoded, DATA T is asserted, and DATA F remains negated. The transfer can be either into or out of the processor, depending on which C control line, if any, is asserted by the peripheral. If the C lines specify a transfer into the processor, the information is placed on the DATA lines by the peripheral, gated through the adder, and placed on the MAJOR REGISTERS BUS; the information is loaded into either the AC or the PC at TP3. If the transfer is out of the processor, the information must also be retained in the AC and, therefore, it is gated through the MAJOR REGISTERS BUS and again loaded into the AC by TP3.

In one case, an IOT instruction does not cause DATA T to be asserted via E11. If the peripheral asserts the C0 L line, and leaves C1 L and C2 L negated, NAND gate E12 is enabled. Thus E11 is disabled, and, because no other gate enables DATA T under these circumstances, an arithmetic 0 is gated to the addend in line of the adder. This action results in an output data transfer and also a clearing of the AC, because 0s are loaded at TP3.

If an OPR microinstruction has been decoded, E11 is again used to assert DATA T, while DATA F is left negated. However, several OPR microinstructions (CMA, for example) are implemented by gating the complement of the signal on the DATA lines to the adder. This can be done if the DATA F signal is grounded along with DATA T. As Figure 3-92 shows, NAND gate E1 grounds DATA F; it does this only for those OPR microinstructions (CMA, CIA, CLA, CMA) that require the AC to be complemented.

DATA T can be asserted by any one of four other signals. One signal is (DCA·E·TS2) L, which asserts both AC  $\rightarrow$  BUS and DATA T. Thus, the AC information is gated to the MAJOR REGISTERS BUS and loaded into the MB by TP2. After the AC information is transferred, the AC must be cleared by negating DATA T and, thereby, placing a 0 on the "addend line" line. Because a 0 is also placed on the "register in" line during TS3 of a DCA instruction, a 0 is placed on the MAJOR REGISTERS BUS. This is then loaded into the AC by TP3. Another signal group that asserts both AC  $\rightarrow$  BUS and DATA T is TAD·E·TS3. Thus, the AC information is gated to the adder, where it is added to the contents of a memory location; the result is then loaded into the AC by TP3.

The LOAD ADDR EN L signal asserts DATA T during manual loading of an address. The operator sets an address on the console switch register and depresses the LOAD ADDR key. This action places the address on the DATA lines, and DATA T gates it to the MAJOR REGISTERS BUS. The address is then loaded into the CPMA by the CPMA LOAD L signal.

The last method of asserting DATA T is with NAND gate E35. This gate provides a path to the adder for data that is being transferred to the MB, either from a data break peripheral or from the console switch register. TP2 then loads the data from the MAJOR REGISTERS BUS into the MB.

## 3.36 ROUTE CONTROL SIGNALS

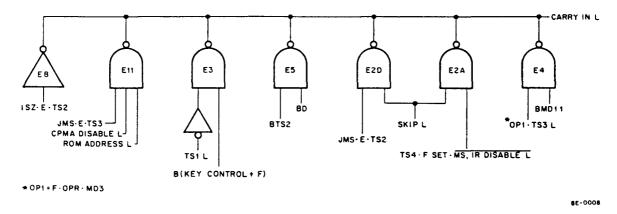

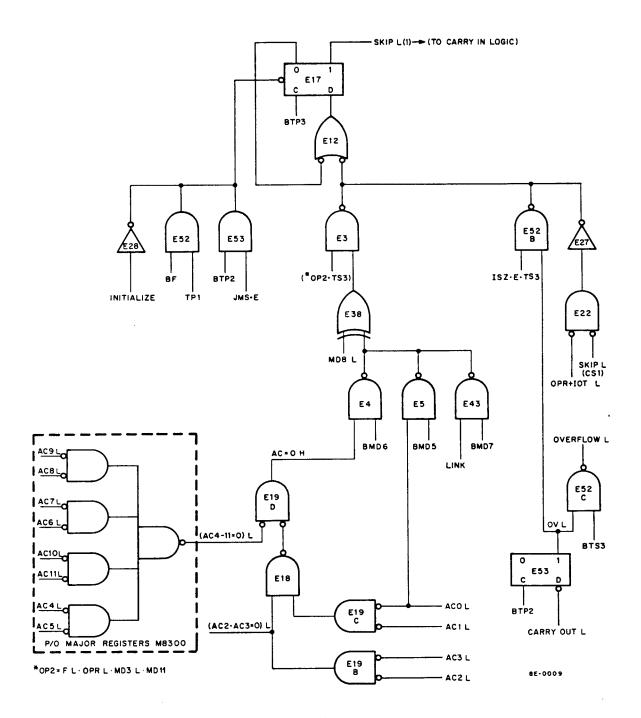

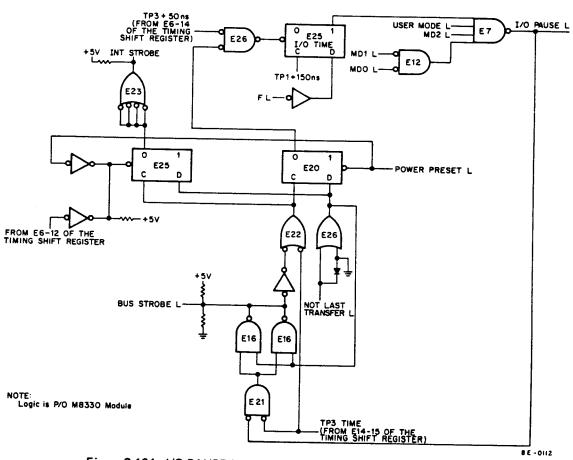

#### 3.36.1 Carry In Logic

The Carry In logic is shown in Figure 3-93. The CARRY IN L control signal enables the processor to increment data. The block diagram in Figure 3-87 shows that a CARRY IN L signal is applied to the adder IC (DEC 7483). This IC is a full adder and, therefore, can perform a complete addition by adding three inputs: an augend, an addend, and a carry from a previous order. In the PDP-8/E, the CARRY IN line of Figure 3-93 is applied directly to the carry input of adder 11, the LSB of the 12-bit data word. The carry from adder 11 is applied to adder 10, and so on, until the carry from adder 0 is applied to the LINK adder (Link logic is discussed in Paragraph 3.39).

Data is incremented during various operations which were introduced in the discussion of the source control signals. For example, the address carried on the MA lines is incremented during TS1 of the FETCH cycle. This new address is then loaded into the PC Register at TP1, thereby updating the program counter. The operation is represented symbolically as MA+1  $\rightarrow$  PC and is carried out as follows: (a) the data on the MA lines is gated to the register in line of the adder (the augend); (b) a 0 is gated to the addend in line of the adder (the addend); and (c) a 1 is gated to the CARRY IN line of the adder by NAND gate E3. The result, MA+1, is placed on the MAJOR REGISTERS BUS and loaded into the PC by TP1; because this must happen at the beginning of each instruction, E3 is enabled by TS1 L and F L.

NAND gate E3 asserts CARRY IN L during automatic operation and during those manual operations that cause the KEY CONTROL L signal to be generated (Paragraph 3.33). Remember that KEY CONTROL L can be asserted by three Programmer's Console keys: DEP, EXAM, and EXTD ADDR LOAD. Because both DEP and EXAM initiate a single timing cycle, the PC is updated by 1 (MA+1  $\rightarrow$  PC) each time either of these keys is activated. The EXTD ADDR LOAD key also asserts KEY CONTROL L and, thus, CARRY IN L; however, both assertions are meaningless in the present application, because no timing cycle is initiated by EXTD ADDR LOAD L.

The program count must also be incremented during the EXECUTE cycle of a JMS instruction. The program count is stored in the memory location specified by the operand of the JMS instruction, e.g., location Y. The processor then proceeds to the first instruction of the subroutine. The address of this first instruction is contained in location Y+1; thus, the PC must be incremented and, as in the last example, the operation is represented symbolically as MA+1  $\rightarrow$  PC. This operation is accomplished during TS3 by NAND gate E11. The ROM ADDRESS L and CPMA DISABLE L signals are asserted if the MR8-E (Read-Only Memory) option is included in the system. Use of CARRY IN L with this option or with any option designed to assert CPMA DISABLE L only is discussed in Volume 2.

Inverter E8 asserts CARRY IN L in response to the signal ISZ·E·TS2. The ISZ instruction directs the processor to increment the data in the specified location and then skip the next instruction if the result of the incrementation is 0000. To increment the data, the processor performs the operation MD+1  $\rightarrow$  MB. The CARRY IN L line is asserted during TS2 of the EXECUTE cycle so that MD+1 can be loaded into the MB at TP2 time. The second portion of the ISZ instruction is carried out as described in Paragraph 3.38.

NAND gate E5 also asserts CARRY IN L. E5 does this during TS2 of a DEFER cycle and as part of the operation MD+1  $\rightarrow$  MB. Remember that this operation has significance during the DEFER cycle only if an Autoindex Register (locations 0010-0017) has been referenced by the instruction being performed. When this is the case, the content of this register is incremented before it is used as the operand. Autoindexing is discussed fully in Chapter 4 of the PDP-8/E & PDP-8/M Small Computer Handbook.

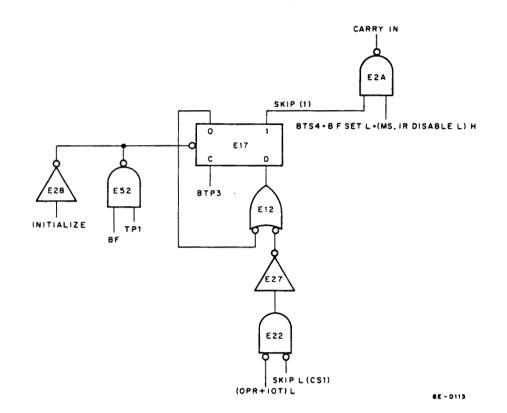

NAND gates E2A and E2D are used with the Skip logic (Paragraph 3.38) to assert CARRY IN L. Gate E2A asserts CARRY IN L when a skip of one program instruction (symbolized as PC+1  $\rightarrow$  CPMA) is required. This requirement arises if: (a) a Group 2 operate microinstruction such as SKP (skip unconditionally) is programmed; (b) if an IOT instruction causes a peripheral to assert the OMNIBUS SKIP L signal; and (c) as a result of the ISZ instruction. In each of these circumstances, TP3 sets the SKIP flip-flop, E13 (Paragraph 3.38), thereby asserting the SKIP (1) line high. During TS4, CARRY IN L is asserted, the PC is gated to the adder and incremented, and the result is placed on the MAJOR REGISTERS BUS and loaded into the CPMA at TP4. The F SET L portion of the enabling signal at E2A ensures that CARRY IN L is not asserted during TS4 of a DMA state. For example, if the program is stopped by the HALT key, the SKIP flip-flop can remain set. Then, if the operator pushes the EXAM key, CARRY IN L is asserted and PC+1, rather than PC only, is loaded into the CPMA at TP4 time of the memory cycle. MS, IR DISABLE L prevents this error from occurring because it is high.

NAND gate E2D is used to assert CARRY IN L if a program interrupt prevents gate E2A from asserting it. For example, if a Group 2 OPR microinstruction causes the SKIP flip-flop to be set at TP3, the PC should be incremented during TS4. However, if the interrupt system logic located in the Timing Generator has honored a peripheral's interrupt request, the OMNIBUS INT IN PROG H signal is also asserted at TP3. The assertion of INT IN PROG H prevents the PC from being gated to the adder network during TS4 (Paragraph 3.35.1). The CPMA is

loaded with 0s, rather than being loaded with the incremented PC contents at TP4. The processor then enters the EXECUTE state. During TS2, CARRY IN L is asserted by E2D, and the PC is gated to the adder and incremented. At TP2 the result (PC+1) is stored in location 0, and the SKIP flip-flop is reset. When the interrupt has been serviced, a JMP I to location 0 causes the main program to be resumed at location PC+1 (the original location if the interrupt had not been requested).

The last gate to consider in the Carry In logic is NAND gate E4. This gate is used during TS3 of a FETCH cycle to carry out operate instructions involving the IAC command. If IAC has been programmed, the contents of the AC are placed on the DATA lines during TS3 and gated through the Data Control Gate to the adder. A 0 is gated to the adder's register in line. E4 asserts CARRY IN L; the result, AC+1, is placed on the MAJOR REGISTERS BUS and loaded into the AC by TP3.

If CIA has been programmed, the operation is similar to that just outlined. However, the data in the AC is complemented by the Data Control Gate before it is applied to the addend in line of the adder. Thus, the result, AC<sub>complement</sub>+1, is loaded into the AC at TP3.

When CLA IAC is programmed, 0s are provided at the addend in and register in lines of the adder. When CARRY IN L is asserted, the resulting output from the adder is  $0001_8$ . This is loaded into the AC at TP3, setting AC=1. Similar operations occur when the IAC command is microprogrammed with other Group 1 operate instructions.

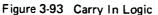

#### 3.36.2 Shift Control Signals

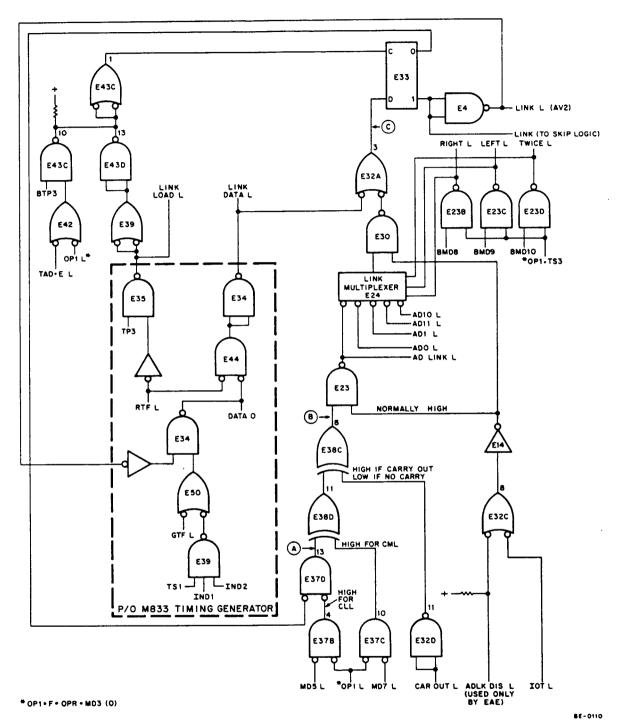

The shift logic is shown in Figure 3-94. The control signals produced by this logic, RIGHT L, LEFT L, TWICE L, and PAGE Z L, gate data to the MAJOR REGISTERS BUS. This data can be taken from an adder, from a NAND gate, or from the PAGE Z multiplexer, as illustrated by the block diagram of Figure 3-87.

Figure 3-94 Shift Logic

A data bit can be transferred from one major register to another major register (Paragraph 3.34 where bit 0 was considered). To transfer bit 0 from one register to another, a "no shift" condition is needed by the Adder Output Multiplexer. As shown in Table 3-7, this condition arises when RIGHT L, LEFT L, and TWICE L are high, and PAGE Z L is low. Because most processor operations involve no shifting, this combination of signals normally prevails. A different combination can arise during either TS3 or TS4 of a FETCH cycle, with one exception. This exception, as shown on the logic diagram (Figure 3-94), occurs during TS3 of the EXECUTE cycle of an AND instruction and is discussed in the following paragraph. Thus, unless the program specifically requires a shifting operation, the shift signals remain as shown above. Shifting is a consequence of any one of five operate microinstructions (Paragraph 3.34). These microinstructions, RAR, RAL, RTR, RTL, and BSW, enable NAND gates E23B, E23C, and E23D in combinations that cause the desired shifting to occur. For example, if RAR (7010<sub>8</sub>) (rotate AC and LINK right one) is programmed, NAND gate E23B is enabled during TS3 of the FETCH cycle. Bit X of the AC Register is placed on the DATA X line at the beginning of TS3, and gated through Data Control Gate X to adder X. A 0 is gated to the register in line of the adder. The adder CARRY IN line is negated. The adder X output is selected by Adder Output Multiplexer X+1, in response to the RIGHT L signal, and placed on MAJOR REGISTERS BUS X+1. At TP3 time, the data is loaded into bit X+1 of the AC Register. In the same manner, AC bit X can be shifted to the right twice (RTR) to AC bit X+2, to the right by six (BSW), or to the left in response to RTL, for example. All this shifting is accomplished by NAND gate E23.

RIGHT L, LEFT L, and TWICE L signals are used in operations other than shifting. Both RIGHT L and LEFT L are asserted by the composite signal AND·E·TS3, as illustrated in Figure 3-94. This combination enables each Adder Output Multiplexer to select the output of a NAND gate for transfer to the MAJOR REGISTERS BUS. This NAND gate is used to implement the basic AND instruction. During the EXECUTE cycle of this instruction, data in the addressed memory location is brought from memory and loaded into the MB Register at TP2 time. The MB Register output is logically NANDed with the AC Register output. During TS3, the logical result is gated through the Adder Output Multiplexer by RIGHT L and LEFT L signals to the MAJOR REGISTERS BUS and loaded into the AC at TP3 time.

Seven of the eight inputs to the Adder Output Multiplexer have been considered with respect to the shift signals. The eighth input is taken from the PAGE Z multiplexer (Figure 3-87). The gating networks for bits 0 through 4 use this multiplexer to provide the page address of the operand of either an MRI or an indirectly addressed JMP instruction. If this address is on the current page, the PAGE Z multiplexer output gates the data on MA lines 0 through 4 to the Adder Output Multiplexers. RIGHT L, LEFT L, and TWICE L signals gate these (0-4) bits to the MAJOR REGISTERS BUS. They are then loaded into CPMA 0 through 4, respectively, at TP4 time (this applies to an MRI; they are loaded into PC 0-4 and CPMA 0-4 for the JMP I instruction). Table 3-7, entry 8, lists the signal levels required to carry out this operation. This condition is implemented by gates E7, E13, E28, E32, and E36, shown in Figure 3-94. NAND E7 is enabled only during TS4 of a FETCH cycle. F SET L must be negated, ensuring that the instruction is either a JMP I or an MRI (if F SET L is negated, either a DEFER or an EXECUTE cycle follows the FETCH). The (FE+FD) L signal must also be negated. If the KE8-E option is not in the system, (FE+FD) L can be asserted only if the INT IN PROG H signal is asserted. Because INT IN PROG H is asserted only if F SET L is negated. (FE+FD) L to be asserted even though F SET L is negated. Refer to Volume 2 for a further discussion.

| RIGHT L | LEFT L | TWICE L              | PAGE Z L | Input To Adder<br>Output Multiplexer                                                                            | Used For                                                                                                |  |

|---------|--------|----------------------|----------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| н       | н      | HI                   | LO       | ADDER X                                                                                                         | No-Shift Operations                                                                                     |  |

| ні      | LO     | ні                   | LO       | ADDER (X+1)                                                                                                     |                                                                                                         |  |

| ні      | LO     | LO LO LO ADDER (X+2) |          | Rotate                                                                                                          |                                                                                                         |  |

| LO      | н      | ні                   | LO       | ADDER (X-1)                                                                                                     | and<br>Byte Swap                                                                                        |  |

| LO      | н      | LO                   | LO       | ADDER (X-2)                                                                                                     | Instructions                                                                                            |  |

| н       | ні     | LO                   | LO       | ADDER (X+6)                                                                                                     |                                                                                                         |  |

| LO      | LO     | н                    | LO       | АСХ АСХ•МВХ                                                                                                     | Logical AND<br>Instruction (0000)                                                                       |  |

| LO      | LO     | LO                   | LO       | PAGE Z Multiplexer 0-4 to<br>Adder Output Multiplexers 0-4.<br>MA 0-4 loaded into CPMA 0-4<br>(or into PC 0-4). | Providing Page Address of<br>operand of either an MRI or<br>an indirectly addressed JMP<br>instruction. |  |

|         |        |                      |          | MD Lines 0–11 to Adder Output<br>Multiplexers 5–11, loaded into<br>CPMA 5–11 (or PC 5–11).                      | Providing Relative Address of either of above.                                                          |  |

| LO      | LO     | LO                   | ні       | PAGE Z Multiplexer 0-4 to<br>Adder Output Multiplexer 0-4.<br>Os loaded into CPMA 0-4 (or<br>into PC 0-4).      | Providing Page Address                                                                                  |  |

|         |        |                      |          | MD lines 5–11 to Adder Output<br>Multiplexer 5–11, loaded into<br>CPMA 5–11 (or PC 5–11),                       | Providing Relative Address                                                                              |  |

Table 3-7 Shift Control Operations

NOR gate E18 is enabled, and the high level at its output causes inverter E28 to assert RIGHT L, LEFT L, and TWICE L. This high level is also applied to E32, where it is NANDed with the signal representing the state of MD4 L. If MD4 L is asserted (the address of the operand is on the current page) PAGE Z L is negated. The data on MA lines 0–4 is loaded into CPMA 0–4 at TP4 time. However, if MD4 L is negated (the address of the operand is on page 0), PAGE Z L is asserted. In this case, the PAGE Z multiplexer provides arithmetic 0s for the Adder Output Multiplexer; these 0s are loaded into CPMA 0–4 at TP4 time.

The PAGE Z multiplexer is also used to provide the page address of an indirectly addressed JMP instruction. This operation is carried out in the same manner as described for the MRI. If the JMP instruction is directly addressed, it is carried out in one cycle of operation. Thus, NAND gate E12 is used to assert the RIGHT L, LEFT L, and TWICE L signal lines. As before, MD4 L can be asserted or negated. If this line is asserted, the data on MA lines 0–4 is placed on the MAJOR REGISTERS BUS and loaded into the PC Register (bits 0–4, respectively) at TP3 time. If MD4 L is negated, 0s are loaded into PC 0–4.