# CHAPTER 4 MAINTENANCE

This chapter contains information pertinent to preventive maintenance, corrective maintenance, and troubleshooting techniques of the PDP-8/E.

#### **SECTION 1 - PREPARATION FOR MAINTENANCE**

#### 4.1 EQUIPMENT

Table 4-1 lists the equipment and relevant specifications needed for maintenance of the basic PDP-8/E. Also included in the list is the equivalent equipment used by DEC Field Service personnel.

#### 4.2 PROGRAMS

Table 2-4 in Chapter 2 lists the maintenance programs supplied by DEC for ascertaining proper PDP-8/E operation. To supplement these programs, there are eight short test routines detailed in the following paragraphs. These routines can be used, as needed, to perform the required maintenance.

#### NOTE All diagnostics require a Programmer's Console, a working Teletype and at least 4K memory with the basic system.

#### 4.2.1 TTY Receiver Test

Perform the following test to display a character (any character depressed on keyboard or read from paper tape) in the ac. Load address 0000 and deposit the following test routine in sequence:

| Location | Contents |  |

|----------|----------|--|

| 0000     | 6032     |  |

| 0001     | 6031     |  |

| 0002     | 5001     |  |

| 0003     | 6036     |  |

| 0004     | 5001     |  |

Load address 0000 and press CONT.

| Equipment                             | Specifications                                                                                                                                                                    | Equivalent                              |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Multimeter                            | 10kΩ/V minimum                                                                                                                                                                    | Triplett Model 310                      |

| Oscilloscope                          | dc to 50 Hz with calibrated deflection factors from 5 mV to 10V/div. Maximum horizontal sweep rate of 0.1 $\mu$ s/div. Delaying sweep is desirable and dual trace is a necessity. | Tektronix Type 453                      |

| Probes                                | X10 with response characteristics matched to oscilloscope.                                                                                                                        | Tektronix Type P6010                    |

| Recessed Probe Tip (2)                |                                                                                                                                                                                   | Tektronix                               |

| Ground Leads (for<br>each probe)      |                                                                                                                                                                                   | Tektronix                               |

| Integrated Circuit Pin<br>Extender    | AP Inc                                                                                                                                                                            | DEC 29-10246                            |

| Double-Height<br>Extender (2)         |                                                                                                                                                                                   | W984                                    |

| Edge Connector<br>Extender Cables (2) |                                                                                                                                                                                   | BC08M-OM                                |

| Light Bulb Extractor                  |                                                                                                                                                                                   | DEC 12-9151                             |

| Tool Kit                              |                                                                                                                                                                                   | DEC Type 142                            |

| Black Spray Paint                     |                                                                                                                                                                                   | DEC 120-68                              |

| White Spray Paint                     |                                                                                                                                                                                   | DEC 120-94                              |

| Jumper Wire                           |                                                                                                                                                                                   | 30-Gauge with TERM<br>POINT Connections |

| Silicone Grease                       |                                                                                                                                                                                   | Dow Corning<br>Compound                 |

| 1/16 in. Allen Wrench                 |                                                                                                                                                                                   | Hunter 4Z 035                           |

| Single-Height<br>Extender Module (1)  |                                                                                                                                                                                   | W980                                    |

# Table 4-1 Maintenance Equipment

#### 4.2.2 TTY Transmitter Test

Perform the following test to print the character in the Switch Register (bits 04-11). Load address 0000 and deposit the following test routine in sequence:

| Location | Contents |  |

|----------|----------|--|

| 0000     | 7604     |  |

| 0001     | 6046     |  |

| 0002     | 6041     |  |

| 0003     | 5002     |  |

| 0004     | 5000     |  |

Load address 0000 and press CONT. To print a different character, change the contents of the Switch Register.

#### 4.2.3 Echo Test

Perform the following test to type a character on the keyboard. Load address 0000 and deposit the following test routine in sequence:

| Location | Contents |

|----------|----------|

| 0000     | 6032     |

| 0001     | 6031     |

| 0002     | 5001     |

| 0003     | 6036     |

| 0004     | 6046     |

| 0005     | 6041     |

| 0006     | 5005     |

| 0007     | 5001     |

Load address 0000 and press CONT. Type any character on the keyboard and observe a corresponding echo return on the printer.

#### 4.2.4 Print Test

Perform the following test to print all characters. Load address 0000 and deposit the following test routine in sequence:

| Location | Contents |                        |

|----------|----------|------------------------|

| 0000     | 7001     | /Increment ac          |

| 0001     | 6046     | /Load buffer and print |

| 0002     | 6041     | /Skip if flag is set   |

| 0003     | 5002     | /JMP 1                 |

| 0004     | 5000     | /JMP O                 |

Load address 0000 and press CONT.

#### 4.2.5 Deposit SR into Corresponding Address

Perform the following test to deposit the contents of the Switch Register into the corresponding address. Load address 0000 and deposit the following test routine in sequence:

| Location | Contents |  |

|----------|----------|--|

| 0000     | 7604     |  |

| 0001     | 3005     |  |

| 0002     | 1005     |  |

| 0003     | 3405     |  |

| 0004     | 5000     |  |

Load address 0000, change SR to any number equal to or greater than 5, and press CONT.

#### 4.2.6 4K Core Transfer (8K or more systems only)

Perform the following test to test the relocation process. Load address 7600 and deposit the following routine in sequence:

| Location | Contents |                                                       |

|----------|----------|-------------------------------------------------------|

| 7600     | 6201     | /Change data field to 0 (specifies source field)      |

| 7601     | 1670     | /TAD   7670                                           |

| 7602     | 6211     | /Change data field to 1 (specifies destination field) |

| 7603     | 3670     | /DCA I 7670                                           |

| 7604     | 2270     | /Increment LOC 7670                                   |

| 7605     | 5300     | /JMP 5                                                |

| 7606     | 7402     | /Halt when transfer complete                          |

| 7670     | 0000     |                                                       |

Load address 7600 and press CONT. This routine can also be used to relocate diagnostic programs from one field to the other.

#### 4.2.7 Write All Zeros

Perform the following test to write 0s in all address locations except some locations already occupied by the program. Load address 0004 and deposit the following test routine in sequence:

| Location | Contents |

|----------|----------|

| 0004     | 1007     |

| 0005     | 3410     |

| 0006     | 5004     |

| 0007     | 0000     |

| 0010     | 0011     |

Load address 0004 and press CONT. Computer will hang-up and all addresses will contain 0s, except locations occupied by the program. Note: addresses 0004 and 0005 will contain 0s after one program pass.

To write any other word, repeat the same procedures but change address 0007 to the desired word.

#### SECTION 2 - PREVENTIVE MAINTENANCE

#### 4.3 PREVENTIVE MAINTENANCE INSPECTIONS

This section provides information for performing preventive maintenance inspections. This information consists of visual, static, and dynamic tests that provide better equipment reliability. Preventive maintenance consists of procedures that are performed prior to the initial operation of the computer and periodically during its operating life. These procedures include visual inspections, cleaning, mechanical checks, and operational testing. A log should be kept to record specific data that indicates the performance history and rate of deterioration; such a record can be used to determine the need and time for performing corrective maintenance on the system.

Scheduling of computer usage should always include specific time intervals that are set aside for scheduled maintenance purposes. Careful diagnostic testing programs can then reveal problems which may only occur intermittently during on-line operation.

#### 4.4 SCHEDULED MAINTENANCE

The PDP-8/E must receive certain routine maintenance attention to ensure maximum life and reliability. Digital Equipment Corporation suggests the maintenance schedule defined in Table 4-2.

| Туре      | Action                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cleaning  | a. Clean the exterior and interior of the computer cabinet, using a vacuum cleaner and/or clean cloths moistened in nonflammable solvent.                                                        |

|           | b. Clean the air filter. Use a vacuum cleaner to remove accumulated dirt and dust, or wash with clean hot water and thoroughly dry before using.                                                 |

| Lubricate | a. Lubricate slide mechanisms and casters with a light machine oil or powdered graphite.<br>Wipe off excess oil.                                                                                 |

| Inspect   | a. Visually inspect equipment for general condition. Repaint any scratched areas.                                                                                                                |

|           | b. Inspect all wiring and cables for cuts, breaks, fraying, wear, deterioration, kinks,<br>strains, and mechanical security. Tape, solder, or replace any defective wiring or cable<br>covering. |

|           | c. Inspect the following for mechanical security: key switches, control knobs, lamps, connectors, transformers, fans, capacitors, etc. Tighten or replace as required.                           |

|           | d. Inspect all module mounting panels to ensure that each module is securely seated in its connector. Remove and clean any module that may have collected excess dirt or dust.                   |

## Table 4-2 Processor Preventive Maintenance Schedule (3 months or 500 hours)

# Table 4-2 (Cont)Processor Preventive Maintenance Schedule3 months or 500 hours

| Туре    | Action                                                                                                                                                                                                                                                                                    |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | e. Inspect power supply components for leaky capacitors, overheated resistors, er<br>Replace any defective components.                                                                                                                                                                    |  |  |  |

|         | f. Check the output of the H724(A) power supply as specified in Table 4-8. Use a multimeter to make these measurements without disconnecting the load. If any output voltage is not within tolerance, the supply is considered defective, and corrective maintenance should be performed. |  |  |  |

| Perform | a. Run all MAINDEC programs to verify proper computer operation in Table 2-4. Each program should be allowed to run for at least three minutes or two passes, whichever is longer.                                                                                                        |  |  |  |

|         | b. Perform all preventive maintenance operations for each peripheral device included in<br>the PDP-8/E System as directed in the individual maintenance instructions supplied<br>with each peripheral device.                                                                             |  |  |  |

|         | c. Enter preventive maintenance results in log book.                                                                                                                                                                                                                                      |  |  |  |

#### 4.4.1 Weekly Preventive Maintenance Schedule

r

Under weekly maintenance, time should be scheduled each week to operate the MAINDEC programs as listed in Table 2-4. Run each program for a minimum of three minutes. Take any corrective action necessary at this time and log the results. External cleanliness of the system should also be maintained on a weekly basis.

#### 4.4.2 The Importance of a Preventive Maintenance Schedule

Computer downtime can be minimized by rigid adherence to a preventive maintenance schedule. A dirty air filter can cause machine failure through overheating. All filters should be cleaned periodically. The procedure for filter cleaning is described in Table 4-2.

#### **SECTION 3 - CORRECTIVE MAINTENANCE**

#### 4.5 MAINTENANCE PROCEDURES

The PDP-8/E is constructed of highly reliable MSI IC logic modules. Use of these circuits and a minimum amount of preventive maintenance ensures relatively little equipment downtime due to failure. If a malfunction occurs, maintenance personnel should analyze the condition and correct it as indicated in the following procedures. Neither special test equipment nor special tools are required for corrective maintenance other than a broad-bandwidth oscilloscope and a multimeter. The best corrective maintenance tool is a thorough understanding of the physical and electrical characteristics of the equipment. Persons responsible for maintenance should become thoroughly familiar with the system concept, logic drawings, operation of specific IC circuits, and location of mechanical and electrical components.

It is virtually impossible to outline any specific procedures for locating faults within complex digital systems such as the PDP-8/E. However, diagnosis and remedial action for a fault condition can be undertaken logically and systematically in the following phases:

- a. Preliminary Investigation

- b. System Troubleshooting

- c. Logic Troubleshooting

- d. Circuit Troubleshooting

- e. Repairs and Replacement

- f. Validation Tests

- g. Log Entry

#### 4.5.1 Preliminary Investigation

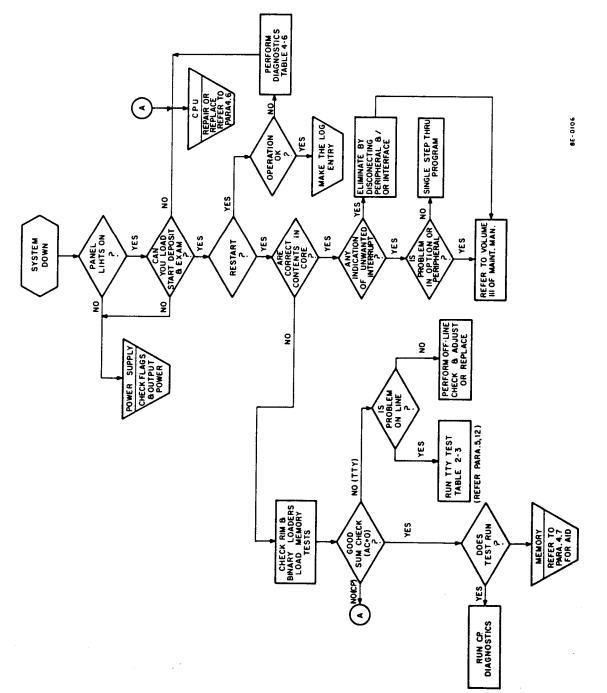

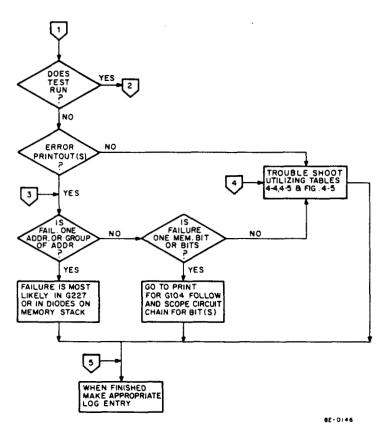

Before beginning troubleshooting procedures, explore every possible source of information. Gather all available information from those users who have encountered the problem and check the system log book for any previous references to the problem. The troubleshooting flowchart (Figure 4-1) should be used to localize the problem. This flowchart is not a complete guide to determining system fault; it is intended to give the user some thoughts on where a problem could be, a possible solution, and how to describe it to the DEC representative before he arrives on site.

Do not attempt to troubleshoot by use of complex system programs alone. Run the MAINDEC programs and select the shortest, simplest program available that exhibits the error conditions. MAINDEC programs are carefully written to include program loops for assistance in system and logic troubleshooting.

#### 4.5.2 System Troubleshooting

When the problem is understood and the proper program is selected, the logical section of the system at fault should be determined. Obviously, the program that has been selected gives a reasonable idea of what section of the system is failing. However, faults in equipment that transmit or receive information, or improper connection of the system, frequently give indications similar to those caused by computer malfunctions.

Disconnect any peripheral devices that are not necessary to operate the failing program. At this time, reduce the program to its simplest scope loop and duplicate this loop in a dissimilar portion of memory to verify, for instance, that an operation failure is not dependent on memory location. This process can aid in distinguishing memory failures from processor failures. Use of the techniques described above often pinpoints the problem to a module or several ICs.

#### 4.5.3 Logic Troubleshooting

Before attempting to troubleshoot the logic, make certain that proper and calibrated test equipment is available. Always calibrate the vertical preamp and probes of an oscilloscope before using. Make sure the oscilloscope has a good ground via the ac line cord, and keep the ground to the probe as short as possible with the aid of probe ground leads.

To extend the suspected module in the OMNIBUS perform the following procedure:

- 1 Turn off power.

- 2 Remove the H851 Edge Connector, if applicable, from the module.

- 3 Remove the module.

- 4 Insert two double-extender boards into the same slot.

- 5 Insert the suspected module into the extender board.

- 6 If applicable, connect the two edge-connector extender cables (BC08M-OM). This method should be used only with short program loops.

- 7 Turn power on.

- 8 Use IC pin extender for signal tracing and for grounding of scope.

#### NOTE Test points on individual modules can be observed by connecting the oscilloscope to available pins on the extender.

Use the oscilloscope and IC pin extender to trace signal flow through the suspected logic elements. Oscilloscope sweep can be synchronized by control pulses or by level transitions that are available on individual IC pins at the component side of the module. Exercise care when probing the logic, to prevent shorting between pins. Shorting of signal pins to power supply pins can result in damaged components. Within modules, unused gate inputs are held at +3V.

#### NOTE

If vibration of the PDP-8/E is desired during troubleshooting, ensure that the vibration is of low enough amplitude that intermodule shorts will not occur.

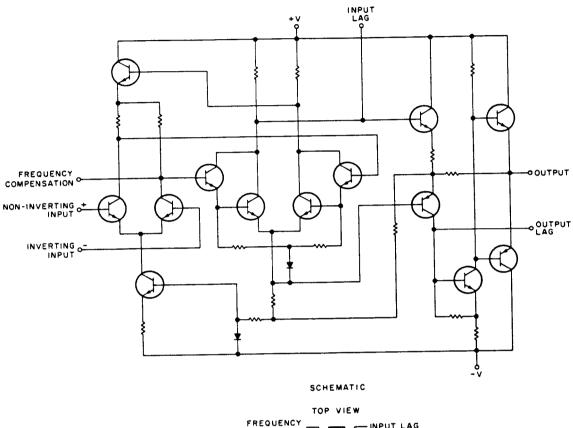

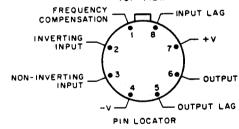

#### 4.5.4 Circuit Troubleshooting

Engineering schematic diagrams of each module are supplied with each PDP-8/E System and should be referred to for detailed circuit information.

Visually inspect the module on both the component side and the printed wiring side to check for overheated or broken components or etch. If this inspection fails to reveal the cause of trouble or confirm an observed fault condition, use the multimeter to measure resistance of suspected components.

#### CAUTION

Do not use the lowest or highest resistance ranges of the multimeter when checking semiconductor devices. The X10 range is suggested. Failure to heed this warning may result in damage to components.

Measure the forward and reverse resistances of diodes. Diodes should measure approximately  $20\Omega$  forward and more than  $1000\Omega$  reverse. If readings in each direction are the same and no parallel paths exist, replace the diode.

Measure the emitter-collector, collector-base, and emitter-base resistances of transistors in both directions. Short circuits between collector and emitter or an open circuit in the base-emitter path cause most failures. A good transistor indicates an open circuit in both directions between collector and emitter. Normally  $50\Omega$  to  $100\Omega$  exist between the emitter and the base, or between the collector and the base in the forward direction, and an open circuit condition exists in the reverse direction. To determine forward and reverse directions, consider a transistor as two diodes connected back to back. In this analogy, PNP transistors would have both cathodes connected together to form the base, and both the emitter and collector would assume the function of an anode. In NPN transistors, the base would be a common-anode connection; and both the emitter and collector, the cathode.

Multimeter polarity must be checked before measuring resistance, because many meters apply a positive voltage to the common lead when in the resistance mode.

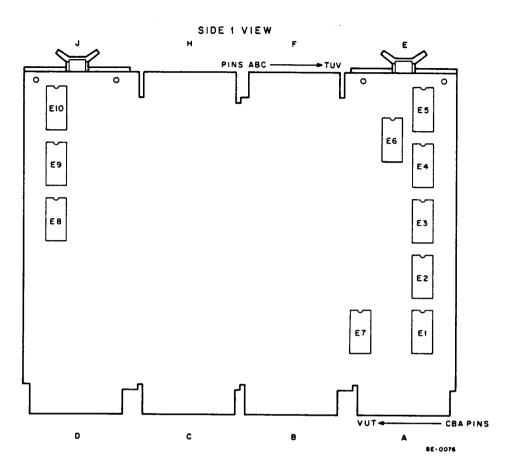

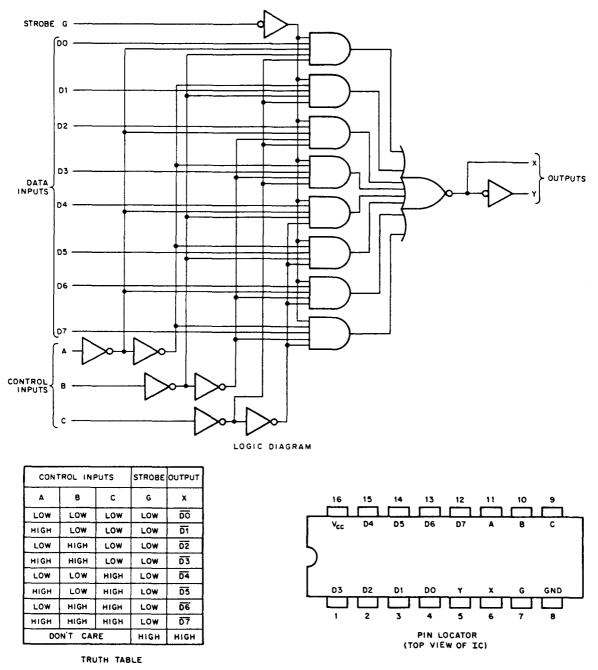

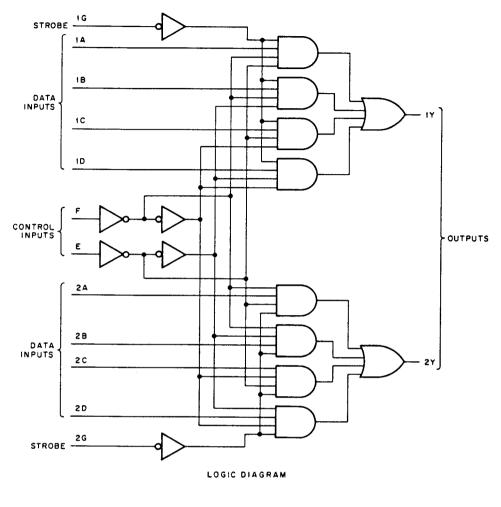

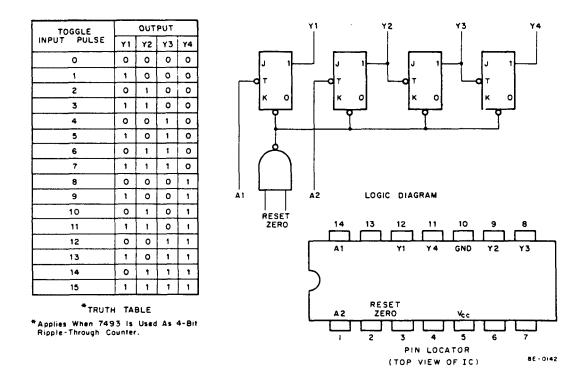

ICs contain complex integrated circuits with only the input, output, and power terminals available; thus, static multimeter testing is limited to continuity checks for shorts between terminals. IC checking is best done under dynamic conditions using a module extender to make terminals readily accessible. Using PDP-8/E logic diagrams and M-series module schematics, locate an IC on a circuit board as follows:

- 1 Hold the module with the handle in your left hand; component side facing you.

- 2 ICs are numbered starting at the contact side of the board; upper right-hand corner.

- 3 The numbers increase toward the handle.

- 4 When a row is complete, the next IC is located in the next row at the contact end of the board (Figure 4-2).

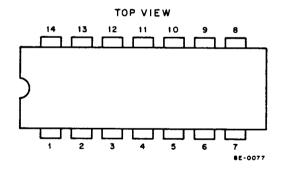

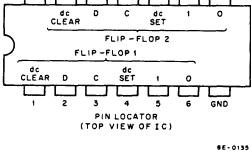

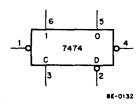

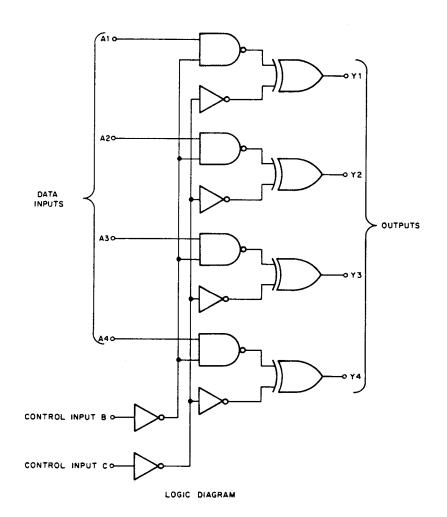

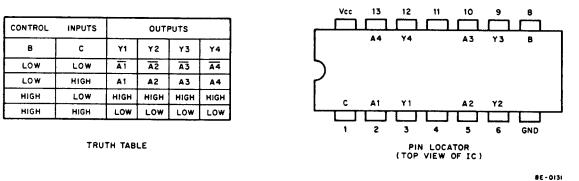

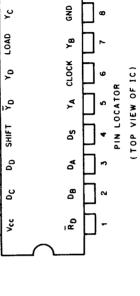

- 5 The pins on each IC are located as Figure 4-3 illustrates.

Figure 4-2 IC Location

•

#### 4.5.5 Repairs and Replacements

When soldering semiconductor devices (transistor, diodes, rectifiers, or integrated circuits) that can be damaged by heat, physical shock, or excessive electrical current, take the following special precautions:

- 1 Use a heat sink, such as a pair of pliers, to grip the lead between the joint and device being soldered.

- 2 Use a 6V iron with an isolation transformer. Use the smallest iron adequate for the work. Use of an iron without an isolation transformer can result in excessive voltages presented at the iron tip. Use only pencil-pointed tip soldering irons on PC boards.

- 3 Perform the soldering operation in the shortest possible time to prevent damage to the component and delamination of the module etched wiring.

- 4 ICs can be removed by using a solder puller to remove all excessive solder from contacts. Then, by straightening the leads, lift the IC from its terminal points. If it is not desired to save the defective IC for test purposes, perform Steps 5 through 12. If the IC is to be saved, perform Steps 8 through 12 (remove IC following Step 8).

- 5 Clip IC leads at top of lead at the connection to chip.

- 6 Remove chip portion of IC.

- 7 Apply heat to individual leads from siside #1 and remove leads slowly from side #1, using a pair of needle nose pliers. Do not hold lead with pliers while applying heat; the pliers will act as a heat sink.

- 8 Turn board over to side #2 and heat each hole individually, removing excess solder with desoldering tool.

- 9 Insert new component, bending appropriate leads. (Only leads with tear drop lands should be bent. They should be bent in the direction of the point.)

- 10 Clip protruding component leads from side #2. Do not cut flush with the board. (Leads and solder joints cannot exceed 1/16 in. from bottom of board.)

- 11 Solder all leads on side #2.

- 12 Clean flux from both sides of board with TRICHLORETHYLENE, FREON, or equivalent. Be careful -- both substances will damage the plastic handle.

In all soldering and unsoldering operations in the repair and replacement of parts, avoid placing excessive solder or flux on adjacent parts or service lines. When repair has been completed, remove all excess flux by washing junctions with a solvent such as trichlorethylene. Be very careful not to expose paint or plastic surfaces to this solvent.

#### CAUTION

Never attempt to remove solder from terminal points by heating and rapping module against another surface. This practive can result in module or component damage. Remove solder with a solder-sucking tool or solderwick. When removing any part of the equipment for repair and replacement, make certain that all leads or wires that are unsoldered, or otherwise disconnected, are legibly tagged or marked for identification with their respective terminals. Replace defective component only with parts of equal or better quality and equal tolerance.

To remove a switch on the Programmer's Console, follow the procedure below:

- 1 Turn power off.

- 2 Loosen Allen screw and remove knob from rotary switch.

- 3 Remove four screws from Bezel.

- 4 Carefully remove the face plate.

- 5 Remove two screws retaining aluminum mounting bracket.

- 6 Remove two wires from tab terminals on the left-hand side of the console.

- 7 Remove Programmer's Console board.

- 8 Remove faulty switch.

- 9 When replacing the panel, the yellow wire goes to the top tab terminal and blue wire to the bottom.

To remove the power supply heat sink assembly (Paragraph 4.8), follow the procedure below:

1 Remove ac power by turning off CB1 and disconnecting the ac plug.

NOTE If the PDP-8/E is rack-mounted, remove carefully and place on table.

- 2 Remove the power supply assembly from the chassis as follows:

- a. Remove five Phillips-head screws. Two are located on the front side of the chassis, one on the rear side, and two are located on the back side.

#### NOTE

# If the PDP-8/E is rack-mounted, the chassis tracks and the five mounting screws must be removed.

- b. Unplug the OMNIBUS power and switch power harness.

- c. Lift up the power supply and slide it back just far enough to remove the blue and the yellow power wires from the front panel.

- d. Lift out the power supply.

- 3 Remove the protective screen from the side of the power supply by removing the 12 countersunk screws on the screen.

- 4 Remove the heat sink assembly as follows:

- a. Remove the nylon plug from the heat sink assembly bracket.

- b. Remove the six screws from the heat sink assembly bracket.

- c. Lift out the heat sink assembly.

- 5 During replacement, the yellow wire goes to the top tab terminal of the front panel.

#### 4.5.6 Validation Tests

If a defective module is replaced by a new one while repairs are being made, tag the defective module noting the nature of the failure. When repairs are completed, ascertain that the repairs have resolved the problem.

To confirm that repairs have been completed, run all tests that originally exhibited the problem. If modules have been moved during the troubleshooting period, return all modules to their original positions before running the validation tests.

#### 4.5.7 Log Entry

A log book is supplied with each PDP-8/E System. Corrective maintenance is not complete until all activities are recorded in the log book. Record all data indicating the symptoms given by the fault, the method of fault detection, the component at fault, and any comments that would be helpful in maintaining the equipment in the future.

The log book should be maintained on a daily basis, recording all operator usage and preventive maintenance results.

#### 4.6 CPU TROUBLESHOOTING

After it is established that the CPU is causing the problem (Figure 4-1), Table 4-3 can be used as a troubleshooting aid to isolate the problem. The symptoms and causes are examples that may help the computer technician to find the area in which to look, once an abnormal indication is noted on the Programmer's Console.

When troubleshooting the PDP-8/E, remember that the OMNIBUS is designed so that all pins that are lettered the same are connected to each other, and that a signal can be provided from more than one place. An example is MD6, which is on pins BM1 of all slots of the OMNIBUS. The source of MD06 can come from either the Major Register module (M8300) or the Sense/Inhibit module (G104) and is used by five of the nine modules in the basic computer. To find the source and destination of all the signals used in the basic computer, refer to Appendix B.

#### 4.7 MEMORY TROUBLESHOOTING

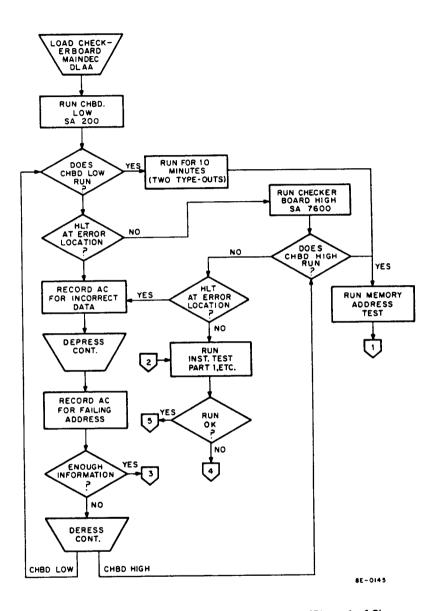

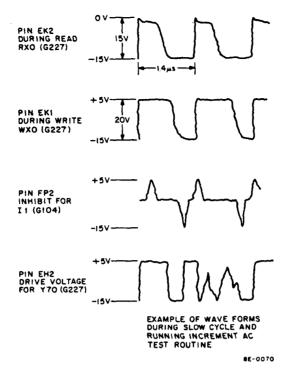

After it is established that the memory is the source of the problem through symptom analysis using the system troubleshooting flowchart (Figure 4-1), the memory troubleshooting flowchart (Figure 4-4) and associated troubleshooting Tables 4-4 and 4-5 and waveforms in Figure 4-5 may be used to isolate the problem.

Figure 4-4 Memory Troubleshooting Flowchart (Sheet 1 of 2)

Figure 4-4 Memory Troubleshooting Flowchart (Sheet 2 of 2)

#### 4.7.1 Memory Resistance Checks

There are also some resistance checks that can be performed to aid in isolating a trouble in the memory. These resistance checks are summarized below:

- 1 Turn power off.

- 2 Remove memory stack module.

- 3 Resistance of thermistor network is approximately  $150\Omega$ .

- 4 Resistance of individual thermistor when out of the circuit is approximately 56 $\Omega$ .

- 5 Resistance of winding for one bit is approximately  $3\Omega$  (for example, between pins FA and FB for bit 6).

- 6 Resistance of diodes FSA2501 is as follows: Forward approximately  $24\Omega$ ; Reverse approximately greater than  $1M\Omega$ .

#### CAUTION

Metal can transistors have their casing connected to the collector. Care should be exercised to prevent a ground lead or the back of another module from touching the metal can during troubleshooting.

| Item | Symptom                                                                                                                                                                             | Likely Cause                                                                                                                                                                                 | Module                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1    | A signal on the OMNIBUS is always low.                                                                                                                                              | Bus loads, diode from GND to the OMNIBUS is shorted.                                                                                                                                         | M8320                                             |

| 2    | Unable to start automatic<br>operations (run light always<br>off).                                                                                                                  | a. Missing MEM START L, which<br>is a 300 to 500 ns pulse for<br>everytime CONT, DEP, or<br>EXAM key is depressed.                                                                           | M8330<br>and<br>KC8-E                             |

|      |                                                                                                                                                                                     | <ul> <li>Power OK "delayed" or<br/>Power OK is true.</li> </ul>                                                                                                                              |                                                   |

| 3    | Unable to change Major<br>States.                                                                                                                                                   | Missing CPMA LOAD L. MA, MS<br>LOAD CONT L grounded.                                                                                                                                         | M8310                                             |

| 4    | Unable to modify any memory locations.                                                                                                                                              | <ul> <li>a. MB LOAD</li> <li>b. Memory direction always low</li> <li>c. INHIBIT always low</li> <li>d. WRITE L stays low</li> <li>e. SOURCE stays low</li> <li>f. FIELD L is high</li> </ul> | M8310<br>M8330<br>M8330<br>M8330<br>M8330<br>G104 |

|      |                                                                                                                                                                                     | (Refer to Table 4-4, Memory Data<br>Errors.)                                                                                                                                                 |                                                   |

| 5    | Data from memory is not getting to the MB.                                                                                                                                          | <ul> <li>a. Memory direction always high</li> <li>b. No MB LOAD L</li> <li>c. No TIME STROBE</li> <li>d. WRITE L staying high</li> </ul>                                                     | M8330<br>M8310<br>G104<br>M8330                   |

|      |                                                                                                                                                                                     | (Refer to Table 4-4, Memory Data<br>Errors.)                                                                                                                                                 |                                                   |

| 6    | When loading an address,<br>the word in the MA is not<br>the same as the Switch<br>Register.                                                                                        | LA ENABLE is always high (this<br>causes the switch register to be<br>ORed with AC, MQ, or STATUS<br>if the rotary switch is in one of<br>these positions).                                  | KC8-E                                             |

| 7    | When using LOAD ADDR,<br>DEPOSIT, or EXAM, the<br>MA changes to an incorrect<br>value (EX:0020 $\rightarrow$ 0634).                                                                 | ENO, EN1, EN2 or LEFT L,<br>RIGHT L, TWICE L are an incorrect<br>level. Refer to truth table on M8310<br>logic print, sheet 3 of 3.                                                          | M8310                                             |

| 8    | Depressing ADDR LOAD<br>key will enter all 1s in the<br>MA. By examining and<br>observing the MD, it will<br>be noted that the register<br>will change when the key<br>is released. | DATA T always high.                                                                                                                                                                          | M8310                                             |

.

# Table 4-3 Processor Troubleshooting

# Table 4-3 (Cont) Processor Troubleshooting

| Item | Symptom                                                                                                 | Likely Cause                                                                                   | Module                  |

|------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|

| 9    | The MA decrements when doing an EXAM or DEPOSIT.                                                        | DATA F is always low. Refer to truth table on M8310 logic print, sheet 3 of 3.                 | M8310                   |

| 10   | When doing an EXAM,<br>DEPOSIT, CONTINUE,<br>or a JUMP instruction,<br>the MA bits 0 – 4 are<br>zeroed. | PAGE Z L is high. (If just one of MA 0 → 4 check PAGE Z circuit on M8300.)                     | M8310<br>M8300          |

| 11   | CPMA, MB, PC, or AC do not increment.                                                                   | CAR IN L is always high to the adder. It should be generated for:                              | M8310                   |

|      |                                                                                                         | a. During TS1 with DEPOSIT,<br>EXAM, or EX TO LOAD de-<br>pressed.                             |                         |

|      |                                                                                                         | b. TS1 of FETCH state.                                                                         |                         |

|      |                                                                                                         | c. TS2 of DEFER state.                                                                         |                         |

|      |                                                                                                         | d. EXECUTE state and TS2 of<br>an ISZ, or TS3 of a JMS.                                        |                         |

|      |                                                                                                         | e. TS3 of a Group 2 OPR instruc-<br>tion.                                                      |                         |

|      |                                                                                                         | f. If SKIP is set: TS2 of<br>EXECUTE doing a JMS, or TS4<br>of a MRI.                          |                         |

| 12   | Unable to SKIP on an ISZ instruction.                                                                   | a. SKIP F/F will not clear.<br>b. No "carryout".<br>c. No "overflow".                          | M8310                   |

| 13   | Information being read<br>from Teletype is loading<br>into MA and PC.                                   | C2 L is always low, which causes PC<br>LOAD at BUS STROBE (TP3) time<br>instead of AC loading. | M8320<br>M8310<br>M8330 |

.

| Symptom          | Cause                        | Module | Check                               |

|------------------|------------------------------|--------|-------------------------------------|

| One Bit = 1 OR 0 | Inhibit Driver               | G 104  | Collector of 2007 transistors       |

| One Bit = 1 OR 0 | Sense Amplifier              | G104   | E31-42 Pin 8                        |

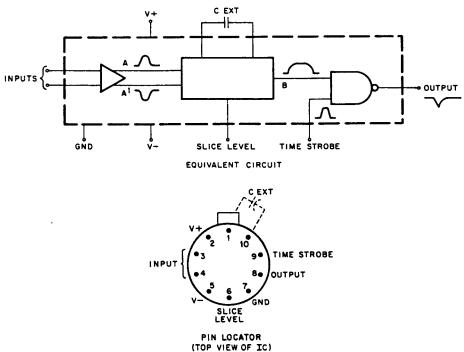

| Random = 1 OR 0  | Time Strobe                  | G104   | E9-3                                |

| Random/All = 0   | XY current/voltage is low    | G227   | ≈5.3V across +5V and Pin JU2        |

| Random/All = 1   | XY current/voltage is high   | G227   | Same as above                       |

| Random/All = 1   | Slice voltage low            | G 104  | ≈5.3V across GND and test point DA1 |

| Random/All = 0   | Slice voltage high           | G104   | ≈5.3V across GND and test point DA1 |

| Random/All = 1   | Inhibit current/voltage low  | G227   | – 15 Vdc power                      |

| Random = $0$     | Inhibit current/voltage high | G227   | - 15 Vdc power                      |

Table 4-4

Memory Data Errors – Possible Causes

|               | Table 4-5         |         |        |

|---------------|-------------------|---------|--------|

| Memory Module | <b>Test Point</b> | Voltage | Levels |

| Signal          | Pin               | Module | Approximate<br>Readings |

|-----------------|-------------------|--------|-------------------------|

| Current Control | HA1               | G104   | 1.2V                    |

|                 | HV2               | G104   | 2.3∨                    |

| Current Source  | JU2               | G227   | 1.4V                    |

|                 | FU2               | G104   | 0.25∨                   |

| Test Point      | DA1               | G104   | -5.3V                   |

| Test Point      | CB1               | G104   | 6∨                      |

| Test Point      | DB1               | G104   | -6V                     |

| Current Source  | HU2               | G104   | 4∨                      |

|                 | FA1               | G104   | 2.3∨                    |

|                 | FB1               | G104   | -4V                     |

|                 | Q17 Emitter       | G104   | -4.8V                   |

| Memory Stack    | Top of Thermistor |        | 2.5V                    |

| Test Points     | Q18 Collector     | G104   | -6V                     |

|                 | Q15, 16 Emitter   | G104   | +3V                     |

|                 | Q13 Base          | G104   | +1.3V                   |

Figure 4-5 Memory Waveforms

#### 4.7.2 Memory Circuit Variables

There are a number of variables in the MM8-E memory system such as current, slice, and field, that have to be set properly. Although some of the settings are permanent for a particular board, interchangeability in the field is assured. These variables are summarized in Table 4-6 and detailed in the following paragraphs.

| Variables on MM8-E<br>Memory System | Means for Settings                                | Location | Who Makes the Settings   |

|-------------------------------------|---------------------------------------------------|----------|--------------------------|

| Field Select                        | 3 Jumpers<br>EMA0, EMA1, EMA2                     | G 104    | Factory or Field Service |

| Strobe                              | 6-position rotary switch                          | G 104    | Factory or Field Service |

| Slice                               | 2 Jumpers – SLA, SLB                              | G 104    | Factory only             |

| X/Y Current Control                 | 2 Jumpers – CCA, CCB                              | G227     | Factory only             |

| Temperature Tracking                | Thermistor-Resistor Combination<br>RT, R1, R2, R3 | G619     | Factory only             |

Table 4-6 Memory Circuit Variables

#### 4.7.3 Field Select Jumpers

The octal combination of the appropriate *cut* jumpers represents the selected field; therefore, for the basic system (no extended memory), all jumpers must be in place.

#### 4.7.4 Strobe Adjustment

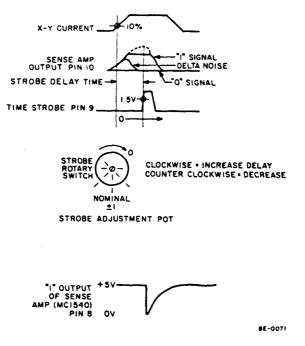

A 6-position rotary switch optimizes the strobe positioning in discrete steps of 10 ns. For detailed setting procedures, refer to Paragraph 4.7.9.

#### 4.7.5 Slice Level

Any variation on the +5V power supply will cause a proportional change of the absolute value of the slice level.

The slice level can be set to four different levels according to the following truth table:

| Jumpers |     | Slice Level             |

|---------|-----|-------------------------|

| SLA     | SLB | (Testpoint DA1 on G104) |

| In      | In  | -4.3V                   |

| Cut     | In  | -4.8V                   |

| In      | Cut | -5.3V                   |

| Cut     | Cut | -6.0V                   |

#### NOTE Do not field-adjust the slice level under any circumstances.

#### 4.7.6 X/Y Current Control (G227)

On the G227 module there are two jumpers in the upper center of the module. These jumpers can be removed and a 24 AWG wire loop soldered in their place if it is necessary to measure currents with a current probe.

The X/Y current control can be set to four discrete levels to calibrate the current source. The nominal voltage varies with temperature and its corresponding X/Y current is 370 mA measured on a loop between the X/Y drive and the stack board. The pertinent truth table follows:

| Jumpers |     | Current Control Voltage                |  |

|---------|-----|----------------------------------------|--|

| CCA     | ССВ | (Voltage across +5V and Pin JU2 on G22 |  |

| In      | In  | +3.7%                                  |  |

| In      | Cut | +2.2%                                  |  |

| Cut     | In  | Nominal (~3.5V at 25°C)                |  |

| Cut     | Cut | - 1.7%                                 |  |

NOTE Do not field-adjust current control voltage under any circumstances.

#### 4.7.7 Temperature Tracking

A thermistor-resistor combination on the memory stack board provides a temperature-sensitive voltage divider, which is connected to the current control circuit.

#### 4.7.8 Inhibit Current

The inhibit current is fixed; however, it varies proportionally to the -15V supply; its corresponding nominal value is 340 mA.

#### 4.7.9 Strobe Setting Procedure

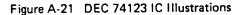

Setting the strobe properly is very important and must be done carefully. The chosen setting scheme makes this procedure relatively simple. Figure 4-6 illustrates the relation between X/Y current sense amplifier output and strobe.

Figure 4-6 Setting of Strobe

It is not advisable to set the strobe timing using an oscilloscope and a current probe. Because of the length of the current probe cables, the bandwidth of the probe and scope may vary in each case.

The resulting correlation error can exceed the tolerance allowed, resulting in a misadjusted memory. To set the strobe accurately, perform the following procedure at room temperature:

- 1 The switch has to be set to one of the three possible nominal positions (Figure 4-6).

- 2 Load "Memory Checkerboard" maintenance program and run it.

- 3 Program should run without error.

- 4 Halt program and delay strobe 10 ns (1 position clockwise), then restart.

- 5 If program still runs without error, proceed to the next position. When errors occur, stop and memorize this strobe position.

- 6 Repeat the same procedure advancing the strobe (counterclockwise) until errors occur, then stop and memorize this position.

- 7 A reliable system has to have a minimum of three working consecutive positions.

- 8 Finally set strobe to the middle working position. If there is an even number of working positions, favor the most delayed (clockwise) of the two center positions.

- 9 In checkout, "Checkerboard" should always run in the middle position and, for at least 15 minutes, in the positions to the left and right of middle with no errors.

- 10 Acceptance is to be run only in the final strobe position.

- 11 Setting strobe for extended memories, load basic memory checkerboard (MAINDEC-8E-D1AA-D) into extended fields and proceed to set strobe position according to Steps 1 through 10.

#### 4.8 H724 POWER SUPPLY TROUBLESHOOTING PROCEDURES

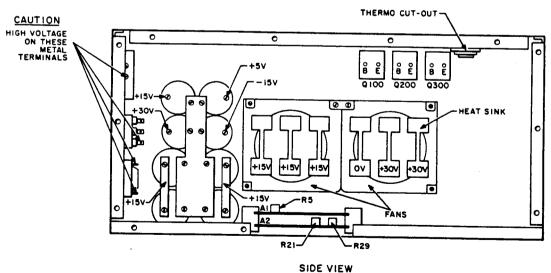

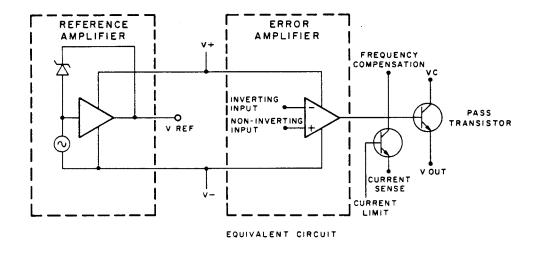

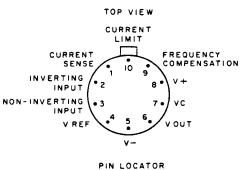

The H724 Power Supply provides power for CPU logic, the memory, bus loads, and the lamps on the Programmer's Console. If the power supply is established to be the source of the problem through symptom analysis with the aid of the system troubleshooting chart (Figure 4-1), voltage checks should be performed. Voltages and tolerances are given in Table 4-7. A component troubleshooting aid, Table 4-8, and parts location, Figure 4-7, are included as aids to isolating and correcting the malfunction.

The following paragraphs describe some of the power supply features and characteristics that can aid in isolating the malfunction.

| Output Voltage | Wire Color | Minimum<br>Voltage | Maximum<br>Voltage | Tolerance | Current Rating | Maximum<br>Ripple |

|----------------|------------|--------------------|--------------------|-----------|----------------|-------------------|

| +5V            | Red        | 4.85V              | 5.15V              | ± 3%      | 20A            | 50 mV p-p         |

| - 15V          | Blue       | - 14.25V           | - 15.75V           | ± 5%      | 8A             | 50 mV p-p         |

| +15V           | Orange     | 13.5V              | 16.5V              | ± 10%     | 1A             | 75 mV p-p         |

| +8V            | Yellow     | <b>6</b> ∨         | 10V                | ± 26%     | 2A             | 1                 |

| dc Volts OK    | Grey       | 3.75V              | 5V                 |           |                |                   |

| Overvoltage    | [          |                    | 6.5V               |           | }              | 1                 |

| Protection     |            |                    |                    |           |                |                   |

| 14 Vac         |            |                    |                    | ± 26%     | 0.2A           |                   |

| AC INTLK       |            |                    |                    |           | 0.12A          | Į                 |

## Table 4-7 H724 Power Supply Parameters

| Output<br>Volts        | Wire<br>Color | Jack & Pin           | Fuse<br>(amps) | Module | Transistors          | Adjustment                             | Use            |

|------------------------|---------------|----------------------|----------------|--------|----------------------|----------------------------------------|----------------|

| +5 Vdc                 | Red           | J3-3<br>J4-3         | 25             | A2     | Q200<br>Q201-6       | R21                                    | CPU<br>Logic   |

| - 15 Vdc               | Blue          | J3-4<br>J4-4<br>J6-3 | 10             | A1     | Q300<br>Q301<br>Q304 | R5                                     | Memory         |

| +15 Vdc                | Orange        | J3-5<br>J4-5         | 1              | A1     | Q100                 | R5                                     | Bus<br>Loads   |

| +8 Vdc                 | Yellow        | J6-4                 | 25             |        |                      |                                        | Lights         |

| 14 Vac                 | •             | J5-1<br>J5-3         | .5             |        |                      |                                        | Options        |

| Overvoltage<br>Protect | -             |                      |                | A2     |                      |                                        | Power<br>Surge |

| dc Volts OK<br>(3.75)  | Grey          | J3-6<br>J4-6         |                | A2     |                      | R29<br>(Factory<br>Adjustable<br>Only) | Power<br>Loss  |

Table 4-8 Component Troubleshooting Aid for H724 Power Supply

Static ohmeter reading of thermistor is approximately  $23\Omega$ .

8E-0072

Figure 4-7 H724 Power Supply

#### 4.8.1 Overcurrent Protection

The power supply should not be loaded by more than 175 percent of the rated output current (Table 4-7).

#### 4.8.2 Hold-Up Time

The regulated output voltages under maximum load conditions should remain stable for a minimum of 2 ms after loss of line voltage.

#### 4.8.3 Thermal Protection

A thermal switch is in series with the interlock circuit. This switch is located in the forward top section of the power supply (Figure 4-6). It will disconnect primary power at  $90^{\circ}$ C ±5°. The thermal switch must be reset manually if it is tripped.

#### 4.8.4 Contact Protection

Contact protection is provided to limit the primary power at the input to the convenience outlet to twice the nominal peak voltage. In addition, protection is provided against a rate of change in the voltage exceeding 10V/second as the solenoid or circuit breaker is opened.

#### 4.8.5 Input Switching

The primary power is switched by a 24 Vdc relay, controlled by an interlock circuit. Grounding pin A on the interlock panel will operate the solenoid and apply power to the computer. The solenoid will break both sides of the line.

#### 4.8.6 Power ON-OFF Switch Adjustment

The Power ON-OFF switch is cam-adjusted according to Table 4-9.

| Power<br>Switch | Three Cam-Operated Switches<br>Switch Position |              |  |

|-----------------|------------------------------------------------|--------------|--|

| Position        | Back 2 Switches                                | Front Switch |  |

| OFF             | ON                                             | OFF          |  |

| ON              | ON                                             | ON           |  |

| Panel Lock      | OFF                                            | ON           |  |

#### Table 4-9 Power ON-OFF Switch Adjustment

#### 4.8.7 Parallel Operation

Two or more power supplies must not be wired in parallel to extend the current driving capability.

#### 4.8.8 Large Configuration

When more than one box is in the sytem, the interlock panel is wired so that the front panel power switch of the first box and the thermal cut-out switch of each additional box are in series and will control power to all boxes, though they may be connected to independent primary power sources.

#### 4.9 H740 POWER SUPPLY TROUBLESHOOTING PROCEDURES

#### 4.9.1 Troubleshooting Rules and Precautions

Observe the following rules and precautions when maintaining the power supply.

- 1 Do not adjust voltages beyond their 105 percent rating; adjust slowly to avoid overvoltage crowbar that blows dc output fuses.

- 2 Use a calibrated voltmeter, preferably a digital voltmeter. Voltages should be adjusted to their center values: +15.0, +5.0, and 15.0, all under load at the dc cable termination.

- 3 Ensure that power is turned off and unplugged before servicing the power supply.

- 4 Ensure that input capacitors C1 and C2 are discharged before servicing the power supply. A 10 $\Omega$  to 100 $\Omega$ , 10W resistor can be used to hasten the discharge of the capacitors. (Ensure power is off.)

- 5 The dc regulator module is not internally grounded to the chassis. Therefore, shorts to ground can be located after disconnecting the dc output cable.

- 6 The dc output fuses, F1 and F2, can be replaced without removing the dc regulator module. Before unsoldering fuses, observe cautions described in 3 and 4.

- 7 For proper operation, all hardware must be secured tightly to about 12 inch pounds (i.e., capacitors, chokes, semiconductors). All hardware should be replaced with identical hardware replacement parts.

- 8 The dc regulator module can be removed from the top of the power chassis assembly while the latter is still bolted to the computer chassis. The dc regulator module is held in place by six screws.

- 9 When replacing power semiconductor components that are secured to the heat sink, apply a thin coat of Wakefield #128 compound or Dow silicone grease to heat sink contact side (bottom) of the semiconductor. Insulating wafers are not required.

#### 4.9.2 Troubleshooting Chart

The most likely source of a power supply malfunction is the dc regulator. A quick remedy for a malfunction is to replace this entire module. The problem, however, could be a short in the system unit or possibly a defective component or other problem in the ac input circuit. Table 4-10 applies to the regulator module and helps to isolate problems in this area.

| Problem                                                                     | Cause                                                                                                                                    |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| No +5V and +15V output                                                      | F1 opened<br>D14 or transformer opened<br>+5V adjusted too high (1)                                                                      |

| +5V output too low                                                          | Q5, D9, Q10, Q9, Q11, D12, or D10 shorted<br>C5 or C7 shorted<br>R49, R50, R46, or R44 opened                                            |

|                                                                             | Q6, Q7, Q8, or D11 shorted<br>A9, Q10, or D9 opened (1)                                                                                  |

|                                                                             | R51 or R50 opened                                                                                                                        |

| +15V output too hjgh                                                        | Q1 shorted<br>D8 opened<br>R35 or R36 opened                                                                                             |

| +15V output too low                                                         | Q3, Q4, Q5, or D8 shorted<br>R56, R35, or R34 opened<br>C19 shorted                                                                      |

| – 15V output too low                                                        | F2 opened<br>D14 or transformer opened<br>Q25, D4, Q26, Q21, Q27, D7 or D5 shorted<br>C14 or C12 shorted<br>R22, R26, R25, or R29 opened |

|                                                                             | Q22, Q23, Q24, or D6 shorted<br>Q25, Q26, or D4 opened<br>R26 or R27 opened (1)<br>- 15V adjusted too high (1)                           |

| AC LO L will not go high                                                    | Q13, Q14, or Q15 shorted<br>Q16 or D3 opened<br>R7, R3, R6, or R8 opened<br>C9 shorted                                                   |

| AC LO L will not go low<br>and/or acts erratically<br>on power-on/power-off | Q13, Q14, or Q16 opened<br>Q15 or D3 shorted<br>R12, R13, R7, or R10 opened                                                              |

Table 4-10 Regulator Module Troubleshooting Chart

#### SECTION 4 - TELETYPE MAINTENANCE

This section contains information pertinent to the maintenance of the TTY and associated control logic. Perform the test routines described in Paragraph 4.2 to localize trouble in the Teletype.

#### 4.10 SPECIAL TOOLS

Table 4-11 lists the special tools needed to maintain the 33 ASR Teletype. All of these items can be obtained from Digital Equipment Corporation or from Teletype Corporation.

#### 4.11 PROGRAMS

The Teletype control test referenced in Table 2-4 serves as an aid in maintaining the 33 ASR Teletype and associated control logic.

| ltem                    | Part No. |

|-------------------------|----------|

| Set of gauges           | 117781   |

| Offset screwdriver      | 94644    |

| Offset screwdriver      | 94645    |

| Handwheel               | 161430   |

| Handwheel adapter       | 181465   |

| Contact adjustment tool | 172060   |

| Gauge                   | 180587   |

| Gauge                   | 180588   |

| Gauge                   | 183103   |

| Bending Tool            | 180993   |

| Extractor               | 182697   |

| Tweezer                 | 151392   |

| Spring hook (push)      | 142555   |

| Spring hook (pull)      | 142554   |

| Screw holder            | 151384   |

# Table 4-11 Teletype Maintenance Tools

#### SECTION 5 - PREVENTIVE MAINTENANCE PROCEDURES

#### 4.12 PREVENTIVE MAINTENANCE

Teletype preventive maintenance should be scheduled every 3 months.

#### CAUTION

Do not use alcohol, mineral spirits, or other solvents to clean plastic parts with protective decorative finishes. Normally, a soft, dry cloth should be used to remove dust, oil, grease, or otherwise clean parts or subassemblies.

To clean plastic surfaces, we recommend using any of several household cleaner-waxer liquids. To clean the printer platen, we recommend a lacquer thinner.

During an overhaul, subassemblies and metal parts can be cleaned in a bath of trichlorethylene. Proper lubrication should be performed often.

#### 4.12.1 Weekly Tasks

The following procedures should be followed on a weekly basis.

- 1 Inspect platen and paper guides. Wipe clean, using a soft, dry cloth.

- 2 Clean external areas of paper-tape punch and reader, using a soft brush or cloth.

- 3 Remove and empty the paper-tape punch chad box.

- 4 Run the Teletype control test for approximately 15 minutes.

#### 4.12.2 Preventive Maintenance Tasks

Follow the procedure outlined below.

- 1 Inspect platen and paper guides. Clean platen, using a lacquer thinner to remove shiny surface.

- 2 Clean ribbon guides and replace ribbon, if necessary.

- 3 Remove cover and check for vibration effects, loose nuts, screws, retaining clips, etc.

- 4 Clear distributor rotor and clean disk surface, using cotton swab moistened in freon or trichlorethylene.

- 5 Clean between selector magnet-pole piece and armature with bond paper to remove any lubricant or dirt.

- 6 Clean and lubricate the Teletype, per Teletype Bulletin 273B. Follow instructions literally; do not over lubricate.

7 The following adjustments should be checked. Pages indicated are in Bulletin 273B, Volume 2.

| Trip Shaft                 | 574-122-700 Page 13     |

|----------------------------|-------------------------|

| Trip Lever                 | 574-122-700 Page 14     |

| Brush Holder (Distributor) | 574-122-700 Page 15     |

| Clutches                   | 574-122-700 Pages 16-24 |

| Code Bar Reset             | 574-122-700 Pages 30-34 |

| Print Suppression          | 574-122-700 Page 35     |

| Blocking Levers            | 574-122-700 Page 37     |

| Print Suppression          | 574-122-700 Page 43     |

| Carriage Drive Bail        | 574-122-700 Page 44     |

| Print Trip Lever           | 574-122-700 Pages 61-62 |

| Dashpot                    | 574-122-700 Page 78     |

| Final Printing Alignment   | 574-122-700 Page 85     |

| Line Feed                  | 574-122-700 Pages 89-95 |

| Keyboard Trip Lever        | 574-122-700 Page 141    |

| Reader Trip Lever          | 574-124-700 Pages 6-9   |

| Detent Lever               | 574-124-700 Page 10     |

| Sensing Pin                | 574-124-700 Page 15     |

| Tape Lid Latch Handle      | 574-124-700 Page 18     |

| Feed Pawl                  | 574-125-700 Page 11     |

| Registration               | 574-125-700 Page 12     |

|                            |                         |

- 8 Run each of the Teletype MAINDEC Programs; at least two passes each.

- 9 Check that tape holes are being punched cleanly.

ана алана алан

•

#### **SECTION 6 - CORRECTIVE MAINTENANCE**

#### 4.13 CORRECTIVE MAINTENANCE PROCEDURES

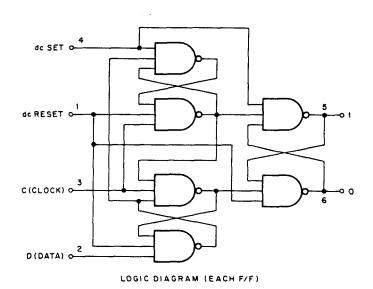

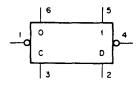

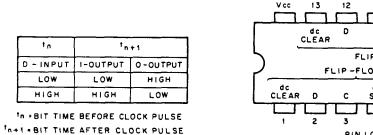

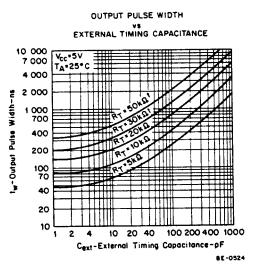

Details of the cable connector fusing and test points are included in Tables 4-12 and 4-13. During off-line operation, the keyboard distributor effectively drives the printer selector magnet; thus, any character received from the keyboard or paper-tape reader is automatically reproduced on the printer and paper-tape punch. During on-line operation, this continuity is broken and a Teletype receiver (M8650) is used to accept the input from the reader or keyboard while a Teletype transmitter (M8650) is used to drive the printer and paper-tape punch.

|            | Pin No.                          | Split Lug                                         |                                                                                                                               |                                                                                                                                                                                                                                                   | Advance                                                                                                                                                         |

|------------|----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 1 (N/C)                          | 0 (N/C)                                           |                                                                                                                               |                                                                                                                                                                                                                                                   |                                                                                                                                                                 |

| 6          | 2                                | 2                                                 |                                                                                                                               | ×                                                                                                                                                                                                                                                 |                                                                                                                                                                 |

| 3          | 3                                | 3                                                 | x                                                                                                                             | 1                                                                                                                                                                                                                                                 | 1                                                                                                                                                               |

| – Relay    | 4                                | 4                                                 |                                                                                                                               | 1                                                                                                                                                                                                                                                 | ×                                                                                                                                                               |

| 7          | 5                                | 5                                                 |                                                                                                                               | X                                                                                                                                                                                                                                                 |                                                                                                                                                                 |

| +Relay     | 6                                | 6                                                 |                                                                                                                               |                                                                                                                                                                                                                                                   | ×                                                                                                                                                               |

| 4          | 7                                | 7                                                 | x                                                                                                                             |                                                                                                                                                                                                                                                   | }                                                                                                                                                               |

| -30V (N/C) | 8 (N/C)                          | 0 (N/C)                                           |                                                                                                                               |                                                                                                                                                                                                                                                   |                                                                                                                                                                 |

|            | 3<br>- Relay<br>7<br>+Relay<br>4 | 6 2<br>3 3<br>- Relay 4<br>7 5<br>+Relay 6<br>4 7 | 6     2     2       3     3     3       - Relay     4     4       7     5     5       + Relay     6     6       4     7     7 | 6         2         2           3         3         3         X           -Relay         4         4         4           7         5         5         5           +Relay         6         6         4           4         7         7         X | 6     2     2     X       3     3     3     X       -Relay     4     4     X       7     5     5     X       +Relay     6     6     X       4     7     7     X |

Table 4-12 Connections of TTY Cable

|     | ٦        | able 4- | 13  |                    |

|-----|----------|---------|-----|--------------------|

| ΤΤΥ | Cabling, | Fusing  | and | <b>Test Points</b> |

| Check        | Reader         | Receiver                | Transmitter     |

|--------------|----------------|-------------------------|-----------------|

| Fuses        | .1/2A          |                         | 3, 3/8, 2.5, 3A |

| Terminal No. | 6 and 4        | 7 and 3                 | 5 and 2         |

| Test Points  | DA1 Reader Run | AB1 Receiver Active '1' |                 |

A crystal clock is used to shift the bits through the transmitter and receiver buffers; therefore, no clock adjustments are required. Most Teletype problems can be traced to one of three areas:

- a. 33 ASR keyboard or reader

- b. 33 ASR printer or punch

- c. M8650 receiver/transmitter

Isolation of bit-related problems is relatively simple. Off-line duplication can usually determine whether the problem is in the teleprinter or the control logic. Steps may be taken to isolate the problem to subassemblies within the teleprinter. Picking up bits during a read operation can be caused by a defect in any of three sets of contacts that are tied in parallel. Reader, keyboard, and answer-back contacts provide parallel inputs to the distributor contact disk. Bit pick-up problems can be isolated to one of these three areas by disengaging the related contact from the suspected contact set.

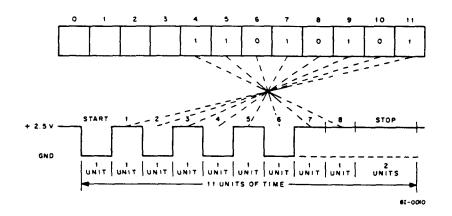

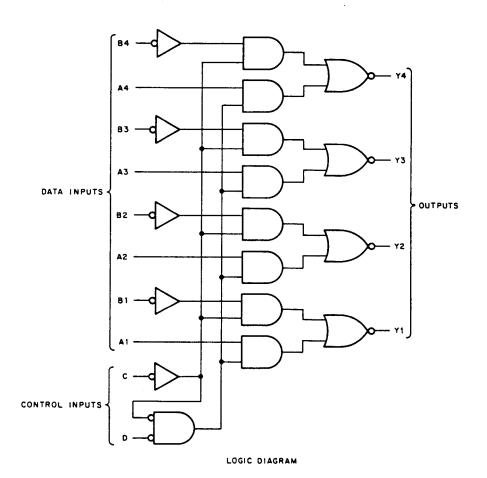

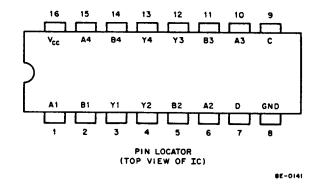

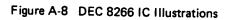

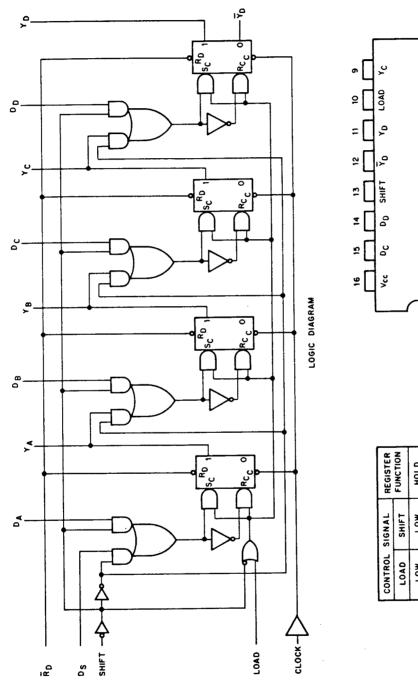

Printer/punch problems can sometimes be isolated by comparing the printed character with the output of the paper-tape punch. If the printed character agrees with the punch output, and both are incorrect, then the problem lies in the selector mechanism or in the TTY receiver/transmitter module (M8650). If the printed character and the paper-tape punch output disagree, and the paper-tape punch output is correct, then the problem lies within the printer assembly. Figure 4-8 shows the Teletype signal relationship between the computer and the Teletype.

Figure 4-8 Teletype Signal Waveform and Bit Relationship for the Character "U"

## SECTION 7 - I/O CABLE TROUBLESHOOTING

#### 4.14 I/O AND BREAK CABLES

Pin assignments for the positive I/O adapter module and break are provided in Figure 9-20 of the PDP-8/E & PDP-8/M Small Computer Handbook. The figure provides a source and destination in the event that cable troubleshooting is necessary.

#### SECTION 8 - SPECIAL TROUBLESHOOTING PROCEDURES

#### 4.15 TEST CLOCK (M499)

The test clock module serves as a troubleshooting tool for the PDP-8/E when problems with memory prevent the use of troubleshooting programs. The M499 module provides a MEM START signal of 100-500 ns width every 15  $\mu$ s with the DEP or EXAM key depressed. This procedure makes signals available for associated troubleshooting at a continuous rate. Troubleshooting procedures using the M499 Test Clock are as follows:

- 1 Insert M499 into any slot in row A of PDP-8/E OMNIBUS.

- 2 Depress the SING STEP key on the Programmer's Console.

- 3 The Switch Register may now be used in conjunction with the EXAM or DEP key to scope manual functions.

- 4 The EXAM or DEP key may be taped into the depressed position (thus leaving the operator free).

#### SECTION 9 - PREPARATION FOR RESHIPMENT

#### 4.16 RESHIPMENT

If the computer must be moved to a location far removed from the original installation, good packaging procedures should be followed. If the original packing materials have been retained, the instructions given below will ensure that the computer is transported safely.

- 1 Disconnect the computer and remove it from its enclosure.

- 2 If the computer is a PDP-8/F or PDP-8/M, remove the chassis tracks and ship them separately; remove the filter from the side of the computer. If the computer is a PDP-8/E table-top model, remove the air filter from both sides of the super cover and ship them with cables, software, manuals, etc.

- 3 Roll the power cord and tape it to the rear of the computer.

- 4 Place the computer in a polyethylene bag and seal the bag with tape.

- 5 Use the original packing materials to pack computer and accessories snugly in an inner carton.

- 6 Seal the inner carton, place the inner carton in an outer carton, and seal the outer carton.

### CHAPTER 5 SPARE PARTS

#### 5.1 INTRODUCTION

This chapter lists the recommended spares for the PDP-8/E, PDP-8/F, and PDP-8/M basic computers and for the 33 ASR Teletype. Two levels of spares are recommended, viz., "Remove and Replace at the Module Level" and "Remove and Replace at the Component Level".

#### 5.2 PDP-8/E SPARES

#### 5.2.1 PDP-8/E First-Level Spares

First-level spares for the PDP-8/E basic computer, which are included in spare parts option kit SP8-EA, are listed in Table 5-1. Table 5-2 lists those parts that are not recommended as spares. Additional spares may be purchased separately.

| Part No.  | Description                    | Quantity |

|-----------|--------------------------------|----------|

| M8300     | M8300 Major Registers Module   |          |