### CHAPTER 2

## LOGICAL FUNCTIONS

Both manual and stored-program operations of the PDP-8 are necessary to perform any complete task. The data break is the only fully automatic operation. Manual operation is normally limited to storing a Readin Mode or Binary Loader program, modifying or examining data or addresses in a prestored program, or establishing the starting conditions and initiating programmed operation of the system. Stored program operation is used in the performance of all user programs. However, for maintenance purposes and to facilitate the debugging of a new program, provision is made for manually advancing the program one cycle at a time or one instruction at a time.

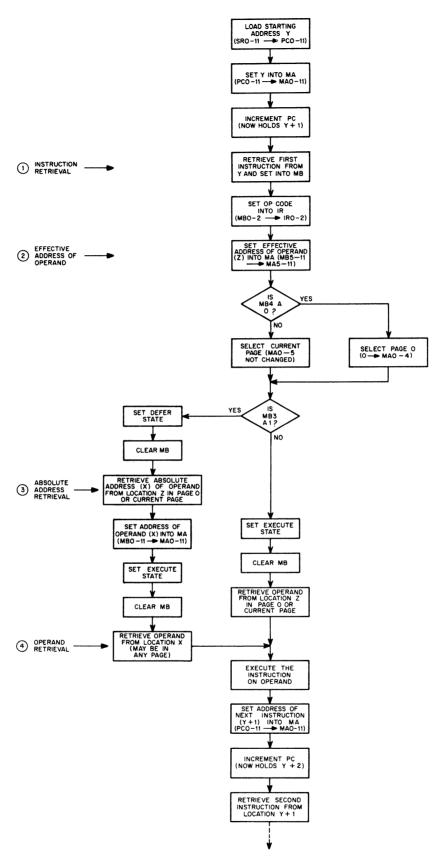

The sequence in which operations occur during manual operation or during each machine cycle for stored program and automatic operation appears on the flow diagram, engineering drawing FD-D-8P-0-7.

### FLOW DIAGRAM INTERPRETATION

The flow diagram illustrates the sequence of events that take place during each of the possible manual, stored program, or automatic operations. Sheet 1 of the flow diagram, containing all functions except manual operations, consists of six vertical columns. The first three columns correspond to one of the three major states in programmed operation: fetch (F), defer (D), and execute (E). The last three columns correspond to automatic operations during a data break and are represented by the word count (WC), current address (CA), and break (B) major states. Sheet 2 of the flow diagram contains the events that take place during manual operation. Horizontal rows on the flow diagram represent time states. Time proceeds from top to bottom on this diagram. The upper row represents the memory strobe during programmed and automatic operation, and represents time state SPO during manual operation.

horizontal line to the rectangle specifies the next common event. Thus, the separate sequences associated with manual deposit and examine operations each conclude with the sequence 1 —— MEM START, 1 —— RUN, and 1 —— RUN STOP.

Note that some events specified in the rectangles of the flow chart are conditional, others unconditional. Unconditional events appear as information transfer statements with no indication of register content. For example, key operations begin with the event  $0 \longrightarrow RUN$  which occurs in time state SPO, and during a load address operation the PC clears in time state SP1. Conditional events appear as information transfer statements accompanied by one or more indications of the contents of a register. For example, during a group 1 OPR instruction, several conditional events may occur, and these appear in the leftmost sequence in time T1. The first event,  $+1 \longrightarrow PC$ , is unconditional. The second event,  $0 \longrightarrow AC$ , occurs only if MB bit 4 contains a 1 and MB bit 6 contains a 0. When following the sequence of events in any given instruction, conditional events for which the required conditions are not met should be ignored.

To find the exact mechanism by which the processor executes an event specified in the flow diagram refer to the appropriate engineering logic diagram and the corresponding circuit description. When tracing a transfer operation, first examine the input and control gating of the register to which the transfer is being made. Thus, to trace the operation +1 — PC, first examine the logic diagram of the PC register: a command pulse designated +1 — PC strobes a set of input gates. To find how this pulse generates, examine the logic drawing of the PC control. When there is doubt where a pulse or level generates, consult Appendix 1. This appendix lists all command and control signals in alphanumerical order of designation, as well as the number of the engineering drawing on which the circuits which generate any given signal appear.

NOTE: It is very important that maintenance personnel familiarize themselves with the flow diagram of the PDP-8. This flow diagram is the key to understanding system operation, and provides much information valuable in trouble-shooting.

#### PREFATORY OPERATIONS

#### POWER and PANEL LOCK Switches

Primary power flows to the computer from the POWER and PANEL LOCK switches. With the PANEL LOCK switch in the unlocked (counterclockwise) position, turning the POWER switch to the clockwise position applies primary power to the computer. When a stored program is running, placing the PANEL LOCK

switch in the locked (clockwise) position disables the POWER switch to prevent primary power from being accidentally turned off. The PANEL LOCK switch also disables all manual keys except the SWITCH REGISTER, to prevent accidental distribunce of the program.

### Power Clearing

When primary power is first applied, the capacitors of the power supply take an appreciable time to charge to the +10v and -15v levels. The processor logic circuits become operative before the supplies stabilize, but the +40v memory supplies are inhibited until the OK LEVEL relay driver in the power supply generates a negative OK level, usually when the potential on the -15v line reaches -14v. During the rise period, the  $\overline{OK}$  ground level enables a 100-kc clock generating PWR CLR pulses to clear the RUN flip-flop, all the memory control flip-flops, and the Teletype control and register flip-flops. A PWR CLR pulse also generates when the START key is pressed. These PWR CLR pulses are also available at the interface to clear the registers of I/O devices. When the negative OK level appears, the 100-kc clock disables and the computer and I/O devices clear for operation.

#### MANUAL OPERATIONS

Keys and switches on the operator console have three functions: they permit information to be stored in core memory; they permit the contents of a specified core memory cell to be displayed for visual examination; and they permit a program to be started and stopped. Operation of the START, LOAD ADD (load address), DEP (deposit), EXAM (examine), or CONT (continue) keys causes the special pulse generator to generate four special pulse (SP) time states during which all manual operations occur. These five keys clear the RUN flip-flop during time state SPO, preventing or interrupting programmed or automatic operation. Operation of the START or CONT keys sets the RUN flip-flop to 1 during time state SP3 so that the processor begins programmed operation at the conclusion of the time state.

# LOAD ADD Key

Before any program can be loaded or executed, the operator must set the starting address into the program counter (PC). Pressing the LOAD ADD (load address) key generates a KEY LOAD ADDRESS signal which starts the special pulse generator and prevents the RUN flip-flop from being set to 1 at the end of the special pulse cycle. During time state SP0, the RUN flip-flop clears. During time state SP1, the PC clears. During time state SP2, the contents of the switch register (SR) are set into the PC. If the memory extension control is in use, the contents of the INST FIELD (instruction field) switches are also set into the instruction field register (IF) and the contents of the DATA FIELD switches are set into the data field register (DF).

## START Key

The START key initiates execution of a program which has been loaded into core memory. Pressing the key generates the KEY ST+EX+DP (key start OR examine OR deposit) level which starts the special pulse generator. During the cycle of the special pulse generator, the following sequence of events takes place:

- 1. During time state SPO, the RUN flip-flop clears, ensuring that the program does not start prematurely.

- 2. During time state SP1, the accumulator (AC), link (L), memory buffer register (MB), instruction register (IR), and interrupt control flip-flops clear. During this time state, the major state generator is set to fetch, and the contents of the PC jam-transfer into the memory address register (MA). At the end of this time state, the processor is ready to execute the first instruction and the PC contains the starting address.

- 3. During time state SP2, a MEM START pulse generates, setting the MEM ENABLE flip-flop and starting the memory timing circuits.

- 4. During time state SP3, the RUN flip-flop is set to 1. Programmed operation now initiated, the processor executes successive instructions until it encounters a halt command.

### CONT Key

The CONT (continue) key permits a program which has temporarily halted to be restarted. Pressing this key clears the RUN flip-flop during time state SPO, generates T2B and MEM START signals during time state SP2, and sets the RUN flip-flop to 1 during time state SP3. Since operation of this key does not clear or in any way change the contents of any register, it initiates execution of the program from the conditions that currently exist.

## **DEP** Key

Lifting the DEP (deposit) key causes the contents of the SR to deposit in memory at the address specified by the current program count. The contents of the PC then increment to permit repeated operation of the DEP key to store information at consecutive memory addresses. Note that a load address operation that sets the starting address into the PC must always precede the initial deposit operation. If the addresses at which information is to be deposited are not consecutive, a load address operation must precede each deposit operation. Pressing the DEP key initiates the following sequence of events:

- 1. During time SPO, the RUN flip-flop clears.

- 2. During time SP1, the AC, MB, and IR clear. The major state generator is set to the execute state, the contents of the PC transfer into the MA, and the contents of the PC then increment

- 3. During time state SP2, the operation code for the DCA instruction  $(3_8)$  is set into the IR, the contents of the SWITCH REGISTER (SR) transfer into the AC, and a MEM START signal generates.

- 4. During time state SP3, the RUN flip-flop is set to 1, but is immediately reset to 0 by a T1 pulse, starting the execute cycle of the DCA instruction but ensuring that the CP halts at the end of the cycle.

- 5. The memory strobe is disabled so that the contents of the MB remain 0 until time state T1 of the execute cycle, when the contents of the AC transfer to the MB and the AC then clears.

- 6. During time state T2, the 0 state of the RUN flip-flop inhibits generation of the T2B pulse.

## **EXAM** Key

Pressing the EXAM (examine) key causes the contents of the memory cell specified by the contents of the PC to transfer into the MB and AC for visual examination. The contents of the PC then increment so that repeated operation of the EXAM key permits examination of the contents of consecutive memory locations. Note that a load address operation must precede the first examine operation. To examine several non-consecutive memory cells, separately specify each location by a load address operation. When the EXAM key is pressed, the following sequence occurs:

- 1. In time states SPO and SP1, the sequence is the same as that initiated by the DEP key.

- 2. In time state SP2, the operation code for TAD  $(1_8)$  is set into the IR, and a MEM START signal generates.

- 3. When the memory strobe pulse occurs, the contents of the specified memory cell read into the MB. During time state T1 of the execute cycle, a HALF ADD command pulse generates to transfer binary 1's from the MB into the corresponding bits of the AC.

- 4. During time state T2, an AC CARRY command generates which propagates carries in the AC. (Since the AC was cleared during time SP1, carries cannot occur during an examine operation.)

- 5. Finally, the 0 state of the RUN flip-flop inhibits generation of a T2B pulse.

## STOP Key

Pressing the STOP key can halt a program at any moment. Operation of this key generates a negative RUN STOP level which clears the RUN flip-flop at the next T1 pulse. The RUN (0) level inhibits the generation of timing pulse T2B, preventing clearing of the MB and MA. Thus, the program stops just before the end of the current cycle to permit visual examination of various registers.

## SING STEP and SING INST Keys

Pressing the SING STEP (single step) or SING INST (single instruction) keys steps a program one cycle or one instruction at a time, respectively. When the SING STEP key is in the up position, a negative RUN STOP level generates. Operating the CONT key sets the RUN flip-flop to 1 during time SP3 of the key cycle, and the flip-flop clears at the next T1 pulse so that processor operation halts at the end of the cycle. Thus, repeated operation of the CONT key advances the program one cycle at a time. When the SING INST key is in the up position, the RUN STOP level does not generate until an F SET level also occurs. The F SET level generates during the last cycle of the current instruction, and the processor operation halts at the end of that cycle to permit register examination.

#### PROGRAMMED OPERATION

The normal mode of PDP-8 operation is execution of a prestored programmed instruction sequence. A program interrupt can modify programmed operation, or a data break can temporarily suspend programmed operation. A program interrupt transfers program control from the main program to a subroutine to effect an information transfer with an I/O device or peripheral equipment. A data break is an automatic operation suspending the main program for one or three cycles to permit a high-speed I/O device to exchange information with the core memory.

### Instructions

The following explanations of the functions performed during the execution of each instruction assume that the PDP-8 is energized and is operating normally under control of the main program. Each explanation begins at the start of the fetch cycle, when the address of the instruction is in the MA and a memory read operation is initiated.

Instructions performed by the PDP-8 are either memory reference instructions or augmented instructions. A memory reference instruction contains an operation code (in bits 0 through 2) and an address in core memory at which the operation is to occur (in bits 3 through 11). An augmented instruction is used when the operand is already in a register such as the AC; in this case, no memory address is required. Bits 0 through 2 of an augmented instruction contain the operation code which determines the general class of the instruction. Bits 3 through 11 of the instruction contain information which permits the required operations to occur during the two or three execution time states of a single (fetch) cycle. Operations performed in this manner are said to be "microprogrammed," since several such operations may take place during a single instruction.

### Memory Reference Instructions

The format of a memory reference instruction appears in Figure 1-3(a). Instructions which reference a memory address in page 0 or in the current page occur in two cycles: fetch and execute. Instructions which reference any other page require three cycles: a fetch cycle in which the instruction word is brought out of memory and contains the effective address of the operand in the current page or page 0; a defer cycle, in which the absolute address of the operand is brought out of memory and enters the MA; and the execute cycle, in which the operand is brought out of core memory and operated on.

The following explanations of memory reference instructions assume that the instruction is directly addressed and that no break request has been initiated during its execution. (Explanations of the defer cycle and the break cycle follow the explanations of augmented instructions.)

<u>Logical AND (AND)</u> - The logical AND operation occurs between the contents of the addressed memory cell and the contents of the AC through a transfer of binary 0's. The result is stored in the AC and the operand is restored to memory. The original contents of the AC are lost.

First, the instruction is read into the MB from the addressed cell. Then, since no interrupt has been acknowledged, the operation code  $(0_8)$  in bits MB0 through MB2 is set into the IR. In fact, since the IR cleared at the end of the previous cycle and the operation code is 0, there is no change in the IR status. The 0 levels of the IR flip-flops decode to produce an AND level used in the control gating circuits. The following sequence of events then occurs:

- 1. During time state T1, the contents of the PC increment by 1.

- 2. The instruction rewrites into the same core memory location.

- 3. At the beginning of time state T2, the contents of bits MB5 through MB11 jamtransfer into the corresponding bits of the MA.

- 4. If bit MB4 contains a 0 and bits MA0 through MA4 are cleared, the addressed cell is in page 0 of core memory. If bit MB4 contains a 1, the addressed cell is in the current page at the location specified by the contents of bits MA0 through MA4.

- 5. Since bit MB3 contains a 0 (indicating direct addressing) and the instruction is not JMS, the MB clears and the major state generator is forced to the execute state.

- 6. The last timing pulse of the cycle, T2B, generates a MEM START pulse which initiates a new read operation. This is the end of the fetch cycle. The PC contains the address of the next instruction; the MA holds the address of the operand; the IR contains the operation code of the current instruction; the MB contains all 0's; and the major state generator is set to execute for the next cycle.

During the memory strobe portion of the execute cycle, the operand reads into the MB. No action occurs during time state T1; the instruction is restored in core memory. During time state T2, the following sequence takes place:

- 1. The logical AND operation occurs through a transfer of binary 0's from the MB to the corresponding bits of the AC. Bits of the AC which were in the 0 state before the transfer remain in the 0 state. Bits of the AC which were in the 1 state before the transfer remain in the 1 state only if they correspond to MB bits in the 1 state.

- 2. The MB clears.

- 3. Since there is no break request, the contents of the PC jam-transfer into the MA, the IR clears, and the major state generator is set to fetch. This concludes the logical AND operation; the program is ready to fetch the next instruction from the location specified by the contents of the MA.

Two's Complement Add (TAD) - The contents of the addressed memory cell add to the contents of the AC in 2's complement arithmetic. The result of the addition is stored in the AC, and the operand (addend) is restored to memory. The original contents of the AC are lost.

During the memory strobe portion of the fetch cycle, the instruction word is read into the MB from the memory cell specified by the current contents of the MA. Then, since no program interrupt has been

acknowledged, the operation code (1<sub>8</sub>) in bits MBO through MB2 is set into the IR. The 1 and 0 levels of the IR flip-flops are decoded to produce a TAD gating level. Operations during the fetch cycle of a TAD instruction are identical to those during the fetch cycle of an AND instruction.

During the memory strobe portion of the execute cycle, the addend reads into the MB from the addressed memory cell. The following sequence of events then takes place:

- 1. During time state T1, a half-add operation occurs, in which MB bits in the 1 state cause corresponding bits of the AC to complement.

- 2. The operand is restored in core memory.

- 3. During time state T2, carries are propagated in the AC. If there is an overflow from bit ACO, the link complements. Therefore, the normal practice is to follow a TAD instruction by a test for link status.

- 4. The MB clears.

- 5. Since there is no data break request, the contents of the PC jam-transfer into the MA, the IR clears, and the major state generator is set to fetch. This concludes the TAD instruction; the program is ready to fetch the next instruction from the location specified by the contents of the MA.

Increment and Skip if Zero (ISZ) – The ISZ instruction reads the contents of the addressed memory cell into the MB and then increments the contents of the MB by 1. If the incremented contents of the MB are not 0, the program proceeds to the next instruction. If the incremented contents of the MB are equal to 0, the contents of the PC increment by 1, and the program skips the next instruction.

Operations during the fetch cycle of an ISZ instruction are identical to those during the fetch cycle of an AND instruction. During the execute cycle of an ISZ instruction, the operand (2<sub>8</sub>) is read into the MB. The E (execute) level from the major state generator combines in the MB control with the ISZ level from the IR decoder. The presence of both levels conditions a gate which triggers at time T1 to produce a pulse that causes the contents of the MB to increment by 1. In 2's complement arithmetic, a register contains 0 only when all its flip-flops are in the 0 state. Therefore, if the incremented contents of the MB are not equal to 0, bit MB0 either remains steadily in the 0 state or changes to the 1 state. In either case, there is no effect on the PC. However, if incrementing the contents of the MB changes the contents to 0, bit

MBO changes from the 1 state to the 0 state. This transition of MBO triggers a gate already conditioned by the E level from the major state generator and the ISZ level from the IR decoder. The gate then produces a pulse which causes the contents of the PC to increment by 1.

During time state T2 of the execute cycle, the incremented contents of the MB write back into memory and the MB clears. The contents of the PC jam-transfer into the MA, the IR clears, and the major state generator is set to fetch.

Deposit and Clear Accumulator (DCA) - The DCA instruction (operation code 3<sub>8</sub>) deposits contents of the AC into the addressed memory cell and the AC clears. The original contents of the addressed cell are lost.

Operations during the fetch cycle of a DCA instruction are identical to those during the fetch cycle of an AND instruction. However, at the end of the DCA fetch cycle, when the major state generator is set to execute, the E level combines with the DCA level from the IR decoder to generate a MEM STROBE ENABLE level. This level inhibits generation of the memory strobe pulse; so although full select read current passes through the core windings of the addressed cell and switches the cores to the 0 state, the contents of the cell do not read into the MB and are therefore lost.

During time state T1 of the execute cycle, timing pulse T1 triggers a gate conditioned by the DCA level and causes the contents of the AC to transfer to the MB. Simultaneously, a second gate triggers to produce a pulse that clears the AC. During time state T2, the contents of the MB write into core memory and the MB clears. Then the contents of the PC jam-transfer into the MA, the IR clears, and the major state generator is set to fetch.

Jump to Subroutine (JMS) – The JMS instruction (operation code 4<sub>8</sub>) provides an exit from the main program into a subroutine. The contents of the PC (current program count) increment by 1 and write into the core memory address specified by the JMS instruction. That address transfers to the PC and increments by 1; this incremented address fetches the first subroutine instruction during the next machine cycle. When the subroutine ends, the main program reenters by a jump indirect to the address specified by the original JMS instruction. The contents of that address are now the incremented main program count, and transferring this count into the PC causes the main program sequence to continue.

The flow chart completely specifies the events which take place during execution of a JMS instruction. However, these events are easier to understand if a concrete example illustrates the flow chart. The following description of the instruction sequence assumes that the main program is in page D of core memory (current page), and that the 21st instruction is JMS page 0 cell 100. The sequence of events appears in Table 2-1 and occurs as follows:

1. During time state T2 of instruction 20 of the main program, the PC contains the address of the next instruction, cell 21 in page D (current page). This address jamtransfers into the MA.

- 2. When the memory strobe occurs, the contents of cell D21 read into the MB. After the memory strobe, the MB contains JMS/0/100. The JMS operation code is in bits MB0 through MB2; page 0 is specified by MB3 (0), denoting a direct address, and MB4 (0), denoting page 0. Bits MB5 through MB11 specify location 100 (of page 0).

- 3. During time state T1 of the JMS fetch cycle, the contents of the MB (JMS/0/100) are written back into memory in location D/21.

- 4. During time state T2 of the fetch cycle, the contents of bits MB5 through MB11 jam-transfer into the MA. The MA now contains D/100.

- 5. Because bit MB4 is 0, bits MA0 through MA4 are cleared. The MA now contains 0/100, the address specified by the JMS instruction.

- 6. The contents of the PC (D/21) jam-transfer into the MB, and the contents of bits MB5 through MB11 (100) jam-transfer into the PC. Although simultaneous command pulses effect this exchange, both transfers take place without any mutual interference due to the storage time of the DCD gates. The MB now contains D/21, the main program count; the PC contains D/100.

- 7. Because MB4 contained 0 at the time of sampling, bits 0 through 4 of the PC clear, now containing 0/100. The major state generator is set to execute.

- 8. Generation of the memory strobe signal is suppressed to avoid disturbing the contents of the MB.

- 9. During time state T1 of the execute cycle, the contents of the PC and the contents of the MB each increment by 1. The PC now contains 0/100, the address of the first subroutine instruction; the MB contains D/22, the address of the main program instruction after completion of the subroutine.

- 10. The contents of the MB (D/22) write into memory at location 0/100, as specified by the JMS instruction.

- 11. The entire contents of the PC (0/100) jam-transfer into the MA, the IR clears, and the major state generator is set to fetch.

- 12. When the memory strobe occurs, the first instruction of the subroutine reads into the MB from location 101 of page 0. The program then proceeds to execute the subroutine.

Jump (JMP) - The JMP instruction occurs in a single fetch cycle if the address specified by the instruction is in the current page or in page 0. If the address is in any other page, a defer cycle is also required. The address specified in the instruction word is set into the PC and then transfers to the MA, so that the next instruction is taken from this address.

During the first part of the fetch cycle, the contents of the addressed memory cell (JMP instruction) read into the MB. Then, since no program interrupt has been acknowledged, the operation code (5<sub>8</sub>) in bits MBO through MB2 is set into the IR. Note that during time state T1 the instruction rewrites into memory, but no other action occurs.

Operations during time state T2 depend upon whether the JMP specifies direct or indirect addressing. If indirect (MB3 is 0), the address specified in page 0 or the current page is set into the MA, the MB clears, and a defer state is established. If a direct address is specified, the contents of bits MB5 through MB11 are set into the PC. If the address is located in page 0 (MB4 is a 0), bits PC0 through PC4 are cleared. If the address is in the current page (MB4 is a 1), the contents of these bits remain unchanged. If there is no break request, the contents of bits MB5 through MB11 are also set into the corresponding bits of the MA. Bits MA0 through MA4 clear for a page 0 address, and remain unchanged for a current page address. The MB then clears. Note that the notation 0 — MB appears in the first rectangle of time state T2 on the flow diagram. This should not be interpreted to mean that the MB clears before transfer of its contents to the PC and MA. In fact, the command pulses which clear the MB and open the appropriate PC and MA input gates generate simultaneously, which is technically feasible due to storage and delay times of the gates. Finally, the IR clears, and the major state generator is set to fetch.

#### Augmented Instructions

There are two classes of augmented instructions: the input/output transfer (IOT), which has the operation code  $6_8$ ; and the operate instruction (OPR), which has the operation code  $7_8$ . Augmented instructions are one-cycle (fetch) instructions which initiate various operations as a function of bit microprogramming.

TABLE 2-1 EXAMPLE OF REGISTER CONTENTS DURING A JMS INSTRUCTION

| Command                               | PC —J ₩ MA          | Memory to MB | MB5-11 — → MA | MB4(0): clear MA0-4 | PC → MB | MB5-11 — → PC | MB4(0): clear PC0-4 | MB to Memory | +1 ─ <b>→</b> PC | +1 — WB | Memory to MB | PC —J ► MA |                               |

|---------------------------------------|---------------------|--------------|---------------|---------------------|---------|---------------|---------------------|--------------|------------------|---------|--------------|------------|-------------------------------|

| MA Contents<br>0-4 5-11               | 21                  | 21           | 100           | 100                 |         |               |                     |              |                  |         |              | 101        |                               |

|                                       | ۵                   | ۵            | ۵             | 0                   |         |               |                     |              |                  |         |              | 0          |                               |

| MB Contents<br>0-4 5-11               |                     | 100          |               |                     | 21      |               |                     |              |                  | 22      | 22           |            |                               |

|                                       |                     | 0/SWL        |               |                     | Ω       |               |                     |              |                  | Δ       | ۵            |            |                               |

| Memory<br>Address Contents            | 001/0/SWf           | JMS/0/100    |               |                     |         |               |                     |              |                  |         | D/22         |            | 1st subroutine<br>instruction |

|                                       | D/21                | D/21         |               |                     |         |               |                     |              |                  |         | 0/100        |            | 0/101                         |

| PC Contents<br>ge Location<br>-4 5-11 | 21                  |              |               |                     | 21      | 100           | 001                 |              | 101              |         |              |            |                               |

| PC C<br>Page<br>0-4                   | ۵                   |              |               |                     | ۵       | Δ             | 0                   |              | 0                |         |              |            |                               |

| Time                                  | 12                  | Ε            | 12            |                     |         |               |                     |              | i⊥               |         |              | 12         |                               |

| Cycle                                 | Fetch or<br>Execute | Fetch        |               |                     |         |               |                     |              | Execute          |         |              |            |                               |

Assumptions for this example: 1. Memory pages are designated 0, A, B, C, D, E...etc.

<sup>2.</sup> Each page contains locations designated 0 through 128.

<sup>3.</sup> The main program is operating in page D.

<sup>4.</sup> The subroutine is in page 0, starting at location 101.

<sup>5.</sup> All operations within one time state occur simultaneously, not sequentially.

Input/Output Transfer (IOT) - The bit assignment of the IOT instruction is shown in Figure 1-3(b). Bits 0 through 2 contain the operation code (6<sub>8</sub>) and bits 3 through 8 form a code that enables the device selector in a given I/O device.

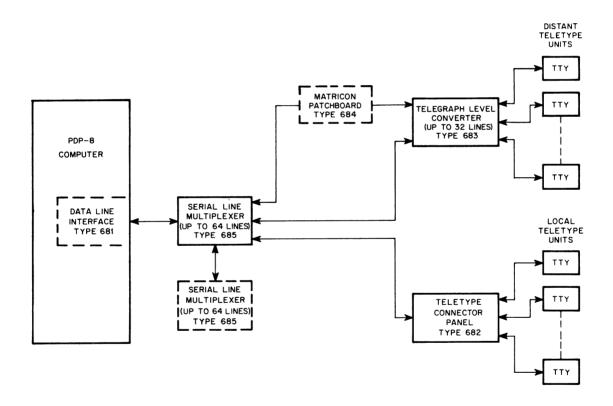

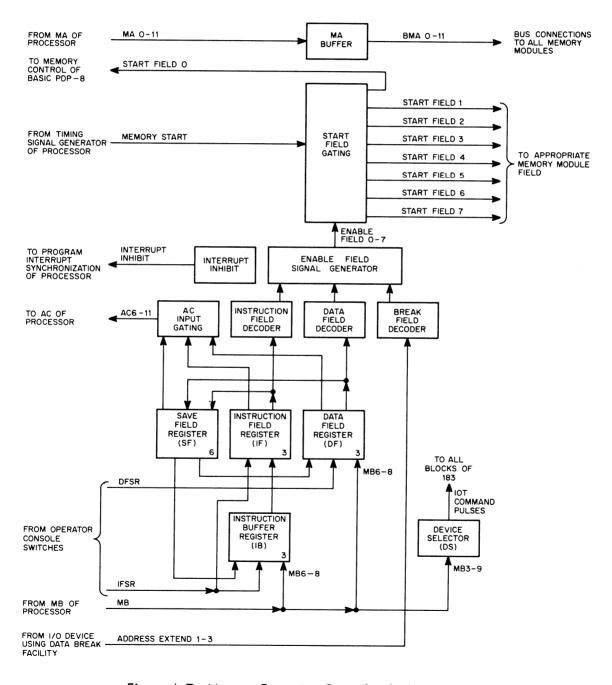

Three groups of IOT instructions are executed completely in a normal 1.5-µsec fetch cycle. These are the commands having a select code of 00 that apply to the program interrupt and Analog-to-Digital Converter Type 189, commands with a select code of 2X that apply to the optional Memory Extension Control Type 183, and commands having a select code of 40 that apply to the Data Line Interface Type 681. When instructions in either of these groups are executed, the instruction word reads into the MB during the memory strobe period, and the operation code is set into the IR. Detection of select codes 00 or 2X in bits MB3 through MB8 inhibits the generation of IOP pulses. Special decoding of bits 9, 10, and 11 in the program interrupt synchronization element and in the Type 183 option generates pulses that substitute for IOT commands. For example, when the select code is 00 if bit MB11 contains a 1 (ION), the INT ENABLE flip-flop sets; so the processor responds to interrupt requests from an I/O device, or if bit MB10 contains a 1 (IOF), the INT ENABLE and INT delay flip-flops clear, preventing any interruption of the program. The MB clears in time state T2. Then, if there is no break request, the contents of the PC (incremented during time state T1) are set into the MA, the IR clears, and the major state generator is set to fetch.

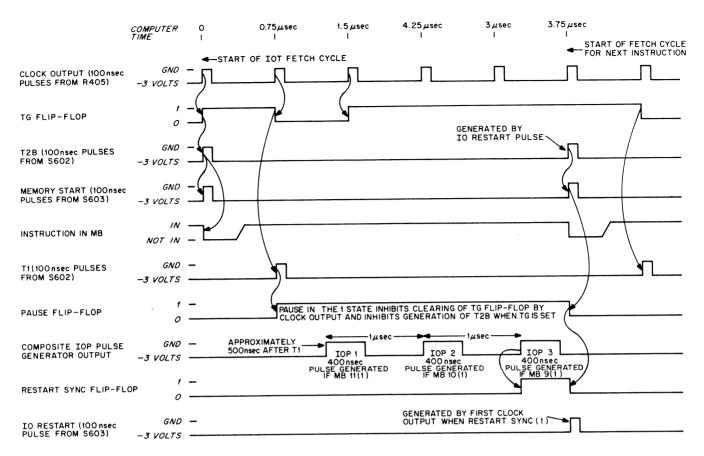

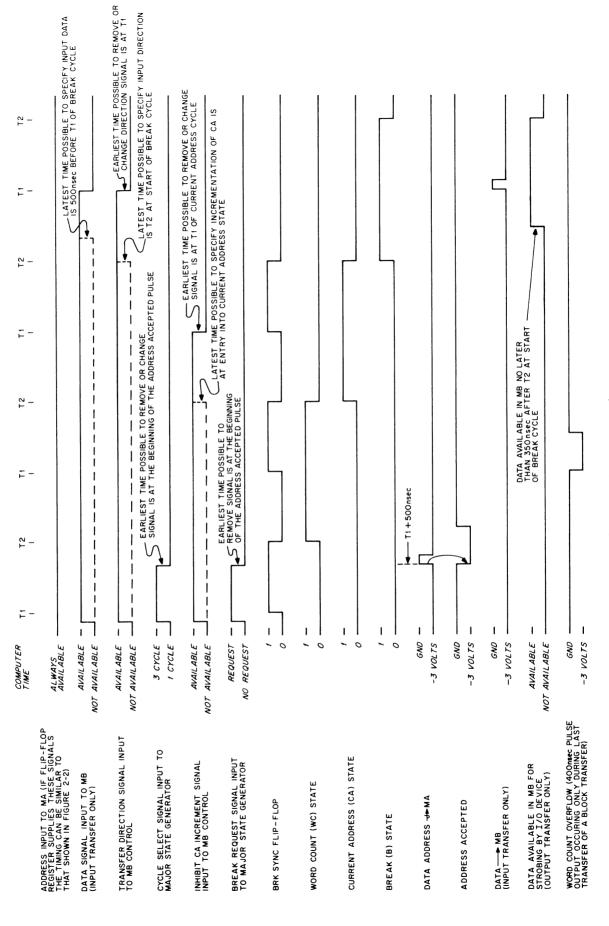

Any other IOT instructions use the pause facilities to extend the fetch cycle to 3.75 µsec (2.5 machine cycles) so that IOP pulses can generate, and to decode the select code by the device selector in an I/O device. When a normal IOT instruction is detected, a 1 PAUSE signal level generates which sets the PAUSE flip-flop and stops the timing generator of the main computer cycle. The 1 PAUSE command pulse also starts the timing chain of the IOP pulse generator which, after 0.5 µsec, permits generation of an IOP1 pulse if bit MB11 of the IOT instruction contains a 1. An IOP2 pulse generates 1 µsec later if bit MB10 contains a 1, and an IOP4 pulse generates 1 µsec after IOP2 if bit MB9 contains a 1. At a time 2.5 µsec after the generation of the 1 PAUSE command pulse, the IOP pulse generator sets the RESTART SYNC flip-flop to 1. Changing RESTART SYNC flip-flop from the 0 to the 1 state sets the RUN flip-flop. The next clock pulse forces generation of a T2B timing pulse that sets the major state generator to fetch, and causes a MEM START pulse to occur. The MEM START pulse clears the PAUSE flip-flop, which in turn clears the RESTART SYNC flip-flop. The RUN(1) and PAUSE(0) levels enable the timing circuits and the processor resumes its normal 1.5 µsec timing cycle. These operations appear in Figure 2-1.

The IOP pulses are gated in the device selector of the addressed I/O device to produce IOT pulses that control the operation of the device, effect a transfer of information between the device and the processor, or initiate action in the processor such as clearing the AC or incrementing the PC. For details of the IOT instructions available, refer to the PDP-8 Users Handbook, F-85.

Figure 2-1 IOT Timing Diagram

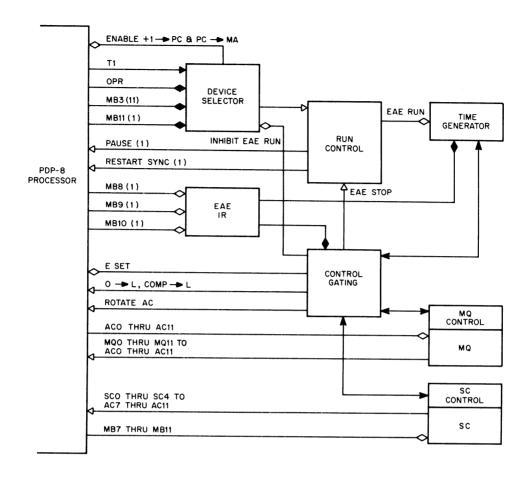

Operate (OPR) - The OPR instruction consists of two groups of microinstructions. The format of both groups appears in Figure 1-3(c) and 1-3 (d). In each case, bits 0 through 2 contain the operation code  $7_8$ . Group 1, designated by a 0 in bit 3, performs clearing, complementing, rotating, and incrementing operations. Group 2, designated by a 1 in bit 3 and a 0 in bit 11, checks the contents of the accumulator and link, and uses the result of the check to determine whether the next instruction is to be performed or skipped.

The operations specified by the group 1 OPR microinstructions may occur singly or in logical combination. It would not be logical, for example, to specify RAR and RAL simultaneously, since they are conflicting operations. The instruction word is read into the MB by the memory strobe, and the contents of the PC increment during time state T1. Thereafter, the following operations take place as a function of the contents of bits 4 through 11:

- 1. Clear accumulator (CLA). If bit MB4 is 1 and MB6 is 0, the accumulator clears during time state T1.

- 2. Clear link (CLL). If bit MB5 is 1 and bit MB7 is 0, the link flip-flop clears to 0 during time state T1.

- 3. Complement accumulator (CMA). If bit MB4 is 0 and bit MB6 is 1, the contents of the AC are set to the 1's complement of its original content, during time state T1.

- 4. Complement link (CML). If bit MB5 is 0 and bit MB7 is 1, the link flip-flop complements during time state T1.

- 5. Set accumulator (STA). If bits MB4 and MB6 are both 1, the AC contains all 1's during time state T1. This operation is logically equivalent to combining the CLA and CMA commands.

- 6. Set link (STL). If bits MB5 and MB7 are both 1, the link flip-flop is 1. This operation is logically equivalent to combining the CLL and CML commands.

Rotation and incrementation of the AC take place during time state T2 of group 1 OPR instructions. The instructions are:

- 1. Rotate accumulator right (RAR). If bit MB8 is 1 and bit MB10 is 0, the combined contents of the accumulator and link rotate one place right.

- 2. Rotate two right (RTR). If bits MB8 and MB10 are both 1, the combined contents of the accumulator and link rotate two places right.

- 3. Rotate accumulator left (RAL). If bit MB9 is 1 and bit MB10 is 0, the combined contents of the accumulator and link rotate one place left.

- 4. Rotate two left (RTL). If bits MB9 and MB10 are both 1, the combined contents of the accumulator and link rotate two places left.

- 5. Increment AC (IAC). If bit MB11 is a 1, the contents of the AC increment by 1. This instruction combines with the CMA microinstruction to convert a binary number in the AC to its equivalent 2's complement number.

When all the microinstructions specified by a group 1 OPR instruction are performed, the MB clears and, if there is no break request, the IR clears and the major state generator remains in the fetch state.

The operations specified by the microinstructions of group 2 OPR may be performed singly or in any logical combination. The microinstructions include clear accumulator, halt, and those which cause a skip as a function of the status of the AC and/or link. If two or more skips combine in a single group 2 OPR instruction, when bit 8 is a 0, the inclusive OR of the various skip conditions determines the skip. When bit 8 is a 1, the AND of all the inverse skip conditions determines the skip.

During the strobe portion of the fetch cycle, the instruction word reads into the MB and the operation code goes into the IR. Then, during time state T1, the contents of the PC increment by 1 if no skip is specified or if the specified conditions for a skip are not met. If a skip is specified and the required conditions are met, the contents of the PC increment by 2, causing the program to skip over one instruction. Three of the microinstructions do not cause a skip and are not affected by the contents of bit 8. These are:

- 1. Clear accumulator (CLA). When bit 4 contains a 1, the AC clears to all 0's.

- 2. OR with SWITCH REGISTER (OSR). When bit 9 contains a 1, binary 1's in the SR transfer into the corresponding bits of the AC. This transfer does not affect AC bits which already contain a 1; thus, the final contents of the AC are the inclusive OR of the 1's in both registers. Note that if the OSR and CLA microinstructions combine, the CLA operation takes place in time state T1, and the OSR operation in time state T2. Thus, the contents of the SR transfer to the AC and the original contents of the AC are lost.

- 3. Halt (HLT). When bit 10 contains a 1, the RUN flip-flop is set to 0 during time state T1, and the program halts at the end of time state T2. The HLT microinstruction can combine with any others in the same operate group, regardless of the event time at which they occur.

There are six conditional and one unconditional skip microinstructions. A 1 in bit 8 and 0's in bits 5, 6, and 7 specify an unconditional skip (SKP). Conditional skips fall into three pairs, in which a 0 in bit 8 specifies one microinstruction of a pair and a 1 in bit 8 the other. The pairs are:

- 1. Skip on non-zero link (SNL) and skip on zero link (SZL). When bit 7 is 1 and bit 8 is 0, the contents of the link are sampled, and, if the content is 1, the next instruction is skipped (SNL). When bits 7 and 8 are both 1, the skip occurs if the content of the link is 0 (SZL).

- 2. Skip on zero AC (SZA) and skip on non-zero AC (SNA). When bit 6 contains a 1, the contents of the AC are sampled. If bit 8 is 0, the next instruction is skipped if the contents of the AC are 0 (SZA); if bit 8 is 1, the next instruction is skipped if any bit of the AC contains a 1 (SNA).

- 3. Skip on minus AC (SMA) and skip on positive AC (SPA). When bit 5 contains a 1, the contents of bit AC0 are sampled. If bit 8 contains a 0, the next instruction is skipped

when bit ACO contains a 1, indicating that the AC contains a negative 2's complement number. If bit 8 is 1, the next instruction is skipped when bit ACO contains a 0, indicating that the AC contains a positive 2's complement number.

### Indirect Addressing

In a memory reference instruction, nine bits are available for specifying the address of the operand. These are sufficient for specifying an address in the same page of memory as the instruction, or an address in page 0. Twelve bits are required to address an operand in any other page. In such a case, the address in bits 5 through 11 of the instruction word is not the absolute address of the operand, but the address of a memory location (in the current page or in page 0) in which the absolute address of the operand is stored. Further, bit 3 of the instruction word contains a 1 signifying an indirect address.

An indirectly addressed memory reference instruction requires three cycles: fetch, in which the instruction is retrieved from memory; defer, in which the absolute address of the operand is retrieved from memory; and execute, in which the operand is retrieved from memory and the specified operation is executed. The only exception to this rule is a JMP indirect which is executed in a fetch and a defer cycle.

During the fetch cycle, the instruction word reads into the MB and the operation code is set into the IR. If the instruction is AND, TAD, ISZ, or DCA, the contents of the PC increment by 1. Incrementation does not occur, however, if the instruction is an indirectly addressed JMS or JMP. During time state T2 of the fetch cycle, the current page address specified by the instruction goes into the MA. Then, since bit MB3 contains a 1, the MB clears and the major state generator is set to defer.

During the strobe portion of the defer cycle, the absolute address of the operand reads into the MB.

During time state T1, if bits MA0 through MA7 are 0 and bit MB8 is 1 (indicating that the address specified by the instruction was one of the autoindexing locations 10 through 17 in page 0), the contents of the MB increment by 1 and the incremented contents rewrite into memory at the same address.

During time state T2 of the defer cycle, if the instruction is neither JMP nor JMS, the contents of the MB jam-transfer into the MA, setting the absolute address of the operand into the MA. The MB then clears, and the major state generator is set to execute.

If the instruction is JMS, the contents of the PC jam-transfer into the MB during time state T2, and the entire contents of the MB then jam-transfer back into the PC. If the instruction is JMP, during time state T2 the contents of the MB jam-transfer into the PC and the MB clears. The contents of the MB also

transfer into the MA, setting up the address of the next instruction. The IR clears, and the major state generator indicates fetch. The subsequent fetch cycle retrieves the next instruction from the location indirectly specified by the JMP instruction.

## Program Interrupt

I/O devices which require several commands to accomplish an information transfer or that are too slow to have the computer wait in a skip loop for the device to complete an operation, employ the program interrupt facility. A program interrupt is similar to a JMS to address 0000. When the program enables the program interrupt, an I/O device or other peripheral equipment initiates an interrupt request, or the interrupt may initiate from a programmed IOT instruction. An interrupt can occur only on completion of the current instruction, and takes effect at the beginning of the following fetch cycle.

During the strobe portion of the fetch cycle, the operation code for JMS goes into the IR, regardless of the instruction word read into the MB. The contents of the MB then write back into the original location during time state T1. During time state T2, the MA clears and the contents of the PC jam-transfer into the MB. The major state generator then indicates execute.

During the execute cycle of the JMS, generation of the memory strobe pulse is inhibited. During time state T1, the contents of the MB (which are the current program count) write into memory at location 0. The contents of the PC then increment by 1. During time state T2, the MB clears, the contents of the PC (0001<sub>8</sub>) jam-transfer into the MA, the IR clears, and the major state generator is set to fetch. Thus, the next instruction will come from memory location 1. The instruction stored at this location is usually a JMP which transfers program control to the first instruction of a subroutine for identifying and servicing the interrupting device. A JMP indirect to address 0000<sub>8</sub> executes exit from the subroutine and reentry into the main program at the point of the interrupt.

### AUTOMATIC OPERATION

#### Data Break

Data breaks occur as a single-cycle break state at an address specified by the requesting device, or as a three-cycle data break consisting of a word count, current address, and break state in which words in the computer core memory control the number of words transferred and the address of each transfer. The data break allows a high-speed I/O device to transfer data with core memory without disturbing the program or active registers. The device requesting a data break supplies a BREAK REQUEST, CYCLE SELECT, TRANSFER DIRECTION, a 12-bit data (core memory) address, and a 12-bit data word (when the transfer

direction is into the computer). When a break request occurs, the address designated by the device jamtransfers into the MA during time T2 of the last cycle of the current instruction, and the major state generator is set to the WC state if the CYCLE SELECT signal is at ground, or is set to the B state if this signal is at -3v. The program delays for the duration of the data break, commencing in the following cycle. Note, however, that a break request is granted only after completion of the current instruction. A break occurs only under the following conditions:

- 1. At the end of the fetch cycle of an OPR or IOT instruction, or of a directly addressed JMP instruction.

- 2. At the end of the defer cycle of an indirectly addressed JMP instruction.

- 3. At the end of the execute cycle of a JMS, DCA, ISZ, TAD, or AND instruction.

### Single-Cycle Data Break

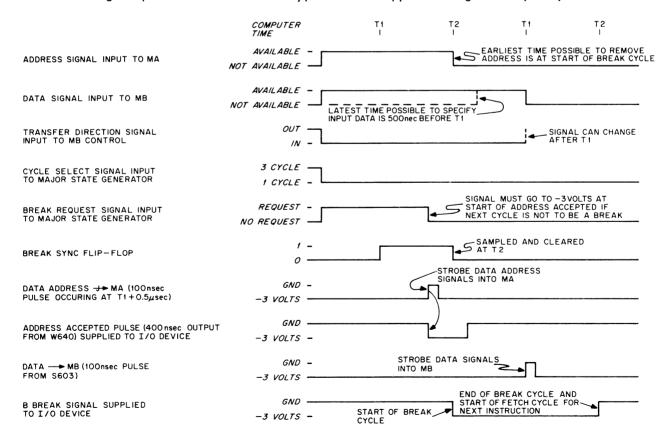

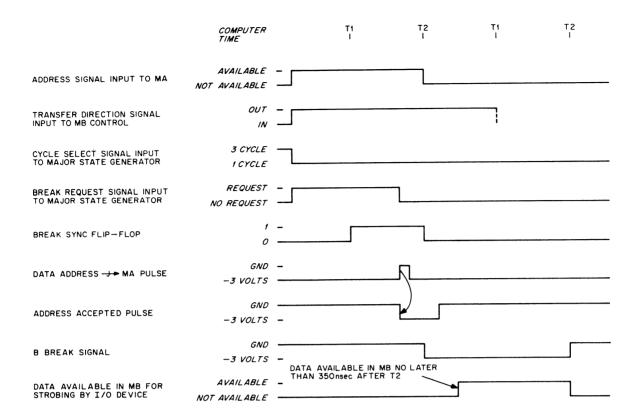

One-cycle breaks transfer a data word into the computer core memory from the device, transfer a data word into a device from the core memory, or increment the contents of a device-specified memory location. The timing of operations in these three types of break appears in Figures 2-2, 2-3, and 2-4.

Figure 2-2 Single-Cycle Data Break Input Transfer Timina

Figure 2-3 Single-Cycle Data Break Output Transfer Timing

In each of these types of data break one computer cycle is stolen from the program for each transfer; break cycles occur singly (interleaved with the program steps) or continuously (as in a block transfer), depending upon the timing of the BREAK REQUEST signal.

During the strobe portion of the break cycle, the contents of the addressed cell read into the MB if the transfer is out of the computer (into the I/O device). However, if the transfer is into the computer, generation of the memory strobe pulse is inhibited so that the MB (cleared during the previous cycle) remains cleared. During time state T1 of the break cycle, information transfers from the output data register of the I/O device into the MB and writes into memory. In the case of an outward transfer, the write operation restores the original contents of the addressed cell to memory.

During time state T2 of the break cycle, the MB clears. If there is a further break request, another break cycle may initiate. If there is no break request, the contents of the PC jam-transfer into the MA, the IR clears, and the major state generator is set to fetch. The program is then ready to execute the next instruction.

Figure 2-4 Single-Cycle Data Break Memory Increment Timing

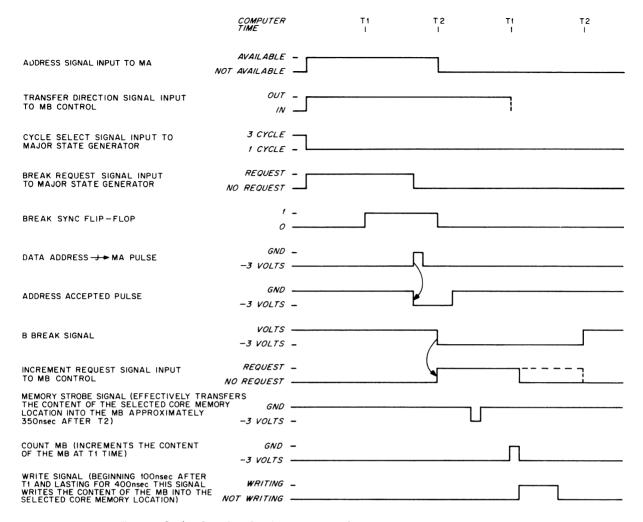

#### Three-Cycle Data Break

The three-cycle data break facility provides an economical method of controlling the transfer of data between the computer core memory and fast peripheral devices. Transfer rates in excess of 220 kc are possible using this feature of the PDP-8.

The three-cycle data break differs from the one-cycle break in that a ground-level CYCLE SELECT signal is supplied and the WC (word count) state is entered to increment the fixed core memory location containing the word count. The device requesting the break supplies this address as in the one-cycle break, except that this is a fixed address supplied by wired ground and -3v signals rather than from a register. The only restriction on this address is that it must be an even number (bit 11 = 0). Following the WC state a CA (current address) state occurs in which the location following the WC address (bit 11 = 1 after  $+1 \Rightarrow PC$ ) is read, incremented by one, restored to memory and used as the transfer address (by  $MB \Rightarrow MA$ ). Then the normal B (break) state is entered to effect the transfer. Figure 2-5 indicates the timing of these operations.

Figure 2-5 Three-Cycle Data Break Timing

Word Count State - When this state is entered the core memory address specified by the external device reads into the MB during time state T1. The word in the MB increments by 1 to advance the word count and if the word becomes 0 when incremented, a WC OVERFLOW pulse generates and flows to the device. During time T2 the incremented word rewrites in memory, the MB clears, the contents of the MA increment by 1 to establish the next location as the address for the following cycle, and the major state generator is set to the current address state.

Current Address State - Operations during the second cycle of the three-cycle data break depend upon the condition of the INCREMENT CA INHIBIT (+1 — CA INHIBIT) signal supplied to the computer from the external device. During T1 the address following the word count reads into the MB. If the INCREMENT CA INHIBIT signal is at ground potential, no further operations occur during T1. If this signal is at -3v, the contents of the MB increment by 1 during T1 to advance the address of the transfer to the next sequential location. During T2, the contents of the MB rewrite into core memory, the address word in the MB jam-transfers into the MA to designate the address to be used in the succeeding cycle, the MB clears, and the major state generator is set to the break state.

Break State - The actual transfer of data between the external device and the core memory, through the MB, occurs during the break state, as during a single-cycle data break, except that the current contents of the MA, not the device itself, determine the address.

### CHAPTER 3

### **PROCESSOR**

Logic circuit elements of the processor perform the major arithmetic, logic, and control functions of the PDP-8. The processor performs all operations of the PDP-8 except those directly concerned with data storage and retrieval in core memory and information exchanges with I/O equipment. In performing these operations, the processor draws instructions from core memory and executes them by sequentially establishing one or more major control states. Each control state lasts the duration of one computer cycle, in which there are two time states.

Functional operation of the processor is similar to a 3-dimensional matrix. As in the matrix, X, Y, and Z coordinates must be specified to locate a given point, so within the processor an instruction, a major state, and a timing pulse determine the specific logic function performed. A change in any one of these determinants changes the resultant logical operation. In general, the current instruction and current state determine the major state, except that a data break request originating in peripheral equipment initiates the word count or break state. The word count or break state occurs only after the current instruction is completed. Execution of each of the six basic memory reference instructions requires two or three of the major states. Execution of an augmented instruction requires only one state, although an IOT instruction increases the normal timing cycle. The sequence of operations during execution of each of the eight basic instructions is described in detail in Chapter 2 of this manual.

NOTES: Throughout Chapters 3, 4, 5, and 6 all drawing references in headings and in text are to the block schematic engineering drawings of the computer, unless otherwise stated. Block schematic diagrams carry the identifying code BS-D-8-0-X, where X is the number of the specific drawing. For brevity, only the drawing number (X) is given as a reference to these drawings. Drawings carrying any other identification code are referenced by the complete identification number.

Several of the module types in the PDP-8 belong to an S series which is not described in the Digital FLIP CHIP Modules Catalog, C-105. Series S modules are logically identical to R series modules described in the catalog. Except for a faster transistor and a lower value of load resistor in the output stage, S series modules are identical to R series modules.

## POWER CLEAR GENERATOR (9, 16)

During the power turnon sequence, the power clear generator produces repeated PWR CLR (power clear) pulses at a repetition rate of 100 kc. Pressing the start key also produces a single PWR CLR pulse. These

pulses clear the PAUSE flip-flop (10), all the memory control flip-flops, all the Teletype control flip-flops, and the TTI and TTO registers of the Teletype control. The PWR CLR pulses buffered by a pulse amplifier arrive at the interface connectors as the negative B POWER CLEAR pulses for clearing registers and control flip-flops of peripheral equipment.

During the power turnon sequence, potentials on the +10v and -15v supply lines rise relatively slowly because of the large amount of filter capacitance employed (210,000 µf in the -15v supply). Until the potential on the -15v line reaches -14v, the memory read/write and inhibit power supplies are disabled, and the PWR STATUS signal from the Type 708 Power Supply is at ground level. However, the memory and processor logic circuits become operative when the potential on the -15v line reaches approximately -8v. The PWR STATUS ground level inverts to produce a negative PWR OK level at inverter output terminal PB30F (9). The PWR OK level has two functions:

- 1. It inverts again to produce a RUN STOP ground level at inverter output terminal PD31F. The RUN STOP level in turn inverts to produce a negative RUN STOP level at inverter output terminal PB33D. During the power turnon sequence, the RUN STOP level clears the RUN flip-flop at every computer clock pulse to ensure that transients within the machine do not prematurely start programmed operation.

- 2. It enables the Type R401 Variable Clock at location PD30. The 100-kc pulses at terminal PD30D gate with the RUN (0) level to produce the positive PWR CLR pulses.

When the rising potential on the -15v supply line reaches -14v, the memory current supplies become enabled and the PWR STATUS signal changes to -3v. This action disables the variable clock and removes the RUN STOP level. Generation of the PWR CLR pulses ceases and the processor is ready for manual or programmed operation. The START key also generates one PWR CLR pulse.

# SPECIAL PULSE GENERATOR (9)

The special pulse generator, shown in the upper portion of engineering drawing 9, provides the timing pulses required to initiate functions during manual operations. There are four sequential special pulses, designated SP0 through SP3.

Any key except the STOP key starts the special pulse generator. The key produces ground level which inverts in module PB31 and causes the Schmitt trigger in module PA36 to change state. The negative-going transition which appears at the output of module PA36 inverts to produce timing pulse SP0.

The SPO triggers a one-shot in the Type R302 Delay module in PA35. Throughout the 4-µsec period during which the one-shot is in its unstable state, a negative SP STOP level is present at terminal PA35M. This level, one input to a transistor NOR gate, produces a ground RUN STOP level, which in turn produces a negative RUN STOP level at terminal PB33D. During programmed operation of the processor the RUN STOP level clears the RUN flip-flop at the next clock pulse if the PAUSE flip-flop is set to 1 and the RESTART SYNC flip-flop clears, or at the next occurrence of time state T1 if the PAUSE flip-flop clears to 0. (For further details, refer to the description of the Run and Pause Control.) If the program is not running when the key is operated, the SP STOP level has no effect.

At the conclusion of the 4-µsec delay period, the one-shot reverts to its stable state, and the positive-going level transition at terminal PA35M triggers pulse amplifier RSTU in the Type S603 module at location PA33. The positive SP1 timing pulse which appears at terminal PA33T inverts to produce a negative SP1 timing pulse. Both the positive and the negative SP1 timing pulses clear registers and effect information transfers. (Refer to flow diagram FD-D-8P-0-7 for a listing of these operations, and to the description of register controls in this chapter for operational details.)

The transition which produces the SP1 pulses also triggers a second one-shot in the Type R302 module at location PA35. At the conclusion of the 1-µsec delay period of this one-shot, a positive-going level transition appears at terminal PA35V. This transition functions as timing pulse SP2, which performs further information transfers and, during certain key operations, initiates a memory cycle to deposit or retrieve information.

The SP2 pulse triggers one-shot EM in the Type R302 module at location PA34. At the conclusion of the 1-µsec delay period, a positive-going level transition occurs at terminal PA34M. This transition functions as timing pulse SP3 and, in all key operations except a load address operation, sets the RUN flip-flop to 1 to start the computer.

## TIMING SIGNAL GENERATOR (9)

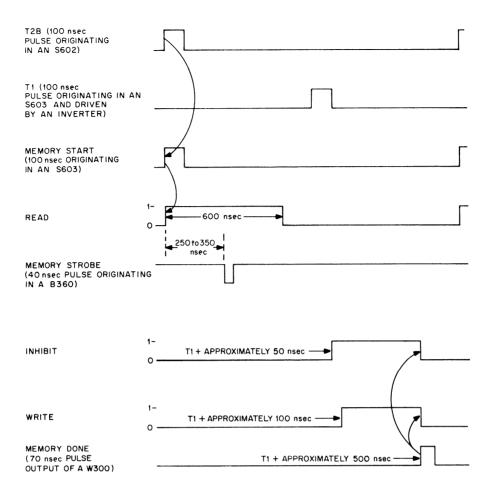

The timing signal generator provides all timing pulses required to perform logical operations during programmed operation of the computer. The timing signal generator appears on the right side of engineering drawing 9 and consists of a crystal clock, the TG (timing generator) flip-flop, pulse amplifiers, and gates. The computer cycle lasts 1.5 µsec, and divides into two time states designated T1 and T2. At the beginning of time state T1 in every cycle, an ungated pulse designated T1 generates. During execute cycles only, a gated pulse designated T1E generates concurrently with the T1 pulse. At the beginning of time state T2, the ungated timing pulse T2A always generates. The gated pulses T2B and T2E may also generate concurrently. Pulse T2E occurs only during an execute cycle. Pulse T2B occurs during every cycle of

programmed operation except cycles immediately preceding a halt or a pause. Before a halt or a pause, generation of pulse T2B is inhibited, retaining information set into registers during the current cycle for sampling or visual examination.

## Clock and TG Flip-Flop

The Type R405 Crystal Clock module at location PB35 produces standard positive 100-nsec pulses at a repetition rate of 1,333,333 pps. Each positive pulse complements the TG flip-flop, provided that the RUN flip-flop is set to 1 and the PAUSE flip-flop is set to 0.

A ground level permanently conditions the DCD set gate of the TG flip-flop. The reset DCD gate, how-ever, is conditioned by a ground level only when negative RUN (1) and PAUSE (0) levels are both present at the inputs of NAND gate RSU in module PB32. If either of these levels is at ground, the reset gate of the TG flip-flop is inhibited, and the flip-flop remains in the 1 state. The crystal clock runs continuously while power flows to the processor logic circuits.

### T1 Pulses

When the TG flip-flop is reset to 0, the positive-going transition at terminal PB34J triggers pulse amplifier circuit DEFH of the Type S603 module at location PB36. A positive T1 pulse appears at terminal PB36F and is distributed to the logic circuits of the processor. A negative T1 pulse, required in certain circuits, appears at inverter output terminal PB33L.

A ground E (execute) level from the major state generator conditions the DCD input gate of pulse amplifier circuit DEFH in module PB33. This ground level is present only during an execute cycle; during any other major state, a negative  $\overline{E}$  level inhibits the gate. During the execute cycle, the transition of the TG flip-flop from the 1 to the 0 state triggers the DCD gate, and the pulse amplifier produces a positive TIE pulse at terminal PA33F. A negative T1E pulse appears at inverter output terminal PB33N.

### T2 Pulses

When the TG flip-flop is set to 1, a positive-going level transition of the 1 output at terminal H of the flip-flop goes to three DCD gates. A ground permanently conditions gate KL in module PB36, and this gate triggers each time the TG (1) transition occurs. The associated pulse amplifier circuit produces the positive timing pulse T2A at terminal PB36M.

A ground Elevel from the major state generator conditions gate KL in module PA33. During an execute cycle, the TG (1) transition triggers this gate, and the associated pulse amplifier circuit produces positive timing pulse T2E at terminal PA33M.

A ground RUN (1) PAUSE (0) level from terminal PB32U conditions gate PR of module PC30. When the processor is executing a program and the IOP generator is not in operation, this gate is conditioned. In each cycle the associated pulse amplifier produces positive timing pulse T2B at terminal PC30U. A programmed halt instruction clears the RUN flip-flop during time state T1, inhibiting gate PC30PR and suppressing pulse T2B. An IOT instruction sets the PAUSE flip-flop to 1, suppressing timing pulse T2B and maintaining the TG flip-flop in the 1 state. The program therefore pauses before time state T2 ends. At the end of the pause, an IO RESTART pulse arrives at terminal PC30V to trigger the pulse amplifier and produce pulse T2B, after which the program resumes. Timing pulse T2B also generates when the operator presses the CONT key. In this case, the KEY CONT level conditions DCD gate ST, triggered by special timing pulse SP2. The resulting T2B pulse initiates a MEM START pulse.

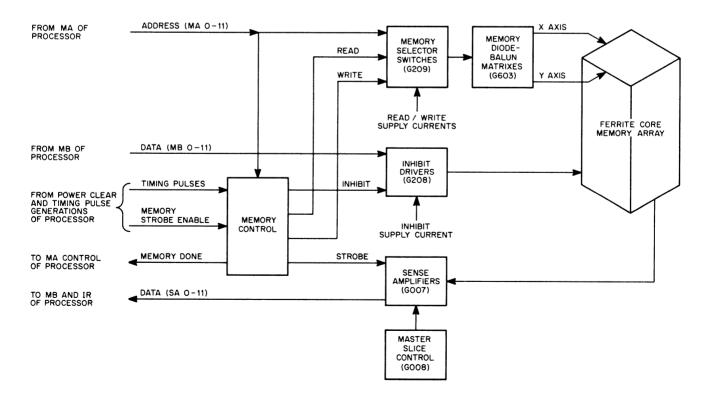

### MEM START Pulse

The MEM START pulse initiates memory operation. Timing pulse T2B arrives at the diode input of pulse amplifier VTU in the Type S603 module at location PB36. The MEM START positive pulse appears at terminal PB36T and goes to the memory control circuits in the core memory system, where it initiates a read operation. The MEM START pulse also generates during a manual start, examine, or deposit operation. When the operator presses the START, EXAM, or DEP key, the KEY ST+EX+DP ground level conditions the DCD input gate of the mem start generator. Special timing pulse SP2 triggers the gate, and the associated pulse amplifier produces the MEM START pulse at terminal PB36T.

## IOP GENERATOR (10, 16)

The IOP generator consists of a gated timing chain of delay modules initiated during an IOT instruction. When initiated, the timing chain produces a sequence of IOP pulses as determined by the contents of bits 9, 10, and 11 of the instruction. This circuit element consists of two Type R302 Delay modules at locations PA34 and PC34 and one Type S603 Pulse Amplifier module at location PC33. Each delay module contains two delay one-shots; the pulse amplifier module contains three pulse amplifiers.

Timing of the IOP pulses allows I/O equipment to perform sequential operations, initiated by each pulse within one instruction. The IOP pulses are spaced 1  $\mu$ sec apart; thus, IOT instructions take longer than the normal 1.5- $\mu$ sec cycle time. Therefore, when the IOP generator is initiated, the run and pause control delays the cycle for three clock pulses (2.25  $\mu$ sec). (1.5- $\mu$ sec normal cycle time +2.25- $\mu$ sec delay = 3.75- $\mu$ sec IOT cycle time.)

The 1 — PAUSE pulse initiates operation of the timing chain. A 6-input negative NAND diode gate produces this pulse at terminal PC35J. The gate triggers to produce the pulse when the T1 pulse occurs if all of the following conditions exist:

- 1. The IOT signal is at -3v, indicating that the current instruction is an IOT.

- 2. The F(1) signal is negative, indicating that the major state generator is in the fetch state.

- 3. The PROCESSOR IOT signal is negative, meaning the instruction does not have the select code of 00 used with the program interrupt control and the 189 Analog-to-Digital Converter.

- 4. The  $\overline{\text{MEM EXT}}$  signal is negative, meaning that the instruction is not a 1.5- $\mu$ sec IOT used with the 183 Memory Extension Control.

- 5. The  $\overline{\text{TT INST}}$  signal is negative, meaning that the instruction is not a 1.5- $\mu$ sec IOT used with the 681 Data Line Interface.

These conditions simply enable generation of the 1 — PAUSE pulse, and subsequent entry into a 3.75 µsec cycle for all IOT instructions except those which use the normal 1.5-µsec machine cycle or a special timing cycle determined by the device execution time.

One-shot NV is set to give a delay of 0.5 µsec; at the end of this time, the one-shot reverts to its stable state and the positive-going level transition appearing at terminal PA34V triggers one-shot EM in the same module. If bit MB11 contains a 1, the transition also triggers the DCD input gate of pulse amplifier circuit DFH in module PC33. The pulse amplifier produces an IOP 1 pulse at terminal PC33F; this pulse goes to pulse amplifier circuit DHJ of module MC31 in the memory assembly. A negative IOP 1 pulse appears at interface connector terminal MF34K (16, C7), where it is available to the device selectors of I/O equipment.

One-shot EM of module PC34 gives a delay of 1 µsec. At the end of this time, the one-shot reverts to its stable state and the positive-going level transition appearing at terminal PC34M triggers one-shot NV in module PC34. If bit MB10 contains a 1, the transition also triggers pulse amplifier KMN in module PC33, and a positive IOP 2 pulse appears at terminal PC33M. This pulse operates pulse amplifier KNP in module MC31, causing a negative IOP 2 pulse to be applied to interface connector MF34M.

One-shot NV of module PC34 gives a delay of 1 µsec. At the end of this time, the one-shot reverts to its stable state and sets the RESTART SYNC flip-flop to 1, if no RUN STOP signal has been generated in the meantime. At the same time, if bit MB11 contains a 1, the transition triggers pulse amplifier RSTU in module PC33 to produce an IOP 4 pulse at terminal PC33T. Pulse amplifier RUV in module MC31 produces a negative IOP 4 pulse which appears at interface connector terminal MF34P.

## RUN AND PAUSE CONTROL (9, 10, 16)

The run and pause control starts, stops, and temporarily interrupts programmed operation of the computer. The RUN flip-flop, when set to 1, enables operation of the timing signal generator, and when cleared to 0, disables the timing signal generator. The PAUSE flip-flop is set to 1 by most IOT instructions. When set to 1, the PAUSE flip-flop prevents advance of the program for a period of 2.5 µsec, during which one or more IOP pulses initiate to control the operation of peripheral equipment. At the conclusion of the pause, IO RESTART, T2B, and MEM START pulses restart operation of the computer and clear the PAUSE flip-flop.

## Run Control (9)

The RUN flip-flop provides a negative RUN (1) level which, in combination with a negative PAUSE (0) level, enables the TG flip-flop to be complemented at every clock pulse, thereby generating timing pulses. If either of these levels is at ground, the reset gate of the TG flip-flop is inhibited, and the computer stops in time state T2. The RUN flip-flop is set to 1 by the reset gate to perform functions initiated by operating the START, DEP, EXAM, or CONT keys, or is set when the RESTART SYNC flip-flop changes from the 0 to the 1 state.

Special timing pulse SP3 sets the RUN flip-flop when a ground KEY LOAD ADDRESS level conditions the set DCD gate. The KEY LOAD ADDRESS level is present except when the LOAD ADD key is pressed; inverter output terminal PB33J (9, B1) is then driven to – 3v and inhibits the RUN set gate. The RUN flip-flop is also set by the leading edge of the RESTART SYNC (1) level which arrives at the direct-set input of the flip-flop.

A positive pulse at output terminal S clears the RUN flip-flop when a HLT command is executed or when required by functions controlled by manual key operations. This flip-flop also clears through the reset gate for execution of an IOT instruction using the pause feature.

The RUN flip-flop clears during a pause condition if a RUN STOP level generates between the time the PAUSE flip-flop is set to 1 and the time the RESTART SYNC flip-flop is set. The RUN STOP, PAUSE (1), and RESTART SYNC (0) negative levels NAND combine to condition the DCD reset gate of the RUN flip-flop. The gate triggers at the next clock pulse and clears the RUN flip-flop. Under all other conditions of manual or stored program operation, the RUN flip-flop clears if a RUN STOP level conditions NAND gate KLN in module PA27. The gate, triggered by the next T1 timing pulse, clears the flip-flop. A 6-input NOR gate generates a RUN STOP level if any one of the following conditions exist:

- 1. During the power turnon sequence, a ground POWER STATUS level inverts in module PB30 to produce a negative PWR OK level. This level again inverts in module PD31, and inverter output terminal PD31F goes to ground, producing the ground RUN STOP level. The RUN STOP level generated during power turnon is not produced after the -15v supply line rises to -14v and the memory read/write and inhibit supplies rise to within 3v of their proper values.

- 2. During a manual examine or deposit operation, a KEY ST+EX+DP level produces the ground RUN STOP level.

- 3. When the SP STOP level is produced by the special pulse generator.

- 4. Whenever the SING STEP switch is activated (in the up position).

- 5. When the SING INST switch is activated (in the up position), the inverted SINGLE INST level NAND combines with the F SET level from the major state generator to produce a RUN STOP level at the end of each instruction.

- 6. During execution of a programmed HLT command. The halt microinstruction is included in a Group 2 OPR instruction by inserting a 1 in bit 10 of the instruction. The MB10 (1) level NAND combines with an OP2 pulse generated in control to produce the RUN STOP level.

## Pause Control (10)

The pause control, operated by the IOP generator, prevents advance of the timing signal generator, extending the cycle time of an IOT instruction by 2.25 µsec. The pause control consists of a PAUSE flipflop, a RESTART SYNC flip-flop, and associated gating circuits. The negative PAUSE (0) level (with the RUN (1) level) enables the timing generator when the flip-flop is set to 1, the ground level PAUSE (0) stops the program in time state T2. A negative PAUSE (1) level also drives the PAUSE indicator on the operator console.

The PAUSE flip-flop initially clears at power turnon by positive PWR CLR pulses arriving at diode OR gate input PD34R (10, A8), or during a key operation by special timing pulse SP1 applied to terminal PD34P. After a pause operation, a MEM START pulse at the direct clear input at terminal PC32K resets the flip-flop at T2 time.

A 1 — PAUSE pulse applied to the DCD gate pulse input at terminal PC32N sets the PAUSE flip-flop.

The 1 — PAUSE pulse generates in the IOP generator as described previously in this chapter.

The 1 — PAUSE command pulse also starts the IOP generator, and after 2.5 µsec the generator produces a pulse which sets the RESTART SYNC flip-flop if no RUN STOP level generates in the meantime. The RESTART SYNC (1) level conditions the DCD input gate of pulse amplifier circuit RTU of the Type S603 module in location PA29. The next clock pulse triggers the DCD gate and the pulse amplifier produces an IO RESTART pulse at terminal PA29T. This pulse causes the timing generator to produce timing pulse T2B. The reappearance of the PAUSE (0) level restores the timing generator to normal operation, and the program continues.

## **INSTRUCTION REGISTER (6)**

The instruction register is a 3-bit register consisting of a Type S203 Triple Flip-Flop module in location PB28. A Type S151 Binary-to-Octal Decoder module in location PB27 decodes the bit combination stored in this register. A ground applied to terminal PB27D permanently enables the decoder. Each output signal from the decoder flows to an inverter in module PA21 or PB26 to produce a ground level and a negative level for each of the following signals and their complements: AND, TAD, ISZ, DCA, JMS, JMP, IOT, OPR. These signals correspond to octal numbers 0 through 7, respectively, stored in binary form in the instruction register. The instruction signals and their complements gate the control logic throughout the processor.

Pulse amplifier circuit PVSUN in the Type S602 module in location PB20 clears the instruction register flip-flops collectively. During manual start, examine, or deposit operations, a KEY ST+EX+DP ground level applied to terminal PB20R conditions a DCD input gate which special timing pulse SP1 triggers clearing the instruction register in preparation for programmed operation or to be jam set with TAD or DCA instructions. During execution of a program the F SET level from the major state generator conditions a second DCD gate of this pulse amplifier which is triggered by timing pulse T2B. Thus, the instruction register clears upon completion of the current instruction. During a data break the leading edge of the B(1) level triggers the pulse amplifier to clear the IR. The B(1) level is the direct output of the major state generator, so the positive-going excursion of this level occurs at T2 time when the break state is entered.

The instruction register flip-flops are set individually, as follows:

1. During the fetch cycle of any instruction, flip-flops IRO through IR2 are set to the operation code contained in bits MBO through MB2. The F(1) level from the major state generator conditions a NAND gate associated with each IR flip-flop. Gates enabled by a 1 output signal from the corresponding MB flip-flop produce a ground level at their output terminals and force the associated IR flip-flop to the 1 state by pull-over action.

Note, however, a INT ACK (indicating that a program interrupt will not occur during the cycle) level as well as the F(1) and MB(1) levels must condition the gates associated with flip-flops IR1 and IR2.

- 2. At the beginning of a program interrupt, the INT ACK (interrupt acknowledged) level combines with the F(1) level to set flip-flop IRO only. The INT ACK level, at ground potential, disables the input gates of flip-flops IR1 and IR2. Thus, when an interrupt is acknowledged, the processor sets the operation code 4<sub>8</sub> into the IR, regardless of the code in bits MBO through MB2. This action forces execution of a JMS instruction.

- 3. Flip-flop IR1 is set during a manual deposit operation. The DCD input gate of the flip-flop, conditioned by a KEY DP level from the DEP key, is triggered by special timing pulse SP2. At the same time, flip-flop IR2 is set. This operation sets the DCA operation code into the IR.

- 4. Flip-flop IR2 is set during a manual deposit or examine operation. A KEY EX+DP level from the key circuits conditions the flip-flop DCD input gate which is triggered by special timing pulse SP2. During a deposit operation, flip-flop IR1 is also set, forcing a DCA instruction into the IR. During an examine operation, when only flip-flop IR2 is set, a TAD instruction is forced into the IR.

### MAJOR STATE GENERATOR (6, 10)

The major state generator consists of two Type S284 Quadraflop modules at locations PB25 and PC02, and associated input gating. Pulsing an appropriate input terminal can set a quadraflop to any one of four stable states. Connections from the active terminal (H) of one module to the disable terminal (V) of the other module ensure that only one state is set at a time. The standard PDP-8 uses only six of the eight available states. These states, and complementary output signals are designated fetch (F), defer (D), execute (E), word count (WC), current address (CA), and break (B). Adding the 681 Data Line Interface option to the system activates the two remaining states, designated status (S) and character (C). Refer to the description of the 681 in this chapter for an explanation of these states.