#### CHAPTER 5

#### INPUT/OUTPUT

Signals which pass between peripheral equipment and the PDP-8 are usually pulses supplied to a processor input bus, or static levels supplied as processor output signals which may be sampled or strobed by a selected I/O device. Exceptions to this rule are the address and data signals which arrive at the processor during data break operations as static levels, and the WC OVERFLOW, ADDRESS ACCEPTED, and IOP pulses, which are pulse outputs of the processor. The bussed nature of input/output signals of the processor requires that the peripheral equipment contain gating circuits to control the application of input pulses to the processor and timing control circuits to strobe processor output lines to transfer information into external device buffers. The design of circuits which perform these operations in input/output equipment depends upon the characteristics of the processor interface circuits as described in Chapter 6, the functional operation of the processor interface logic elements as explained in Chapter 3, and by the nature of the circuits in the peripheral equipment which receives or transmits signals. Gating circuits in peripheral equipment that supply input pulses to the processor are similar to those on the processor drawings for standard input/output devices.

Programmed information transfers (including initializing of equipment using the data break facility) between the processor and all other devices require that a preestablished select code in bits 3 through 8 of an IOT instruction enable each circuit (or group of circuits) transmitting or receiving information, and that transfers synchronize with the processor timing. A NAND gate and pulse amplifier circuits, serving as a device selector, perform these operations. Typical device selectors appear in engineering drawing 10 for the program interrupt synchronization element and on engineering drawing 11 for the Teletype control. An outline of a device selector suitable for peripheral equipment is at the end of this chapter.

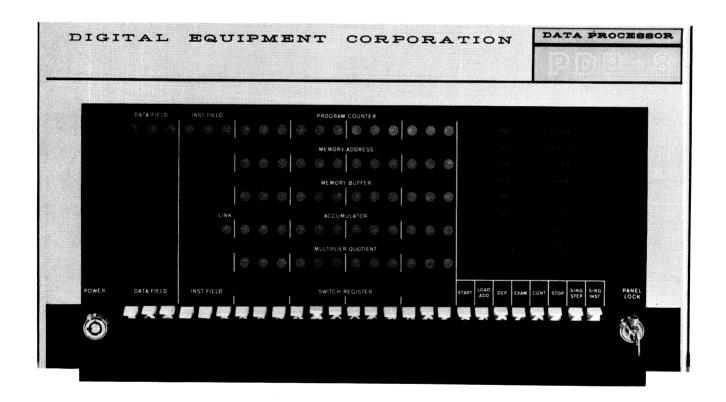

The standard peripheral equipment supplied with a PDP-8 consists of a Teletype Model 33 Automatic Send Receive Set and a Teletype Control, which are described in this chapter. Except for the Type 189 Analog-to-Digital Converter, described in this chapter because it is intricately involved in the operations of the PDP-8 and wired into the system (adding this option to the computer requires little more than the insertion of the modules into the module connector blocks), other optional peripheral equipment is described in separate documents. The Type KR01 Automatic Restart, Type 182 Extended Arithmetic Element, and Type 681 Data Line Interface options described in Chapter 3 of this manual and the Type 183 Memory Extension Control, Type 184 Memory Module, and Type 188 Memory Parity options described in Chapter 4 of this manual are not peripheral equipment since these options are integral parts of the system and functionally inseparable from the processor.

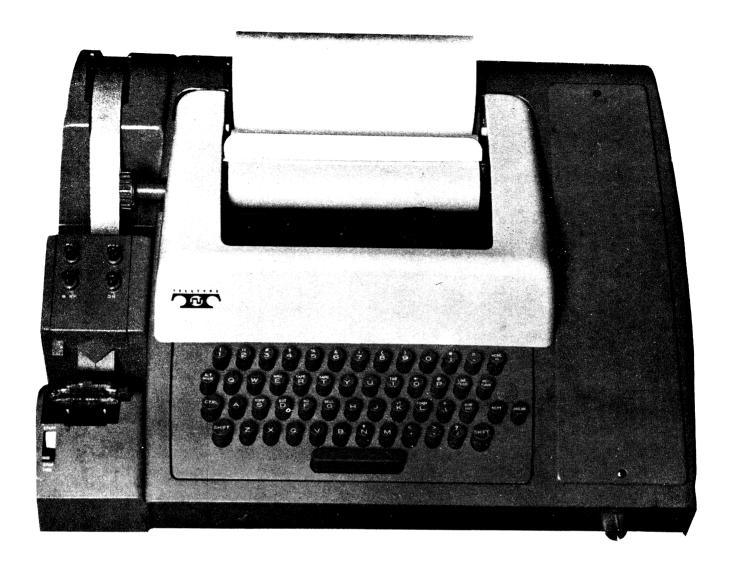

#### TELETYPE MODEL 33 AUTOMATIC SEND RECEIVE SET

The Teletype unit supplied as standard equipment with a PDP-8 serves as a keyboard input and page printer output, and as a perforated-tape reader input and a tape-punch output device. This unit is a standard Model 33 Automatic Send and Receive Set (ASR) as described in Teletype Corporation bulletins 273B and 1184B. For operation with the PDP-8, this unit is modified as follows:

- 1. The WRU (who are you) pawl is removed. This pawl is used only when several Teletypes connect in a communication system so that a unit receiving a message sends a "who are you" message to the transmitting unit which automatically produces the "here is" identification code and supplies it to the receiving station. In the computer system this pawl is removed to prevent insertion of the "here is" code into data supplied to the computer from the Teletype unit.

- 2. Cables are connected between the Teletype unit and the control as appears in engineering drawing 11. Signal cables connect to a terminal block within the stand. A relay is added and connections are made to the tape reader advance magnet. These connections enable tape motion while the control assembles a character, and disable the magnet when the keyboard flag is a 1, indicating that the assembled character is ready for transfer to the computer.

This modification takes only a few minutes and does not permanently limit any normal use of the 33 ASR.

## TELETYPE CONTROL (18)

The control assembles or disassembles serial information for the Teletype unit for parallel transfer to or from the accumulator of the processor. The control also provides the flags which cause a program interrupt or an instruction skip based upon the availability of the Teletype unit, thus controlling the rate of information transfer flow between the Teletype and the processor as a function of the program. Engineering drawing 11 shows the control and interface connections between the control and the Teletype unit.

Table 5-1 indicates interface connections between the control and the processor.

In all programmed operation, the Teletype unit is considered two separate devices: a Teletype input device (TTI) from the keyboard or the perforated-tape reader; and a Teletype output device (TTO) for computer output information to be printed and/or punched on tape. Therefore, two device selectors are used, consisting of 6-input NAND gates at locations ME17 and ME18 (11, A2 and B1). One of these is assigned the select code of 03 to initiate operations associated with the keyboard/reader, and the other is assigned the select code of 04 to perform operations associated with the teleprinter/punch. Corresponding IOT

TABLE 5-1 TELETYPE CONTROL INTERFACE WITH PROCESSOR

|                  |                          | Processor              |            | Symbol                                                                                    | Teletype            |

|------------------|--------------------------|------------------------|------------|-------------------------------------------------------------------------------------------|---------------------|

| Signal           | Logic<br>Element         | Engineering<br>Drawing | Terminal   | and<br>Direction*                                                                         | Control<br>Terminal |

| PWR CLR          | Power Clear<br>Generator | 9                      | PD33U      | <b>─</b>                                                                                  | MF36M               |

| BAC4 (1)         | AC                       | 16                     | MF34M      | $\longrightarrow$                                                                         | ME22S               |

| BAC5 (1)         | AC                       | 16                     | MF34P      | $\longrightarrow$                                                                         | ME23P               |

| BAC6 (1)         | AC                       | 16                     | MF34S      | $\longrightarrow$                                                                         | ME23R               |

| BAC7 (1)         | AC                       | 16                     | MF34T      | $\longrightarrow$                                                                         | ME23S               |

| BAC8 (1)         | AC                       | 16                     | ME34V      | $\longrightarrow$                                                                         | ME24P               |

| BAC9 (1)         | AC                       | 16                     | MF34D      | $\longrightarrow$                                                                         | ME24R               |

| BAC10 (1)        | AC                       | 16                     | MF34E      | $\longrightarrow$                                                                         | ME24S               |

| BAC11 (1)        | AC                       | 16                     |            | $\longrightarrow$                                                                         | ME25H               |

| INTERRUPT BUS IN | Interrupt Sync           | 10                     | PF1S       | <                                                                                         | MF36S               |

| COUNT PC         | PC Control               | 11                     | PF1R       | <                                                                                         | MF36R               |

| TTI——►AC         | AC                       | 2                      | PF1P       | <                                                                                         | MF36P               |

| KCC IOT 032      | AC Control               | 3                      | PF1U       | 4                                                                                         | MF36U               |

| IOP1             | IOP Generator            | 10                     | PF1J       | $\longrightarrow \hspace{0.2cm} \triangleright$                                           | MF36J               |

| IOP2             | IOP Generator            | 10                     | PF1K       | $\longrightarrow \hspace{0.5cm} \triangleright$                                           | MF36K               |

| IOP4             | IOP Generator            | 10                     | PF1L       | $\longrightarrow\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | MF36L               |

| MB3-4 (0)        | MB                       | 5                      | PD1R,T     | -                                                                                         | MD36R,T             |

| MB5-8 (0)        | MB                       | 5                      | PEID,F,J,L |                                                                                           | ME36D,F,J,L         |

| MB7-8 (1)        | MB                       | 5                      | PE1K,M     |                                                                                           | ME36K,M             |

| TTIO (0)         | AC                       | 2                      | PB1A       | $\diamond$ —                                                                              | MB36A               |

| TTI1 (0)         | AC                       | 2                      | PB1B       | $\diamond$ —                                                                              | MB36B               |

| TTI2 (0)         | AC                       | 2                      | PC1A       | <b>~</b> —                                                                                | MC36A               |

| TTI3 (0)         | AC                       | 2                      | PC1B       | <b>~</b> —                                                                                | MC36B               |

| TT14 (0)         | AC                       | 2                      | PD1A       | <b>~</b> —                                                                                | MD36A               |

| TTI5 (0)         | AC                       | 2                      | PD1B       | <b></b>                                                                                   | MD36B               |

| TT16 (0)         | AC                       | 2                      | PE1A       | $\Diamond$ —                                                                              | ME36A               |

| TT17 (0)         | AC                       | 2                      | PE1B       | $\Diamond$ —                                                                              | MF36B               |

<sup>\*</sup>Arrows pointing right designate processor output; arrows pointing left designate processor inputs.

pulses from the two device selectors perform parallel input and output functions. Pulses from the IOP1 pulse trigger the skip control element; pulses from the IOP2 pulse clear the control flags and/or the accumulator; and pulses produced by the IOP4 pulse initiate data transfers to or from the control.

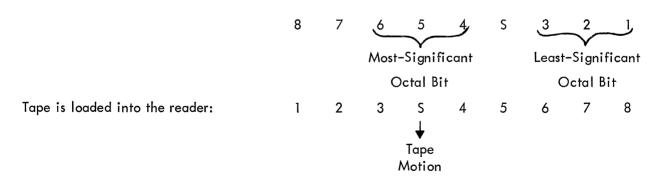

Signals used by the Teletype unit are standard 11-unit-code serial current pulses consisting of marks (bias current) and spaces (no current). Each 11-unit Teletype character consists of a 1-unit start space, eight 1-unit character bits, and a 2-unit stop mark. The 8-bit flip-flop TTI shift register at locations MF22 through MF24 receive the Teletype characters from the keyboard/reader. The character code of a Teletype character loads into the TTI so that spaces correspond with binary 1's and marks correspond to binary 0's. Upon program command the complement of the contents of the TTI transfers in parallel to the accumulator. Eight-bit computer characters from the accumulator load in parallel into the 8-bit flip-flop shift register TTO at locations ME22 through ME25 for transmission to the Teletype unit. The TTO clock generates the start space, then shifts the eight character bits into a flip-flop which controls the printer selector magnets of the Teletype unit, and then produces the stop mark. This transfer of information from the TTO into the Teletype unit occurs in serial manner at the normal Teletype rate.

A ground IN ACTIVE signal flows from the control circuit of the Teletype incoming line unit module when a Teletype character starts to enter the TTI. This signal clears the READER RUN flip-flop, which in turn energizes a relay in the Teletype unit to release the tape feed latch. When released, the latch mechanism stops tape motion only when a complete character has been sensed and before sensing of the next character begins. The KEYBOARD FLAG flip-flop sets and causes a program interrupt when an 8-bit computer character has been assembled in the TTI from a Teletype character. The program senses the condition of this flag with a KSF microinstruction (skip if keyboard flag is a 1, IOT 6031) and issues a KRB microinstruction (IOT 6036) which clears the AC, clears the keyboard flag, transfers the contents of the TTI into the AC, and sets the READER RUN flip-flop to enable advance of the tape feed mechanism.

A TELEPRINTER FLG flip-flop sets when the last bit of the Teletype code has been sent to the teleprinter/punch, indicating that the TTO is ready to receive a new character from the AC. This flag connects to both the program interrupt synchronization element and the skip control element. Upon detecting the set set condition of the flag by the TSF microinstruction (skip if teleprinter flag is a 1, IOT 6041), the program issues a TLS microinstruction (IOT 6046) which clears the flag and loads a new computer character into the TTO.

Operation of the Teletype incoming line unit TTI requires an input clock signal which is eight times the baud frequency of the Teletype unit. This signal controls the strobing of Teletype information into the TTI during the center of each baud (which is the most reliable time for sensing) and controls the shifting of information through the flip-flops of the TTI. The Teletype transmitter requires an input clock frequency

which is the same as the baud frequency of the Teletype unit. This signal controls the shifting of the TTO and thus determines the timing of the 11-unit-code Teletype character it generates. The three Type S202 Dual Flip-Flops at locations MF14 through MF16 produce the TTI CLOCK and TTO CLOCK signals. These six flip-flops form a binary counter which provides frequency division of the output from the Type R405 Crystal Clock module at location ME15. This frequency division method is used since electronic clocks are not reliable at the low frequency required for Teletype operation. The 7.04-kc frequency of the clock is 64 times the baud frequency of the Teletype unit. Division of the clock frequency by 8 (three binary flip-flops) yields the TTI CLOCK signal, which is eight times the baud frequency, and division by 64 (six binary flip-flops) yields the TTO CLOCK signal, which corresponds with the baud frequency.

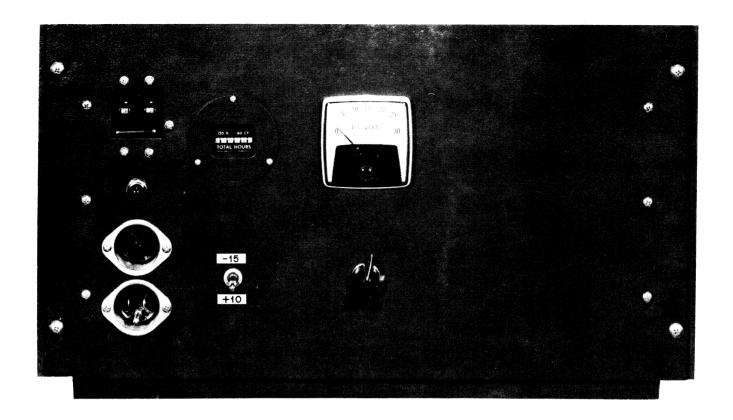

## TYPE 189 ANALOG-TO-DIGITAL CONVERTER (189-0-2)

The Type 189 Converter operates in the conventional successive-approximation manner, using the memory buffer register as a distributor shift register and using the accumulator as the digital buffer register. The converter logic consists of some timing and control circuits, a 12-bit digital-to-analog converter, and a comparator. An ADC instruction, which produces a pause and clears the accumulator, initiates converter operation. The conversion process starts by assuming that the value of the analog input signal is at midscale. A binary 1 is therefore set into the most significant bit of the MB and transfers to accumulator bit ACO. This causes the digital-to-analog converter, whose output is a function of the number contained in the AC, to produce a voltage equal to the center of the converter range (ground to -10v). The output of the D/A converter, representing the first approximation of the input signal, is then compared with the actual analog input signal. If the approximated voltage is greater than the analog signal voltage, the AC bit clears. The binary 1 in bit MBO then shifts one place to the right and transfers into the corresponding bit of the AC. The number in the AC is 4000 if the approximated voltage was less than the analog input signal or is 6000 if the approximated voltage was greater than the analog input during the previous step. The new number in the AC causes the D/A converter to generate a new approximated voltage. If this voltage is still too large, the clear and shift right process repeats, and the binary 1 now appears in bit AC2. The approximated voltage is again compared with the analog input signal. Each successive approximation reduces by one half the difference (error) between the value of the analog input signal and the value of its digital representation in the AC.

The location of the binary 1 in the MB controls the number of approximations made, and hence the accuracy of the conversion. Since the conversion starts when the binary 1 shifts right, one conversion takes place after sensing of the MB bit which discontinues the conversion process. At the conclusion of the conversion, the unsigned binary number in the accumulator is accurate to one half of the digital value

of the least significant bit sensed. At the conclusion of the conversion process the converter produces a RESTART SYNC (1) pulse. This pulse causes the computer program to continue, and the restart process automatically clears the MB.

The Type 189 Analog-to-Digital Converter is completely wired in the standard PDP-8, so that addition of the option requires only the insertion of modules into their connector blocks, installation of an input signal cable terminated with a BNC connector, and presetting of the conversion accuracy. The converter is composed of modules at locations PE5, PE11 through PE16, and PF11 through PF16. The block schematic for the logic circuits is engineering drawing BS-D-189-0-2, and interface connections between the converter and the processor appear in Table 5-2. Note that the input connections to converter terminal PE12J is one of six possible connections to the MB, and the connection used determines the accuracy of the conversion. Table 5-3 indicates the MB terminals which may be used for this connection, and lists other characteristics of the converter which the accuracy connection affects. To save program running time, the converter should be preset to provide only the accuracy required by the program application. Maximum error of the converter is equal to the switching point error plus the quantization error. Maximum quantization error is equal to plus or minus one half of the digital value of the least significant bit.

Table 5-3 also indicates switching point error, total conversion time, and execution time of the IOT instruction which initiates operation of the converter.

TABLE 5-2 ANALOG-TO-DIGITAL CONVERTER INTERFACE WITH PROCESSOR

|         |                  | Processor              |          | Symbol            |                       |

|---------|------------------|------------------------|----------|-------------------|-----------------------|

| Signal  | Logic<br>Element | Engineering<br>Drawing | Terminal | and<br>Direction* | Converter<br>Terminal |

| AC0 (1) | AC               | 2                      | PA7AP    |                   | PF11U                 |

| AC1 (1) | AC               | 2                      | PA8AP    | <del></del>       | PFIIT                 |

| AC2 (1) | AC               | 2                      | PA9AP    | $\longrightarrow$ | PF12U                 |

| AC3 (1) | AC               | 2                      | PA10AP   | $\longrightarrow$ | PF12T                 |

| AC4 (1) | AC               | 2                      | PA11AP   | <del></del>       | PF13U                 |

| AC5 (1) | AC               | 2                      | PA12AP   | <del></del>       | PF13T                 |

| AC6 (1) | AC               | 2                      | PA13AP   | $\longrightarrow$ | PF14U                 |

| AC7 (1) | AC               | 2                      | PA14AP   | <del></del>       | PF14T                 |

| AC8 (1) | AC               | 2                      | PA15AP   | <del></del>       | PF14V                 |

| AC9 (1) | AC               | 2                      | PA16AP   | <del></del>       | PF15U                 |

<sup>\*</sup>Arrows pointing right designate converter input signals; arrows pointing left designate converter output signals.

TABLE 5-2 ANALOG-TO-DIGITAL CONVERTER INTERFACE WITH PROCESSOR (continued)

|               | F                                | rocessor               |                      | Symbol             |                       |

|---------------|----------------------------------|------------------------|----------------------|--------------------|-----------------------|

| Signal        | Logic<br>Element                 | Engineering<br>Drawing | Terminal             | and<br>Direction*  | Converter<br>Terminal |

| AC10 (1)      | AC                               | 2                      | PA17AP               |                    | PF15T                 |

| AC11 (1)      | AC                               | 2                      | PA18AP               | $\longrightarrow$  | PF15V                 |

| IOT 00        | Processor Device IOT<br>Selector | 10                     | PC23T                | <b></b> >          | PE 15R                |

| TI            | Timing                           | 9                      | PB33L                |                    | PA27R                 |

| PROCESSOR IOT | Processor Device IOT<br>Selector | 10                     | РВЗЗТ                |                    | PD34T                 |

| MB9 (1)       | MB                               | 5                      | PC16CD               | <del></del>        | PE 15S                |

| MB9 (1)       | MB                               | 5                      | PC16CF               |                    | PA27S                 |

| A/D CONV      | AC                               | 2                      | PA7BP thru<br>PA18BP | <                  | PE10V                 |

| SHIFT MB      | MB                               | 5                      | PC7DU thru<br>PC18DU | <                  | PE15F                 |

| RESTART SYNC  | Program Sync                     | 10                     | PC32S                | <                  | PE15M                 |

| RUN STOP      | Run Control                      | 9                      | PB33D                | $\longrightarrow$  | PE15L                 |

| IOT 004       | AC Control                       | 3                      | PA26L                | <                  | PE15T                 |

| COMPARATOR    | AC                               | 2                      | PA7BV thru<br>PA18BV | <b>\$</b>          | PD26T                 |

| A/D START (1) | AC                               | 2                      | PA7BU                | <b>\rightarrow</b> | PE 12L                |

| A/D START (1) | MB                               | 5                      | PC7DP                | $\diamond$ —       | PE 12L                |

| A/D START (0) | MB                               | 5                      | PC7DR                | <b>\rightarrow</b> | PE12M                 |

| PAUSE (1)     | Pause Control                    | , 10                   | PC32L                | 4                  | PA27U                 |

<sup>\*</sup>Arrows pointing right designate converter input signals; arrows pointing left designate converter output signals.

An ADC instruction having the code 6004 initiates operation of the converter. The 0's contained in bits MB3 through MB8 of this instruction cause the processor IOT device selector (00) to produce a negative PROCESSOR IOT level at terminal PB33T and a positive IOT 00 pulse at terminal PC23T. In the converter, the PROCESSOR IOT level combines with an MB9 (1) level and a T1 pulse to produce a PAUSE (1) pulse at device selector output terminal PA27U. This pulse sets the PAUSE flip-flop to 1, thereby halting the computer program without initiating operation of the IOP pulse generator. In the converter an IOT 00 pulse triggers DCD input gate RS of module PE15 when the gate is enabled by the ground MB9 (1) level.

The output of the gate triggers the associated pulse amplifier to produce an IOT 004 pulse at terminal PE15T. The IOT 004 pulse performs the following operations:

- 1. In the AC control the IOT 004 pulse causes generation of a —— AC pulse that clears the AC.

- 2. In the converter, the IOT 004 pulse sets the A/D ENABLE flip-flop via the direct-set input, and sets the A/D START flip-flop via the DCD gate input.

TABLE 5-3 ANALOG-TO-DIGITAL CONVERTER TYPE 189 CHARACTERISTICS

| Adjusted<br>Bit<br>Accuracy | Origin of<br>MB Signal<br>of<br>PE12J | Switching<br>Point<br>Error<br>(percent) | Conversion<br>Time per<br>Bit<br>(in µsec) | Total<br>Conversion<br>Time<br>(in µsec) | Instruction<br>Execution<br>Time<br>(in µsec) |

|-----------------------------|---------------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|-----------------------------------------------|

| 6                           | PC12CF                                | ±1.6                                     | 1.0                                        | 6                                        | 7.6                                           |

| 7                           | PC13CF                                | ±0.8                                     | 1.85                                       | 13                                       | 14.6                                          |

| 8                           | PC14CF                                | ±0.4                                     | 2.5                                        | 20                                       | 21.6                                          |

| 9                           | PC15CF                                | ±0.2                                     | 2.7                                        | 24                                       | 25.6                                          |

| 10                          | PC16CF                                | ±0.1                                     | 2.7                                        | 27                                       | 28.6                                          |

| 11                          | PC17CF                                | ±0.05                                    | 4.1                                        | 45                                       | 46.6                                          |

| 12                          | PC18CF                                | ±0.025                                   | 4.6                                        | 55                                       | 56.6                                          |

The A/D ENABLE flip-flop controls the length of time the converter operates. When the ADC instruction is issued, this flip-flop is set to 1 and remains in this state until the 1 in the MB has reached the desired (prewired) conversion bit accuracy. During the next to last conversion the A/D CONV pulse clears the A/D ENABLE flip-flop, thereby disabling the converter at completion of the next conversion.

The ground A/D ENABLE (1) level conditions the DCD input gate of the Type R302 Delay module at PE10. The negative A/D ENABLE (1) level enables the Type R401 Variable Clock module at PE13, which produces 100-nsec pulses to trigger the DCD gate of the delay one-shot. The one-shot gives an A/D CONV output pulse after a delay of 0.5 µsec.

Both the 1 and 0 outputs of the A/D START flip-flop flow to complementary gates of the R123 module at location PC5. The F(1) level from the major state generator enables these gates to produce the ground level MB0 SHIFT ENBL (0) and MB0 SHIFT ENBL (1) levels which set up the DCD gates to shift the 1 through the MB. The DCD gates of the MB for bits 1 through 11, conditioned by the state of the next greater significant bit flip-flop, respond to the SHIFT MB pulse to shift a 1 into the MB for the

first conversion, and to shift it through the MB until the desired accuracy is obtained. This gating of the outputs of the A/D START flip-flop occurs in circuits of the Type R123 module at location PE5 and appears in engineering drawing BS-D-681-0-2.

The binary 1 output of the A/D START flip-flop enables a DCD gate at the set-to-1 input of the most significant bit of the AC. A/D CONV signals trigger this DCD gate. The A/D CONV signal is the positive-aoing level transition produced at terminal PE10V when the one-shot reverts to its stable state.

The delay one-shot reverts to its stable state and produces A/D CONV and MB SHIFT signals; the next converter clock pulse triggers it again. Thus, the one-shot continues to produce A/D CONV and MB SHIFT signals for as long as the A/D ENABLE flip-flop is in the 1 state. (The MB SHIFT pulse generates when the Type 681 Data Line Interface option (see engineering drawing BS-D-681-0-2) triggers pulse amplifier DFHJ of the S603 module at PE15.)

When the MB accuracy control bit becomes a binary 1, the MBn (1) ground level conditions the DCD input gate of the A/D ENABLE flip-flop. The next A/D CONV transition triggers the gate and resets the A/D ENABLE flip-flop to 0, thereby disabling the clock and delay one-shot, and stopping the conversion process. The number stored in the accumulator is the digital equivalent of the analog input signal (within the specified accuracy).

The positive-going level transition, which occurs at terminal PE12E when the A/D ENABLE flip-flop clears, triggers pulse amplifier KIMN of module PE15, provided that a RUN STOP level from the processor run control circuits conditions the DCD gate. The pulse amplifier produces a RESTART SYNC (1) pulse, which sets the RESTART SYNC flip-flop of the pause control to 1. Then the computer program restarts, following the discussion of the run and pause control in Chapter 3 of this manual.

The accumulator, cleared by the IOT 6004 pulse and with a binary 1 set into its most significant bit, contains a binary number which corresponds to one half of its possible maximum value during the first approximation. Each bit of the accumulator supplies the input to a level amplifier of the modules at locations PF11 through PF15. The level amplifiers also receive a -10v potential from the output of the Type A704 -10v Precision Power Supply module at location PE16. Each level amplifier circuit provides an output ground potential when the input signal is at ground level (ACj (1)), and produces a -10v output signal when the input is at -3v (ACj (0)). The outputs from all level amplifiers combine in the digital-to-analog sections of the Type A601 and A604 modules. The analog voltage appearing at terminal PF11K represents the binary number contained in the AC. This voltage is compared with the analog input signal to be measured in the Type A502 Difference Amplifier module at location PE11. The output (at terminal F) of this difference amplifier is -3v if the input from the converter (at terminal P) is more negative than the analog

input signal (at terminal N) being measured. The output of this amplifier is at ground potential if the input from the converter is more positive than the analog input signal. This output is inverted and arrives at the AC as the COMPARATOR signal.

The COMPARATOR signal flows to one input of a 3-input ground-level DCD gate at the 0 input of each AC flip-flop. The corresponding bit of the memory buffer register in the 1 state enables the second input to each DCD gate. When the DCD gate is enabled by both conditions, the A/D CONV pulse triggers it to clear the AC flip-flop. The binary 1 state of the next more significant bit of the memory buffer register enables a corresponding positive DCD gate at the set-to-1 input of each AC flip-flop. The binary 1 state of the A/D START flip-flop of the converter conditions this input to the set-to-1 DCD gate of ACO. These DCD gates trigger at the conclusion of each delay period of the integrating single shot. At this time also, the SHIFT MB signal shifts the contents of the MB one position to the right. This shifting results from a jam-transfer of information from the next more significant bit of the MB (and from the A/D START flip-flop for MBO). This operation transfers a binary 1 into MBO during the first conversion and shifts it to the right for each successive conversion. The MB bit containing a 1 enables the next less significant bit of the accumulator to be set to 1 for the next approximation.

In summary, the IOT 6004 pulse clears the MB and AC; establishes a pause; starts operation of a clock and a one-shot, whose period is determined by the time required to generate and compare an analog signal with the signal to be measured; and sets the A/D START flip-flop which serves as a one-bit extension of the MB. When the one-shot period elapses for the first time, the contents of the MB shift to the right so that all bits contain 0's except the most significant bit, which contains a 1. At this time also, the most significant bit of the AC is set to 1. The contents of the AC then produce an analog signal which is compared with the signal to be measured. If the generated analog signal is more negative (greater amplitude) than the signal being measured, the COMPARATOR signal is at ground level, enabling the DCD gate at the clear input of ACO. When the time period of the one-shot elapses again, ACO clears if the COM-PARATOR signal is at ground potential, and AC1 is set to 1 from the contents of MBO. This operation of setting a 1 into the next least significant AC flip-flop, producing a comparator signal to clear the AC bit, and advancing a binary 1 through MB, continues until the one-shot and clock are disabled by the resetting of the A/D ENABLE flip-flop. This occurs when the binary 1 shifted through the MB reaches a preselected bit. The A/D ENABLE (0) transition causes a pulse amplifier to produce the RESTART SYNC (1) signal, which restores the processor timing signal generator to allow the program to continue and clears the MB. At this time the AC holds an unsigned binary number that corresponds with the value of the analog input signal. This number can be processed under program control.

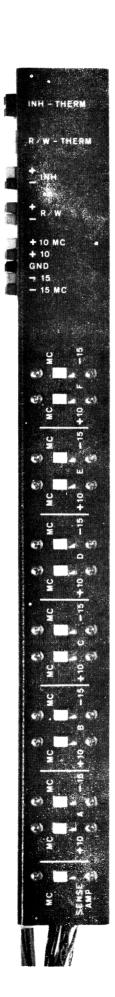

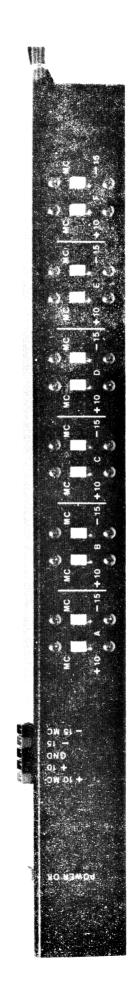

## SPECIAL INPUT/OUTPUT DEVICE MODULES

Because all I/O devices and peripheral equipment connect to a common I/O bus system, each external unit must have a device selector capable of recognizing the device selection code assigned to that unit. In addition, the device selector must be able to accept the three IOP pulses and combine these with the device code to produce IOT pulses for equipment control. Further, since the I/O information lines are common to all equipment, each external unit that transfers information into or out of the accumulator must have suitable gates at the output and input of the data register. The Type W103 Device Selector module and the Type R123 Diode Gate module meet all the requirements of the PDP-8 I/O system and permit connection of a wide variety of devices into the system.

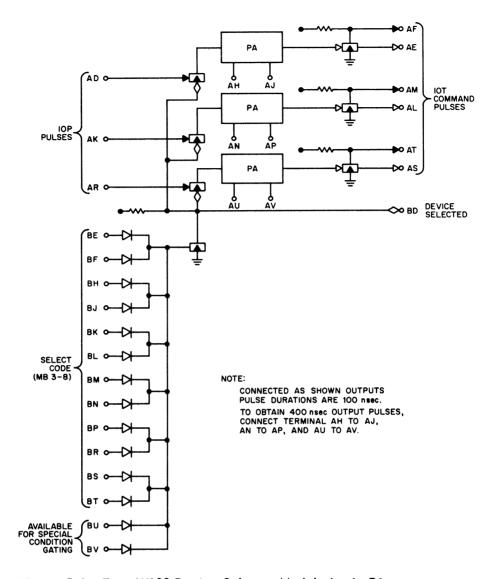

## Type W103 Device Selector

This double-height FLIP CHIP module contains a 14-input diode gate, and additional gates and pulse amplifiers for the production of IOT pulses. Figure 5-1 shows the internal logic of the module.

Negative MB (1) and MB (0) assertion levels corresponding to bits 3 through 8 of the IOT instruction serve as the select code input to the device and are applied to the 14-input NAND gate via input terminals BE through BT. Terminals BU and BV are available for the connection of any other level that governs selection of the device. Input terminals not used should be left unconnected. If the 1 and 0 levels of bits MB3 through MB8 are all permanently wired to the connector block, diodes corresponding to the unasserted levels should be removed from the module.

When all the required levels are present at the input terminals, terminal BD is driven from — 3v to ground. This ground level indicates selection of the device and may be used in the control logic of the device. The ground level appearing at terminal BD also enables three IOP input gates. The IOP 1, IOP 2, and IOP 4 pulses arrive at terminals AP, AK, and AR, respectively. Each of these gates, when conditioned by the device selection level and strobed by an IOP pulse, triggers an associated pulse amplifier. The pulse amplifiers are similar to the Type R601 Pulse Amplifier described in the FLIP CHIP catalog, C-105; for driving capabilities and other characteristics, refer to the catalog. Each pulse amplifier provides both positive and negative IOT output pulses; these may be either 100 nsec or 400 nsec in duration, depending upon the pulse amplifier timing connections.

Figure 5-1 Type W103 Device Selector Module Logic Diagram

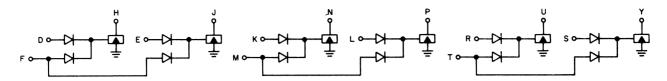

## Type R123 Diode Gate

This standard FLIP CHIP module contains six 2-input negative NAND diode gates. Figure 5-2 shows the internal logic of the module. When used as an I/O device output gate, the conditioning levels from the output of the AC or data register should be applied to terminals D, E, K, L, R, and S; the IOT strobe pulse that opens the gates should be applied to terminals F, M, and T. In this manner, data register flip-flop outputs in the 1 state (-3v) cause the appropriate AC input bus to be driven to ground when a negative IOT pulse triggers the gate. Driving the input bus to ground sets a 1 into the corresponding AC flip-flop. In a similar manner the AC outputs in the 1 state cause the IOT pulse to produce a positive pulse which can be used to set the appropriate flip-flop of the data register.

- NOTES:

1. STROBE PULSE INPUT TO TERMINALS F, M, AND T WHICH ARE CONNECTED IN COMMON WHEN USED AS A BUS GATE

TO TERMINALS D. F. K. L. R. AND S.

- 2. DATA BIT INPUTS TO TERMINALS D, E, K, L, R, AND S

- 3. TWO MODULES ARE REQUIRED TO STROBE A 12-BIT WORD

Figure 5-2 Type R123 Diode Gate Module Logic Diagram

| . ÷ |  |  |

|-----|--|--|

## CHAPTER 6

## INTERFACE

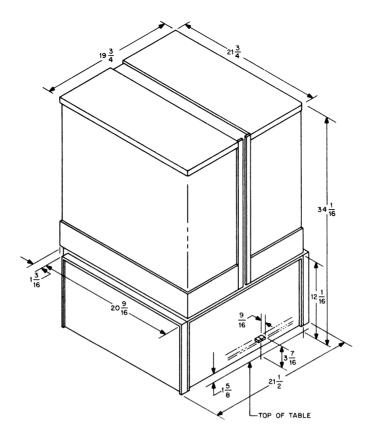

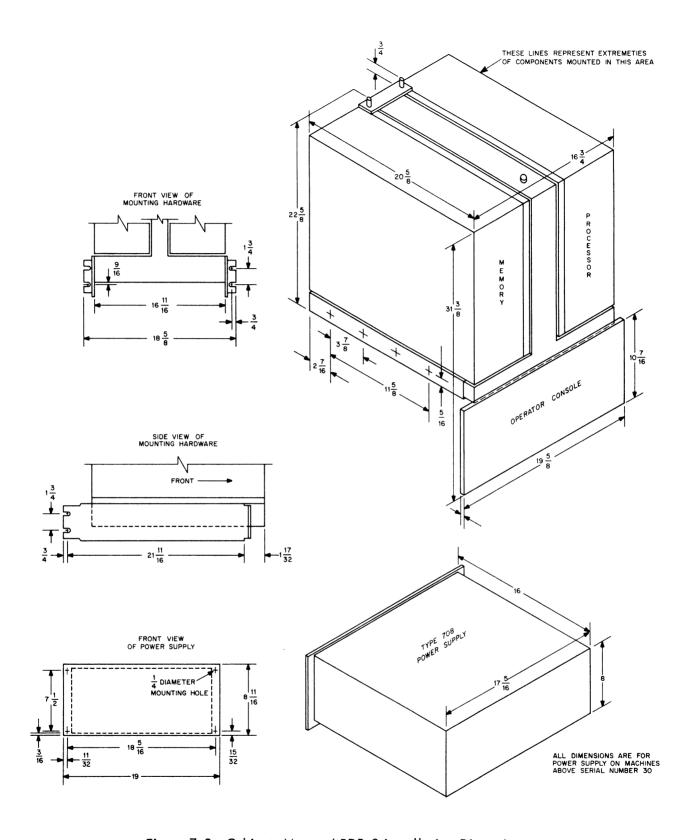

All interface connections to the PDP-8 are made at assigned module receptacle connectors at the back of the memory M or processor P module mounting frame. The module receptacles and assigned use for interface signal connections are:

| Receptacle | Signal Use                                                         |

|------------|--------------------------------------------------------------------|

| PE2        | AC 0-8 inputs                                                      |

| PE3        | Data address 0–8 inputs                                            |

| PE4        | Data bit 0–8 inputs                                                |

| PF2        | AC 9-11, skip, clear AC inputs and run output                      |

| PF3        | Data address 9–11 inputs, and address accepted and B break outputs |

| PF4        | Data bit 9–11 inputs                                               |

| ME30       | Address extend 1, 2, 3 inputs and data field 0–2 outputs           |

| ME34       | BAC 0-8 outputs                                                    |

| ME35       | BMB 0-5 outputs                                                    |

| MF34       | BAC 9–11, IOPs, BT1, BT2A, and power clear outputs                 |

| MF35       | BMB 6-11 outputs                                                   |

Terminals C, F, J, L, N, R, and U of these receptacles are grounded within the computer, and terminals D, E, H, K, M, P, S, T, and V carry signals. These terminals mate with Type W011 Signal Cable Connectors at each end of 93-ohm coaxial ribbon cable.

Interface connections to the PDP-8 for all peripheral equipment can be made with series cable connections between devices. Only one set of cables connects to the computer; two sets of cables connect to each I/O device. One set receives the computer connection from the computer or from the previous I/O device, and one set passes the connection to the next I/O device. Where physical location of equipment does not make series bus connections feasible, or when cable length becomes excessive, place additional interface connectors near the computer (such as just below the operator console in a cabinet configuration system).

All logic signals which pass between the PDP-8 and the I/O equipment are standard DEC levels or standard DEC pulses. Mnemonic names of logic signals indicate the assertion condition of the signal. Standard levels are either ground potential (0.0 to -0.3v) designated by an open diamond ( ), or -3v (-3.0 to -4.0v) designated by a solid diamond ( ). Standard pulses in the positive direction are designated by an open triangle ( ), and negative pulses are designated by a solid triangle ( ). Pulses originating in R and S series modules are positive-going pulses which start at -3v, go to ground for 100 nsec, then return to -3v. Pulses originating in W series modules are always negative, are always referenced to ground, are 2.5v in amplitude (2.3 to 3.0v) with a 2v overshoot, and are of 400-nsec duration. Computer input signals that drive the interface bus to ground (inputs to the AC, CLEAR AC, SKIP, INCREMENT MB, BREAK REQUEST, and INTERRUPT REQUEST) must be connected to the collector of a grounded-emitter transistor, and so can be considered to be transistor-gated negative pulses ( ) or levels ( ).

## LOADING AND DRIVING CONSIDERATIONS

All interface circuits within the PDP-8 consist of series R, S, or W FLIP CHIP modules. When interconnecting these circuits with those in the peripheral equipment, it is important to keep the load on each circuit within its driving ability.

Since a flip-flop consists of two cross-connected diode gates, all input circuits of series R and S modules consist of either a diode gate or a diode-capacitor-diode gate circuit. All inputs draw current from the same direction. Each diode gate input draws 1 ma, and the diode gate output drives a 20-ma load. The internal load resistor draws 2 ma in series R modules, and 5 ma in series S modules. Therefore, a diode gate in an R series module with a clamped load resistor can drive an 18-ma load. The direct set and clear terminals of flip-flops draw 1 ma. The output capability of a series R flip-flop is 20 ma less 2 ma for the load resistor permanently connected in the flip-flop, and 1 ma for conditioning the opposite side of the flip-flop. The flip-flop can drive a 17-ma external load.

The DCD gates on flip-flops and pulse amplifiers draw 2 ma at level inputs and 3 ma at pulse inputs. When two DCD gates drive both sides of the same flip-flop, the load on both pulse inputs totals only 4 ma. When the level inputs are connected together as in a complement configuration, the total input load is only 3 ma.

Capacitive loading adversely affects the performance of series R and S modules; therefore, where long lines are being driven, extra clamped loads should be added to sufficiently discharge the cable capacitance. As a general rule, an extra 2 ma of clamped load current should be added for every foot of wire beyond 1-1/2 feet. An exception to this rule is the R650 Bus Driver module. This module can drive

coaxial cable of 100-ohm characteristic impedance through a series driving resistor. If coaxial cable is not used, use the direct output provided that the lines are short. If reflections occur on the line, adjust the resistive output of the bus driver to correct the problem. Shunt termination on the far end of the transmission line is not advisable.

The Type R650 Bus Driver module has two types of outputs: the fast and the slow (or ramp) output. Using the fast output, the bus driver operates merely as a fast amplifier. When the ramp output is used, an integrating capacitor inserted between the input of the bus driver and the output stage causes the output lines to move from ground to – 3v, or in the reverse direction, in approximately 500 nsec. This connection, used on the AC lines, helps to reduce cross-talk. All other Type R650 Bus Driver module outputs are fast.

Terminate the Type W640 Pulse Amplifier modules carefully. If the output of these modules generates sufficient noise, regeneration may result. For this reason, output lines of Type W640 Pulse Amplifier modules should be well shielded. The outputs of these modules are either 400 nsec or 1 µsec in width. All connections on the standard PDP-8 use the 400-nsec pulse width.

Input circuits to the PDP-8 consist, in many cases, of a 10-ma clamped load and a direct input to a flip-flop or pulse amplifier. The input load is 10 ma for the clamped load and 1 ma for the flip-flop or the pulse amplifier. Give careful consideration to capacitive loads on the input lines, since the input lines must be at -3v before the pulse amplifier or flip-flop begins its next machine cycle.

The machine itself usually determines timing. However, the following timing considerations apply to the modules. The Type S111 Diode Gate sets up in approximately 50 nsec in either direction under normal load conditions. Fall times are faster with heavier loads, and the best method to speed up a slow diode gate is to connect an external load across the input to ground. The DCD gates set up in 400 nsec, as measured from the end of the preceding 100-nsec pulse, and both the level and pulse inputs must return to —3v for 400 nsec before the next pulse is applied. Series R and S pulses are 100 nsec in width, measured from the 10-percent point of the leading edge to the 90-percent point of the trailing edge. Fall time is not critical on these pulses, provided that the pulse has returned to —3v in time to come up for the next pulse.

#### PROGRAMMED TRANSFER INTERFACE

Tables 6-1 and 6-2 summarize input and output interface signal connections for use in programmed operations.

TABLE 6-1 PROGRAMMED TRANSFER INPUT INTERFACE

|          |                        |                         |                    | Signal Destination | itination        |                    |

|----------|------------------------|-------------------------|--------------------|--------------------|------------------|--------------------|

| Signal   | Symbol                 | Interface<br>Connection | Module<br>Terminal | Module<br>Type     | Logic<br>Element | Block<br>Schematic |

| AC 0     |                        | PE2D                    | PA7, PB7<br>AE     | R210               | AC               | BS-D-8P-0-2        |

| AC 1     | ` <u></u>              | PE2E                    | PA8, PB8<br>AE     | R210               | AC               | BS-D-8P-0-2        |

| AC 2     | - <del> </del>         | PE2H                    | PA9, PB9<br>AE     | R210               | AC               | BS-D-8P-0-2        |

| AC 3     |                        | PE2K                    | PAIO, PBIO<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 4     |                        | PE2M                    | PAII, PBII<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 5     |                        | PE2P                    | PA12, PB12<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 6     |                        | PE2S                    | PA13, PB13<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 7     | - <del>[4]</del> III   | PE2T                    | PA14, PB14<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 8     |                        | PE2V                    | PA15, PB15<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 9     |                        | PF2D                    | PA16, PB16<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 10    | - <del>[4]</del>   , [ | PF2E                    | PA17, PB17<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| AC 11    |                        | РҒ2Н                    | PAI8, PBI8<br>AE   | R210               | AC               | BS-D-8P-0-2        |

| CLEAR AC | \<br>- <del> </del>    | PF2P                    | PA19J              | 5603               | AC Control       | BS-D-8P-0-3        |

|          |                        |                         |                    |                    |                  |                    |

TABLE 6-1 PROGRAMMED TRANSFER INPUT INTERFACE (continued)

|                      |        |                         |                    | Signal Destination | tination                 |                    |

|----------------------|--------|-------------------------|--------------------|--------------------|--------------------------|--------------------|

| Signal               | Symbol | Interface<br>Connection | Module<br>Terminal | Module<br>Type     | Logic<br>Element         | Block<br>Schematic |

| INTERRUPT<br>REQUEST |        | PF2M                    | PD36K              | SIII               | Program<br>Interrupt     | BS-D-8P-0-10       |

| SKIP                 |        | PF2K                    | PB21V              | 2603               | Sync.<br>Skip<br>Control | BS-D-8P-0-10       |

TABLE 6-2 PROGRAMMED TRANSFER OUTPUT INTERFACE

|            |            |                         |                    | Signal Origin  | Origin           |                    |

|------------|------------|-------------------------|--------------------|----------------|------------------|--------------------|

| Signal     | Symbol     | Interface<br>Connection | Module<br>Terminal | Module<br>Type | Logic<br>Element | Block<br>Schematic |

| BAC 0 (1)  | <b>\</b>   | ME34D                   | ME26J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 1 (1)  | $\Diamond$ | ME34E                   | ME26T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 2 (1)  | $\Diamond$ | ME34H                   | ME27J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 3 (1)  | $\Diamond$ | ME34K                   | ME27T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 4 (1)  | Ŷ          | ME34M                   | ME28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 5 (1)  | Ŷ          | ME34P                   | ME28T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 6 (1)  | Ŷ          | ME34S                   | MF26J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 7 (1)  | $\Diamond$ | ME34T                   | MF26T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 8 (1)  | Ŷ          | ME34V                   | MF27J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 9 (1)  | $\Diamond$ | MF34D                   | MF27T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BAC 10 (1) | $\Diamond$ | MF34E                   | MF28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

|            |            |                         |                    |                |                  |                    |

TABLE 6-2 PROGRAMMED TRANSFER OUTPUT INTERFACE (continued)

|            |            |                         |                    | Signal Origin  | Origin           |                    |

|------------|------------|-------------------------|--------------------|----------------|------------------|--------------------|

| Signal     | Symbol     | Interface<br>Connection | Module<br>Terminal | Module<br>Type | Logic<br>Element | Block<br>Schematic |

| BAC 11 (1) | <b>\</b>   | MF34H                   | MF28T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 3 (0)  | Ŷ          | ME35K                   | MC27T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 3 (1)  | Ŷ          | ME35M                   | MC28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 4 (0)  | $\Diamond$ | ME35P                   | MC28T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 4 (1)  | Ŷ          | ME35S                   | MC29J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 5 (0)  | $\Diamond$ | ME35T                   | MC29T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 5 (1)  | Ŷ          | ME35V                   | MD25J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 6 (0)  | $\Diamond$ | MF35D                   | MD25T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 6 (1)  | Ŷ          | MF35E                   | MD26J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 7 (0)  | Ŷ          | MF35H                   | MD26T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 7 (1)  | Ŷ          | MF35K                   | MD27J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 8 (0)  | $\Diamond$ | MF35M                   | MD27T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 8 (1)  | $\Diamond$ | MF35P                   | MD28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| 10P 1      | <b>†</b>   | MF34K                   | МС31Н              | W640           | I/O Buffers      | BS-D-8M-0-16       |

| 10P 2      | <b>†</b>   | MF34M                   | MC31N              | W640           | I/O Buffers      | BS-D-8M-0-16       |

| 10P 4      | †<br>†     | MF34P                   | MC31U              | W640           | I/O Buffers      | BS-D-8M-0-16       |

|            |            |                         |                    |                |                  |                    |

## Accumulator Data Input (2)

The AC input receives data transferred from an I/O device to the PDP-8. For a data transfer from an I/O device, the CLEAR AC signal first clears the AC flip-flops; then the input signals from the I/O device arrive directly at the set input of the AC flip-flops. A positive pulse that drives any input line to ground sets a binary 1 into the associated AC flip-flop. Each AC input presents a 10-ma clamped load and a 1-ma direct input to the flip-flop.

# Clear AC Input (3)

An interface connection to the PDP-8 allows a programmed I/O device to clear the AC. In this way an external device supplying information to the computer ensures that the word being read into the AC is not transferred in over an existing word. Transferring a word into the AC without first clearing the AC results in the inclusive OR of the new word, with the previous word being held in the AC after the transfer. The CLEAR AC signal initiates operation of the Type S603 Pulse Amplifier module at location PA19 by driving the input terminal to ground. The pulse amplifier may be triggered by a standard DEC positive pulse of 100-nsec duration or by a positive-going transition with a rise time of less than 60 nsec supplied to this input. This connection presents a clamped 10-ma load and a 1-ma diode load to the pulse source.

## Program Interrupt Request Input (10)

Signals from I/O devices which interrupt the program in progress are connected to a bus in the PDP-8. Connections to this bus must be static levels: ground level to interrupt; — 3v for no effect. The INTER-RUPT REQUEST signal is clamped at — 3v by a 10-ma clamped load in the W005 Clamped Load module at location PE9. The S111 Diode Gate module at location PD36 inverts and isolates the signal which then arrives as one input to the S111 Diode Gate module at location PC35 to initiate the internal interrupt gate. The INTERRUPT REQUEST signal source must be capable of driving a 10-ma clamped load plus the 1-ma input load of the diode gate module.

# Input/Output Skip Input Connection (10)

A skip bus is available for input connections to the PDP-8 from gated SKIP pulses generated in I/O equipment. A flag or device status level which is strobed or sampled by an IOT pulse usually produces input SKIP pulses. The IOT pulse from the device selector strobes the flag; and, if it is in the preselected binary condition, the instruction following the IOT is skipped.

The input SKIP pulses drive one input of the Type S603 Pulse Amplifier module at location PB21 to ground. The pulse source must be capable of driving a 10-ma clamped load and the 3-ma load represented by the pulse input of the pulse amplifier.

# Buffered AC Data Output (16)

Data contained in the AC as static levels supplies information to I/O devices. These static levels can be strobed into an I/O device register by IOT pulses from the associated device selector. The static level of each buffered AC output signal is at – 3v when the bit contains a binary 0 and at ground potential when that bit contains a binary 1.

The BAC signals arrive at the interface connections through Type R650 Bus Driver modules at locations ME26 through ME28 and MF26 through MF28. To avoid the possibility of ringing on long interface lines, the bus driver connections provide a total transition time of 800 nsec for output rise and 700 nsec for output fall. The bus drivers for bits 0 through 3 can drive a 20-ma load; the bus drivers for bits 4 through 11 also drive the teleprinter, thereby reducing the external driving capability to 18 ma.

## Buffered MB Select Code Output (16)

Bits 3 through 8 of an IOT instruction held in the MB select the I/O device addressed by the instruction. Complementary output signals from flip-flops MB3-8 supply the input to each device selector in the external I/O device through Type R650 Bus Driver modules at locations MC25 through MC29 and MD25 through MD29. The binary 1 outputs also serve as data word outputs during a data break. Each BMB signal at ground potential can drive a 20-ma load.

#### IOP Generator Output (16)

The IOP 1, IOP 2, and IOP 4 pulses trigger pulse amplifiers in the addressed peripheral equipment device selector. When triggered, the pulse amplifiers produce IOT pulses which perform control functions in the peripheral equipment or in the processor. Type W640 Pulse Amplifier modules at location MC31 standardize the IOP pulses prior to application to the interface connections. Each pulse output can drive a 10-ma load.

#### DATA BREAK INTERFACE

Tables 6-3 and 6-4 summarize the input and output interface connections used in data break transfers.

TABLE 6-3 DATA BREAK INPUT INTERFACE

|                  |                |                         |                    | Signal Destination | tination         |                    |

|------------------|----------------|-------------------------|--------------------|--------------------|------------------|--------------------|

| Signal           | Symbol         | Interface<br>Connection | Module<br>Terminal | Module<br>Type     | Logic<br>Element | Block<br>Schematic |

| DATA ADDR 0 (1)  | $  \diamond  $ | PE3D                    | PC7, PD7<br>CR     | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 1 (1)  | $\Diamond$     | PE3E                    | PC8, PD8<br>CR     | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 2 (1)  | $\Diamond$     | РЕЗН                    | PC9, PD9<br>CR     | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 3 (1)  | $\Diamond$     | PE3K                    | PC10, PD10<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 4 (1)  | $\Diamond$     | PE3M                    | PCII, PDII<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 5 (1)  | $\Diamond$     | PE3P                    | PC12, PD12<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 6 (1)  | $\Diamond$     | PE3S                    | PC13, PD13<br>CR   | R211               | W                | BS-D-8P-0-4        |

| DATA ADDR 7 (1)  | $\Diamond$     | PE3T                    | PC14, PD14<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 8 (1)  | $\Diamond$     | PE3V                    | PC15, PD15<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 9 (1)  | $\Diamond$     | PF3D                    | PC16, PD16<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 10 (1) | $\Diamond$     | PF3E                    | PC17, PD17<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA ADDR 11 (1) | $\Diamond$     | РЕЗН                    | PC18, PD18<br>CR   | R211               | WA               | BS-D-8P-0-4        |

| DATA BIT 0 (1)   | Ŷ              | PE4D                    | PC7, PD7<br>DM     | R211               | MB               | BS-D-8P-0-5        |

|                  |                |                         |                    |                    |                  |                    |

TABLE 6-3 DATA BREAK INPUT INTERFACE (continued)

|                    |                |                         |                    | Signal Destination | tination            |                    |

|--------------------|----------------|-------------------------|--------------------|--------------------|---------------------|--------------------|

|                    |                | <b>.</b>                |                    |                    |                     |                    |

| Signal             | Symbol         | Interface<br>Connection | Module<br>Terminal | Module<br>Type     | Logic<br>Element    | Block<br>Schematic |

| DATA BIT 1 (1)     | $  \uparrow  $ | PE 4E                   | PC8, PD8<br>DM     | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 2 (1)     | $\Diamond$     | PE4H                    | PC9, PD9<br>DM     | R211               | WB                  | BS-D-8P-0-5        |

| DATA BIT 3 (1)     | $\Diamond$     | PE4K                    | PC10, PD10<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 4 (1)     | $\Diamond$     | PE4M                    | PC11, PD11<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 5 (1)     | $\Diamond$     | PE4P                    | PC12, PD12<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 6 (1)     | $\Diamond$     | PE4S                    | PC13, PD13<br>DM   | R211               | WB                  | BS-D-8P-0-5        |

| DATA BIT 7 (1)     | Ŷ              | PE4T                    | PC14, PD14<br>DM   | R211               | WB                  | BS-D-8P-0-5        |

| DATA BIT 8 (1)     | $\Diamond$     | PE4V                    | PC15, PD15<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 9 (1)     | $\Diamond$     | PF4D                    | PC16, PD16<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 10 (1)    | $\Diamond$     | PF4E                    | PC17, PD17<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| DATA BIT 11 (1)    | <b>\</b>       | РҒ4Н                    | PC18, PD18<br>DM   | R211               | MB                  | BS-D-8P-0-5        |

| BREAK REQUEST      | }<br>          | PF3K                    | PC32J              | 8203               | Major State<br>Gen. | BS-D-8P-0-6        |

| TRANSFER DIRECTION | *              | PF3M                    | PD23E              | SIII               | MB Control          | BS-D-8P-0-5        |

|                    |                |                         | -                  |                    |                     |                    |

\*Direction is into PDP-8 when signal is - 3v, out of PDP-8 when ground potential.

TABLE 6-3 DATA BREAK INPUT INTERFACE (continued)

|                |                                        |                         |                    | Signal De      | Signal Destination  |                    |

|----------------|----------------------------------------|-------------------------|--------------------|----------------|---------------------|--------------------|

| Signal         | Symbol                                 | Interface<br>Connection | Module<br>Terminal | Module<br>Type | Logic<br>Element    | Block<br>Schematic |

| INCREMENT MB   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | PF3T                    | PD31 M             | \$107          | MB Control          | BS-D-8P-0-5        |

| CYCLE SELECT   | 11 🔷                                   | PF4K                    | PE7S               | S10 <i>7</i>   | Major State<br>Gen. | BS-D-8P-0-6        |

| INCREMENT CA** | <b>†</b>                               | PF4M                    | PE I OF            | R121           | MB Control          | BS-D-9P-0-5        |

<sup>\*\*</sup>This signal must not be - 3v unless PDP-8 is in break state.

TABLE 6-4 DATA BREAK OUTPUT INTERFACE

|           |                |                         |                    | Signal         | Signal Origin    |                    |

|-----------|----------------|-------------------------|--------------------|----------------|------------------|--------------------|

| Signal    | Symbol         | Interface<br>Connection | Module<br>Terminal | Module<br>Type | Logic<br>Element | Block<br>Schematic |

| BMB 0 (1) | $  \uparrow  $ | ME35D                   | MC26J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 1 (1) | $\Diamond$     | ME35E                   | MC26T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 2 (1) | $\Diamond$     | ME35 H                  | MC27J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 3 (1) | $\Diamond$     | ME35 M                  | MC28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 4 (1) | Ŷ              | ME35S                   | MC29J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 5 (1) | $\Diamond$     | ME35V                   | MD25J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 6 (1) | $\Diamond$     | MF35E                   | MD26J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 7 (1) | $\Diamond$     | MF35K                   | MD27J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 8 (1) | Ŷ              | MF35P                   | MD28J              | R650           | I/O Buffers      | BS-D-8M-0-16       |

| BMB 9 (1) | $\Diamond$     | MF35S                   | MD28T              | R650           | I/O Buffers      | BS-D-8M-0-16       |

TABLE 6-4 DATA BREAK OUTPUT INTERFACE (continued)

|                     |            |                         |                    | Signal Origin  | Origin              |                    |

|---------------------|------------|-------------------------|--------------------|----------------|---------------------|--------------------|

| Signal              | Symbol     | Interface<br>Connection | Module<br>Terminal | Module<br>Type | Logic<br>Element    | Block<br>Schematic |

| BMB 10 (1)          | Ŷ          | MF35T                   | MD29J              | R650           | I/O Buffers         | BS-D-8M-0-16       |

| BMB 11 (1)          | $\Diamond$ | MF35V                   | MD29T              | R650           | I/O Buffers         | BS-D-8M-0-16       |

| B BREAK             | <b>†</b>   | PF3P                    | PE8T               | R650           | Major State<br>Gen. | BS-D-8P-0-10       |

| ADDRESS<br>ACCEPTED | Î          | PF3S                    | PF10H              | W640           | MA Control          | BS-D-8P-0-10       |

| WC OVERFLOW         | <b>†</b>   | PF4P                    | PF10N              | W640           | MB Control          | BS-D-8P-0-10       |

#### Data Address Inputs (4)

Address signals arrive at the MA during a data break to designate the core memory address of the transfer. These DATA ADDR signals condition a pair of DCD gates at the input of each MA flip-flop and are at ground potential to signify a binary 1. A DATA ADDR signal travels directly to the gate at the 1 input and through an inverter to the gate at the 0 input, thereby providing a jam transfer. The DATA ADDR signals must arrive during T2 of the cycle preceding the data break cycle. To assure proper timing, these signals should occur concurrently with the BREAK REQUEST signal. Each DATA ADDR signal connection presents a 3-ma (maximum) load to the signal source in the I/O device.

## Data Bit Inputs (5)

Input connections to the MB are also made through the interface connections. These connections are made to the DATA BIT level input of a DCD gate in each module of the MB. Data supplied to the MB inputs must be at ground level to specify a binary 1, or must be – 3v for a binary 0. The DATA — MB pulse strobes this data into the MB flip-flops, as described in connection with the TRANSFER DIRECTION signal description. Each DATA BIT signal input represents a 2-ma load to the signal source.

## Data Break Request Input Signal (6)

The break state is entered to transfer information between a peripheral device and the core memory via the MB. This state is entered only after the external device supplies a ground-level BREAK REQUEST signal to the computer. The signal is applied to one input of a DCD gate in the S203 Triple Flip-Flop module at location PC32. The second input to this gate is the T1 pulse that strobes the BREAK REQUEST signal into a synchronizing flip-flop. This flip-flop is sampled and cleared during T2 of each cycle. The BREAK REQUEST signal interface input must drive a 10-ma clamped load to the level input of a DCD gate, which represents a 2-ma load at ground.

#### Transfer Direction Input Signal (5)

A TRANSFER DIRECTION signal must arrive at the computer during time state T2 of the cycle preceding a break state, to determine the read or write status of the memory for the data break. At ground potential this signal specifies a transfer from the core memory to the I/O device; at – 3v the signal specifies a transfer into core memory from the external device. This signal must be at ground potential before T2 of the preceding cycle or no MEMORY STROBE pulse occurs, and data cannot transfer out of core memory. If the signal is at – 3v, the DATA

MB pulse occurs during T1 of the break state, and the data arriving at the MB inputs is strobed into the MB flip-flops. One input of a 2-input NAND gate in the Type S111 Diode Gate module at location PD23 receives the TRANSFER DIRECTION signal. The BREAK

signal supplies the second input to the gate so that the TRANSFER DIRECTION signal has effect only when the computer is in the break state. The input represents a 1-ma load to the TRANSFER DIRECTION signal source.

## Increment MB Input Signal (5)

An INCREMENT MB signal input to the PDP-8 allows the contents of device-specified core memory location to increment by 1 during a data break. This input requires a ground level signal that is gated to occur only when the B BREAK signal is present. The Type \$107 Inverter module at location PD31 receives this signal. Connection to this point presents a 1-ma load on the driving source of the INCREMENT MB signal.

# Cycle Select Input Signal (6)

A device requesting a data break must supply a CYCLE SELECT signal to specify that a single-cycle or a 3-cycle break is needed. An S107 module that exhibits a load of 1 ma at ground and no load at -3v receives this signal. When this signal is at ground potential, a 3-cycle break is requested; when it is at -3v, a 1-cycle break is requested.

## Increment CA Input Signal (5)

During the current address (CA) cycle of a 3-cycle data break the address of the transfer can be incremented by 1 so that data break transfers occur at successive core memory locations. The INCREMENT CA signal which arrives from the requesting device determines incrementation of the address during the CA state. If the signal is at – 3v the address increments; if it is at ground the address does not increment. This signal must occur at the beginning of the CA state (T2 time), arriving at a gate of a Type R121 module whose ground-level output enables a DCD gate that is triggered by a T1 pulse. When triggered, this gate causes the COUNT MB pulse to advance the address contained in the MB. At ground potential the INCREMENT CA signal source receives 1 ma of load and at – 3v it receives no load.

#### Buffered MB Data Output (16)

Type R650 Bus Driver modules isolate and power amplify the binary 1 output of each MB flip-flop. During a data break in which the transfer direction is out of the computer, words transfer from core memory to the I/O device via these bus drivers. These bus driver outputs for bits MB3-8 arrive at the device selectors for programmed data transfers. Each BMB output signal is at ground potential to signify a 1, and is capable of driving a 20-ma load.

#### Buffered Break State Output Signal (10)

When in the break state, the computer supplies a negative signal level to external devices. This – 3v signal is often logically combined with a timing pulse to initiate operations in an I/O device. This signal level arrives at the interface connections through the Type R650 Bus Driver module at location PE8. The bus driver output is capable of driving a 20-ma load.

## Address Accepted Output (10)

During time state T2 of each break state cycle, the PDP-8 produces a standard DEC 400-nsec positive pulse when the externally supplied address is strobed into the MA. The W640 Pulse Amplifier module at location PF10 produces this ADDRESS ACCEPTED pulse, which can drive a 10-ma load.

## WC Overflow Output Pulse (10)

During the word count (WC) cycle of a 3-cycle data break, the word count reads into the MB from core memory, increments by 1, and is rewritten in memory. Incrementation of the word count causes MBO to change from the 1 to the 0 state, generating the WC OVERFLOW pulse and transmitting it to the device using the data break. Usually the word count is preset to a negative number that is one less than the desired number of data break transfers. In this manner the WC OVERFLOW pulse indicates to the device that the current break will complete the desired number of transfers.

The WC OVERFLOW pulse is a standard DEC negative 400-µsec pulse produced by a Type W640 module. The pulse occurs approximately 80 µsec after memory strobe and can drive a 10-ma load.

#### MISCELLANEOUS INTERFACE

The PDP-8 interface has available several input and output signal connections which are not required for either programmed or data break transfers, but which peripheral equipment can use with either transfer mode. These connections are summarized in Tables 6-5 and 6-6.

## Analog Input Signal

The Type 189 Analog-to-Digital Converter option receives an analog input signal between 0 and -10v. A BNC connector mounted on the outside of the processor fan housing at the back of the computer provides connection for this signal. Internal wiring cables this connector to the input of a Type A502 Comparator module. This module compares the analog input signal with a 0 to -10v analog signal which Type A601 and A604 Digital-Analog Converter modules produce. The input draws up to 1 µa depending on the relative polarity of the two voltage inputs of the A502 module. The maximum current difference between positive and negative input voltages is 1 µa. The difference input capacitance is 75 pf.

TABLE 6-5 MISCELLANEOUS INPUT INTERFACE

| Signal Destination | Module Logic Block Type Element Schematic | 2 A-D Conv BS-D-189-0-2 | S107, R123 DLI BS-D-681-0-2 | S107, S151 Mem Ext BS-D-183-0-3<br>Cont | S107, S151 Mem Ext BS-D-183-0-3<br>Cont | S107, S151 Mem Ext BS-D-183-0-3<br>Cont |

|--------------------|-------------------------------------------|-------------------------|-----------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

|                    | Module Me<br>Terminal T                   | PE11N A502              | PE6K, PE5L S107             | ME8K, MC3K S107                         | ME8H, MC3E S107                         | ME8E, MC3J S107                         |