# IDENTIFICATION

Product Code:

MAINDEC-81-D6AB-D

Product Name:

AX08 Diagnostic

Date Created:

October 8, 1968

Maintainer:

Diagnostic Group

Author(s):

J. Kelly J. Hittell

#### ABSTRACT

This unit is tested in three sections: (a) an instruction test of the logic; (b) a display test for the scope; (c) a calibration section for the A/D Converter.

### 2. REQUIREMENTS

#### 2.1 Equipment

PDP-8, 8L or 8I Standard Computer

AX08 option

Adjustable Voltage Source (0.01% or better, Z out < 1.0 ohm)

#### 2.2 Storage

2.2.1 Program Storage - The routine uses memory from address 0 to 4500.

### 3. LOADING PROCEDURE

#### 3.1 Methods

Procedure for normal binary tape is followed.

## 4. STARTING PROCEDURE

For normal starting operation all switches should be down. Starting address is 200.

# 4.1 Program and/or Operator Action

Connect non-zero voltage source to input connector for channel zero.

Set "Timing Control" minimum (C.C.W.)

Load the program into memory.

Set switch register to starting address - SA = 0200

Load Address.

Press Start.

4.1.1 The program will loop in the first section of the test, and the display, if on, will read

"DIAGNOSTIC RUNNING"

"SAME VALUE IN XX ICMX"

1

If there is an error, the teleprinter will print out the error and continue on in section test. (XX = the multiplexer channel + 1 where overflow occurs)

### 5. OPERATING PROCEDURE

### 5.1 Operational Switch Settings

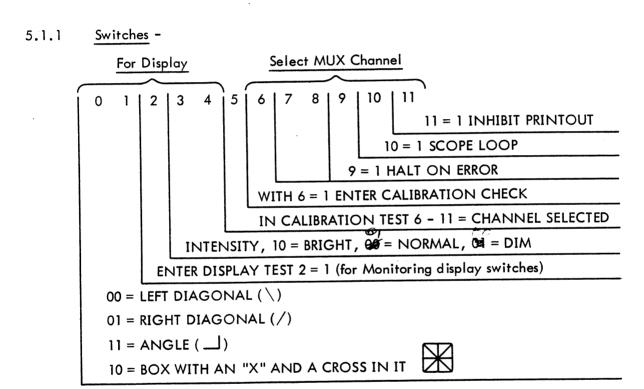

With all switches down (Logical zero), the test will stay in the instruction section. With switch 2 up the test will enter the display section, from the instruction section. With switch 6 up the test will enter the A/D calibration section, from the display section.

## 5.2 Subroutine Abstract

- 5.2.1 <u>BEGIN</u> This is AX08 instruction test of the logic which tests that all registers and flip-flops initiated by start key are in the correct state. Also tested is the ability to set and clear the (Y) register, the skip on flag and interrupt logic for—the A/D timing, the RC clock and the crystal clock. Other logic functions of the display and the A/D converter are also tested.

- 5.2.2 <u>CHTST</u> This is an increment test of multiplexer and assumes that (1) the display is operating; (2) the A/D is calibrated; (3) the <u>channel zero</u> of the multiplexer has a <u>non-zero voltage</u> applied to it,

and that all other channels have no voltage applied to them. This routine records the voltage it sees on channel zero, counts increments of the multiplexer until the same voltage (+/-1/2 LSB) is found again. Then uses the display for the message "SAME VALUE IN XX ICMX" (ICMX is the increment instruction).

- 5.2.3 <u>Display</u> There are four basic patterns which can be displayed: (1) a right diagonal from the lower left corner to the upper right; (2) a left diagnoal from the upper left corner to the lower right corner; (3) an angle from the middle to the left edge of the screen to the center then to the top; (4) a box with an "X" and a cross in it. These tests are designed to show inverted bit transfers from accumulator to the deflection registers, malfunctions in the deflection logic and deflection amplifier faults.

- 5.2.4 INIT3 This routine is the A/D Converter calibration check. Bits 6-11 of the switch register selects the multiplexer channel, then 1000 octal conversions are made on this channel and stored in a buffer. The first word of the buffer, which is the binary value of the analog voltage is displayed in the upper left of the scope. A horizontal line is now drawn on the scope. A deviation in the amplitude of the horizontal sweep from its point of origin represents a change in the A/D Converter output for a fixed voltage in. A voltage at the converter switching point will give two levels in the horizontal sweep. A noisy converter, or voltage source may give a staircase pattern which indicates excessive noise in the system. The refresh rate of the sweep is controlled by the RC (timing control) clock adjustment on the front panel.

- 5.2.5 SCOPE This subroutine call, is placed between each subtest in the instruction section and records the starting address of each subtest as it is being entered. If a scope loop is requested, it will jump to the start of the subtest that the scope loop is requested for.

- 5.2.6 <u>HALT</u> This routine printouts an address that tags the failing subtest and the contents of the AC at the time of the failure.

# 5.3 Program and/or Operator Action

Loading and starting at 200 with all switches down is the start of the IOT instruction test. If an error is detected here, there will be a printout in this section. When an error is detected, and it is necessary to scope on it, place SW9 UP to halt on error, then SW10 UP to loop on it, then SW11 to DELETE printouts.

When errors in the instruction section have been corrected SW2 UP will advance the program to the display test.